一种FPGA逻辑重加载电路的制作方法

一种fpga逻辑重加载电路

技术领域:

[0001]

本发明涉及但不限于计算机硬件技术领域,尤指电路系统中一种fpga逻辑重加载电路。

背景技术:

:

[0002]

现代航空电子产品设计中,fpga被广泛用于各类嵌入式系统及模块的开发与设计。由于航电系统对于电子模块的启动有着严格的可靠性要求,传统的基于fpga设计的电子模块多采用1片flash为fpga芯片提供逻辑存储及加载功能,当flash芯片失效、flash芯片管脚脱焊/桥连或在逻辑升级加载过程中出现异常下电等情况时,均会导致fpga无法正常加载完成从而出现电子模块“变砖”无法工作的情况。

技术实现要素:

:

[0003]

本发明的目的是:本发明实施例提供一种fpga逻辑重加载电路,以解决传统fpga逻辑存储及加载电路,可能由于flash芯片故障或升级加载异常中断,而导致整个电路无法正常完成加载操作的问题。

[0004]

本发明的技术解决方案是:本发明实施例提供一种fpga逻辑重加载电路,包括:至少2片flash,1片可编程逻辑电路,所述至少2片flash挂接在可编程逻辑电路上互为备份;

[0005]

其中,所述至少2片flash芯片的时钟信号clk、数据信号、地址信号、控制信号通过复用的连接方式连接到fpga,fpga输出的片选信号cs在flash与fpga之间通过可编程逻辑电路进行耦合;所述fpga逻辑重加载电路具有3种应用模式:逻辑加载模式、逻辑在线升级模式、逻辑离线升级模式;

[0006]

所述fpga逻辑重加载电路,用于通过所述可编程逻辑电路控制2片flash的加载过程,从而通过可编程逻辑电路中的控制逻辑在逻辑加载模式下控制fpga逻辑加载状态判断和重加载功能,以及在逻辑在线升级模式下实现在线状态下对指定flash的逻辑升级功能,在逻辑离线升级模式下实现离线状态下对指定flash的逻辑升级功能。

[0007]

可选地,如上所述的fpga逻辑重加载电路中,

[0008]

所述fpga逻辑重加载电路中,fpga的逻辑加载信号rogram_b和fpga逻辑加载完成信号done均连接至可编程逻辑电路;

[0009]

所述可编程逻辑电路的输入信号包括:由fpga输入的片选信号cs、在线升级使能信号en_online_upgrade、在线升级flash选择信号sel_online_flash、所述done和启动加载信号init_b,以及由外部驱动输入的离线升级使能信号en_offline_upgrade、离线升级flash选择信号sel_offline_flash、时间设定信号timeset1和timeset2;

[0010]

所述可编程逻辑电路的输出信号包括:输出到fpga的逻辑加载信号program_b,以及输出到其中一片flash的选通片选信号cs1和输出到另一片flash的选通片选信号cs2信号。

[0011]

可选地,如上所述的fpga逻辑重加载电路中,

[0012]

在所述逻辑加载模式下控制fpga逻辑加载状态判断和重加载功能的方式,为:fpga默认从其中一片flash中加载逻辑,且在一个加载周期后fpga没有正常启动,则通过可编程逻辑电路的控制逻辑将加载信号cs选通到另一片flash上,并强制fpga开始新的加载序列。

[0013]

可选地,如上所述的fpga逻辑重加载电路中,

[0014]

所述逻辑在线升级模式下实现在线状态下对指定flash的逻辑升级功能的方式,为:在上电过程中通过使能在线升级使能信号en_online_upgrade以使能逻辑在线升级模式,并通过控制在线升级flash选择信号sel_online_flash选择待升级的flash,可编程逻辑电路通过判断以上信号对已选择的flash执行在线升级操作。

[0015]

可选地,如上所述的fpga逻辑重加载电路中,

[0016]

所述逻辑离线升级模式下实现离线状态下对指定flash的逻辑升级功能的方式,为:在上电过程中通过使能离线升级使能信号en_offline_upgrade以使能逻辑离线升级模式,并通过控制离线升级flash选择信号sel_offline_flash选择待升级的flash,可编程逻辑电路通过判断以上信号对已选择的flash执行离线升级操作。

[0017]

可选地,如上所述的fpga逻辑重加载电路中,所述可编程逻辑电路中的控制逻辑为:通过可编程逻辑电路控制fpga的加载过程,实现加载电路的冗余设计、可配置升级与加载动态切换功能;

[0018]

其中,可编程逻辑电路的控制逻辑控制架构包括:模式选择控制单元、计时器单元、加载控制单元和片选控制单元。

[0019]

可选地,如上所述的fpga逻辑重加载电路中,

[0020]

所述可编程逻辑电路中的模式选择控制单元,用于根据在线升级使能信号en_online_upgrade、离线升级使能信号en_offline_upgrade、在线升级flash选择信号sel_online_flash、离线升级使能信号en_offline_upgrade,以及超时信号timeout的状态,判断并输出片选选通控制信号cs_ctrl。

[0021]

可选地,如上所述的fpga逻辑重加载电路中,

[0022]

所述可编程逻辑电路中的计时器单元,用于通过时间设定信号timeset1和timeset2的值

‘

00’、

‘

01’、

‘

10’、

‘

11’设置相应的加载时间超时值分别为300ms、500ms、1s、2s,并在启动加载信号init_b有效后开始计时;

[0023]

在超时时间到达前若fpga逻辑加载完成信号done未有效,则输出的超时信号timeout为

‘1’

;

[0024]

在超时时间到达前若fpga逻辑加载完成信号done有效,则输出的超时信号timeout为

‘0’

;

[0025]

所述计时器单元,还用于在加载超时情况下,判断接收到的由加载控制单元输出的重加载信号reload的状态重新开始计时。

[0026]

可选地,如上所述的fpga逻辑重加载电路中,

[0027]

所述可编程逻辑电路中的加载控制单元,用于通过判断超时信号timeout状态,当加载超时即计时器单元输出的timeout为

‘1’

时,将逻辑加载信号program_b输出低脉冲以启动fpga重新加载流程,并且向计时器单元输出重加载信号reload。

[0028]

可选地,如上所述的fpga逻辑重加载电路中,

[0029]

可编程逻辑电路中片选控制单元,用于根据模式选择控制单元输出的片选选通控制信号cs_ctrl执行对ppga输出的片选信号cs至2片flash芯片的选通片选信号cs1和cs2的选通操作;其中,当cs_ctrl为

‘0’

时输出选通cs1,cs2无输出;当cs_ctrl为

‘1’

则输出选通cs2,cs1无输出。

[0030]

本发明的优点是:

[0031]

本发明实施例提供的fpga逻辑重加载电路,fpga逻辑存储加载电路采用至少2片flash互为备份设计,使用1片cpld控制2片fpga的加载过程,2片flash芯片的clk时钟信号、数据信号、地址信号、控制信号通过复用的连接方式连接到fpga,fpga输出的片选信号(cs)在flash与fpga之间通过cpld进行耦合。该fpga逻辑重加载电路,通过cpld中的控制逻辑实现fpga逻辑加载状态判断和重加载功能,并可实现在线和离线状态下对指定flash的逻辑升级功能。另外,本发明实施例的fpga逻辑重加载电路具有以下优点:

[0032]

1)、可靠性高:逻辑存储备份设计,自动判断fpga加载状态并确保加载异常情况下执行逻辑重加载操作;

[0033]

2)、工作模式可设置:可设置当前工作模式为逻辑加载模式或逻辑升级模式;

[0034]

3)、多种逻辑升级模式设置:支持在线、离线情况下对指定flash的逻辑升级功能;

[0035]

4)、兼容性好:适用于各种型号fpga的逻辑加载电路可靠性设计。

附图说明

[0036]

附图用来提供对本发明技术方案的进一步理解,并且构成说明书的一部分,与本申请的实施例一起用于解释本发明的技术方案,并不构成对本发明技术方案的限制。

[0037]

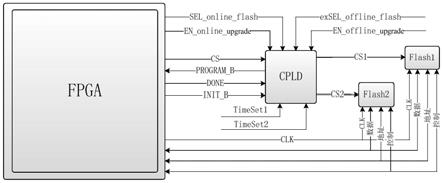

图1为用于执行本发明实施例提供的fpga逻辑的重加载方法的fpga逻辑重加载电路图的结构示意图;

[0038]

图2为图1所示实施例提供的fpga逻辑重加载电路图中cpld逻辑控制架构图。

具体实施方式:

[0039]

为使本发明的目的、技术方案和优点更加清楚明白,下文中将结合附图对本发明的实施例进行详细说明。需要说明的是,在不冲突的情况下,本申请中的实施例及实施例中的特征可以相互任意组合。

[0040]

本发明针对传统fpga逻辑存储及加载电路在出现flash芯片故障或升级加载异常中断时无法正常完成加载操作的缺点,创新地提出了一种fpga逻辑重加载电路及该电路的逻辑重加载方法,实现了fpga逻辑存储及加载电路的冗余设计、可配置升级与加载动态切换功能,从而避免了由于当前逻辑存储flash芯片故障或升级加载异常中断而导致的fpga逻辑无法正常完成加载的情况,并且提高了模块及系统的可靠性。

[0041]

本发明提供以下几个具体的实施例可以相互结合,对于相同或相似的概念或过程可能在某些实施例不再赘述。

[0042]

图1为本发明实施例提供的fpga逻辑重加载电路的结构示意图。本发明实施方案使用1片cpld控制fpga的加载过程,如图1所示fpga逻辑重加载电路及相关信号。本发明实施例中的fpga逻辑重加载电路,fpga的逻辑加载信号连接至cpld,在cpld上挂接2片flash芯片互为备份,2片flash芯片的时钟信号clk、数据信号、地址信号和控制信号通过复用的

连接方式连接到fpga,fpga输出的片选信号cs在flash与fpga之间通过可编程逻辑电路进行耦合。cpld的输入信号具体包括:cs、en_online_upgrade、en_offline_upgrade、sel_online_flash、sel_offline_flash、timeset1、timeset2、done、init_b信号,输出信号包括:program_b、cs1、cs2信号。

[0043]

fpga逻辑重加载电路的应用模式包括:逻辑加载模式、逻辑在线升级模式、逻辑离线升级模式。

[0044]

本发明实施例提供的fpga逻辑重加载电路,可以通过所述可编程逻辑电路控制2片flash的加载过程,从而通过可编程逻辑电路中的控制逻辑在逻辑加载模式下控制fpga逻辑加载状态判断和重加载功能,以及在逻辑在线升级模式下实现在线状态下对指定flash的逻辑升级功能,在逻辑离线升级模式下实现离线状态下对指定flash的逻辑升级功能。

[0045]

本发明实施例的fpga逻辑重加载电路中,fpga的逻辑加载信号rogram_b和fpga逻辑加载完成信号done均连接至可编程逻辑电路(cpld);

[0046]

该可编程逻辑电路(cpld)的输入信号包括:由fpga输入的片选信号cs、在线升级使能信号en_online_upgrade、在线升级flash选择信号sel_online_flash、所述done和启动加载信号init_b,以及由外部驱动输入的离线升级使能信号en_offline_upgrade、离线升级flash选择信号sel_offline_flash、时间设定信号timeset1和timeset2。

[0047]

该可编程逻辑电路(cpld)的输出信号包括:输出到fpga的逻辑加载信号program_b,以及输出到其中一片flash的选通片选信号cs1和输出到另一片flash的选通片选信号cs2信号。

[0048]

以下分别对上述3中应用模式的加载方式进行说明:

[0049]

逻辑加载模式为:fpga默认从其中一片flash中加载逻辑,当一个加载周期后如果fpga没有正常启动,则cpld通过控制逻辑将加载信号选通到另一片flash并强制fpga开始新的加载序列。

[0050]

逻辑在线升级模式为:在上电过程中通过使能“在线升级使能信号”en_online_upgrade使能在线升级模式,实际应用中,可以定义

‘1’

为使能/

‘0’

为禁止,在线升级操作完成后需禁止;并通过控制“在线升级flash选择”信号sel_online_flash选择升级的flash,cpld通过判断以上信号执行在线升级操作,模式状态真值表定义如表1所示。

[0051]

逻辑离线升级模式为:在上电过程中通过使能“离线升级使能信号”en_offline_upgrade使能离线升级模式,实际应用中,可以定义

‘1’

为使能/

‘0’

为禁止,默认为拉低;并通过控制“离线升级flash选择”信号sel_offline_flash选择升级的flash,cpld通过判断以上信号执行离线升级操作,模式状态真值表如表1定义所示。

[0052]

表1模式状态真值表

[0053][0054]

通过cpld控制fpga的加载过程,实现加载电路的冗余设计、可配置升级与加载动态切换功能。如图2所示,为本发明实施例中cpld逻辑控制架构的示意图,该cpld的控制逻辑为:通过可编程逻辑电路控制fpga的加载过程,实现加载电路的冗余设计、可配置升级与加载动态切换功能,该cpld的逻辑控制架构包括:模式选择控制单元、计时器单元、加载控制单元和片选控制单元等部分。下面结合输入/输出信号及具体操作进行说明。

[0055]

(1)模式选择控制单元

[0056]

定义模式状态真值表如表1所示,模式选择控制单元根据“在线升级使能信号”en_online_upgrade、“离线升级使能信号”en_offline_upgrade、“在线升级flash选择信号”sel_online_flash、“离线升级使能信号”en_offline_upgrade以及“超时信号”timeout的状态判断并输出“片选选通控制信号”cs_ctrl;

[0057]

(2)计时器单元

[0058]

计时器单元通过“时间设定信号”timeset1/timeset2的值(

‘

00’、

‘

01’、

‘

10’、

‘

11’)设置相应的加载时间超时值,例如分别为300ms、500ms、1s、2s,在“启动加载信号”init_b有效(

‘1’

为有效)后开始计时,在超时时间到达前若“fpga逻辑加载完成信号”done未有效(

‘1’

为有效,

‘0’

为无效),则输出“超时信号”timeout为“1”,否则输出为

‘0’

,判断接收到的由加载控制单元输出的“重加载信号”reload(

‘1’

为有效)的状态重新开始计时。

[0059]

(3)加载控制单元

[0060]

加载控制单元,判断“超时信号”timeout状态,当加载超时即计时器单元输出的timeout为

‘1’

时将“逻辑加载信号”program_b输出低脉冲(默认为外部拉高处理)启动fpga重新加载流程,同时向计时器单元输出“重加载信号”reload(

‘1’

为有效)。

[0061]

(4)片选控制单元

[0062]

片选控制单元,根据模式选择控制单元输出的“片选选通控制信号”cs_ctrl实现ppga输出的“片选信号”cs至2片flash芯片“选通片选信号”cs1和cs2的选通,具体见表1模式状态真值表定义。当cs_ctrl为

‘0’

时输出选通cs1,cs2无输出;当cs_ctrl为

‘1’

则输出选通cs2,cs1无输出。

[0063]

本发明实施例提供的fpga逻辑重加载电路,fpga逻辑存储加载电路采用至少2片flash互为备份设计,使用1片cpld控制2片fpga的加载过程,2片flash芯片的clk时钟信号、数据信号、地址信号、控制信号通过复用的连接方式连接到fpga,fpga输出的片选信号(cs)

在flash与fpga之间通过cpld进行耦合。该fpga逻辑重加载电路,通过cpld中的控制逻辑实现fpga逻辑加载状态判断和重加载功能,并可实现在线和离线状态下对指定flash的逻辑升级功能。另外,本发明实施例的fpga逻辑重加载电路的可靠性高:逻辑存储备份设计,自动判断fpga加载状态并确保加载异常情况下执行逻辑重加载操作;工作模式可设置:可设置当前工作模式为逻辑加载模式或逻辑升级模式;多种逻辑升级模式设置:支持在线、离线情况下对指定flash的逻辑升级功能;兼容性好:适用于各种型号fpga的逻辑加载电路可靠性设计。

[0064]

采用本发明实施例提供的fpga逻辑重加载电路,可以避免传统fpga逻辑存储及加载电路在出现flash芯片故障或升级加载异常中断时无法正常完成加载操作的缺点,实现了fpga逻辑存储及加载电路的冗余设计、可配置升级与加载动态切换功能,提高了模块及系统的可靠性。

[0065]

虽然本发明所揭露的实施方式如上,但所述的内容仅为便于理解本发明而采用的实施方式,并非用以限定本发明。任何本发明所属领域内的技术人员,在不脱离本发明所揭露的精神和范围的前提下,可以在实施的形式及细节上进行任何的修改与变化,但本发明的专利保护范围,仍须以所附的权利要求书所界定的范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1