用于FFT处理器芯片设计的新型改良蝶形单元算法结构的制作方法

用于fft处理器芯片设计的新型改良蝶形单元算法结构

技术领域

[0001]

本发明涉及fft处理器技术领域,具体为用于fft处理器芯片设计的新型改良蝶形单元算法结构。

背景技术:

[0002]

fft处理器广泛应用于频谱分析、图像处理、语音识别、生物医学、雷达、滤波、无线及有线通信等领域。随着5g时代的到来,不断涌现的各类新的业务和应用场景如车联网、虚拟现实、在线游戏、机器类通信、物联网等,面向5g时代对上述新业务的需求,新的多载波传输技术应运而生,如滤波器组多载波、广义频分复用、通用滤波多载波等。fft处理器作为多载波传输系统中最为重要的模块,其所消耗的硬件成本及功耗影响着整个多载波传输系统的表现,因此对于fft处理器的优化设计显得尤为重要。

[0003]

以往对于fft处理器的优化设计大多在算法与整体架构上进行优化,而且目前算法与整体架构的研究已趋于成熟,很难有所突破,本发明着眼于蝶形单元的架构改良设计,为fft处理器的优化设计提供新的思路和方向。因此,我们提出一种用于fft处理器芯片设计的新型改良蝶形单元算法结构。

技术实现要素:

[0004]

本发明的目的在于提供用于fft处理器芯片设计的新型改良蝶形单元算法结构,以解决上述背景技术提出的目前fft处理器的优化设计所存在条件限制的问题。

[0005]

为实现上述目的,本发明提供如下技术方案:

[0006]

用于fft处理器芯片设计的新型改良蝶形单元算法结构,包括模块旋转因子以及控制逻辑“r”,在原有蝶形单元构架基础上增加特定的模块旋转因子以及额外的控制逻辑“r”形成新型改良蝶形单元架构模型,在fft处理器芯片的设计上采用流行的基-2

k

算法和sdf流水线架构。

[0007]

优选的,所述模块旋转因子的计算公式为其中中的n是根据所设计fft处理器的点数来确定。

[0008]

优选的,所述控制逻辑“r”用来控制输入序列进行与w进行复数乘法运算,“n”为fft点数,“t”和“x”为基本蝶形运算控制信号,分别对应进行乘以

“-

j”运算和是否进行蝶形运算,为减小关键路径,在w复数乘法运算模块与选择器之间增加流水线型寄存器。

[0009]

优选的,针对基-2

k

算法sdf流水线架构的fft处理器来说,新型改良蝶形单元的控制逻辑“r”可通过公式求出,其中“c”代表fft处理器的控制时钟,代表异或逻辑运算,“·”代表与逻辑运算,“k”代表基-2

k

算法的k值,“n”代表时钟的最高位值。

[0010]

优选的,所述模块旋转因子的值呈规律性重复。

[0011]

与现有技术相比,本发明的有益效果是:

[0012]

1、减少fft处理器设计时的硬件资源消耗;

[0013]

2、简化实现fft处理器复数乘法运算乘法器的控制逻辑;

[0014]

3、对于实现点数不超过1024的fft处理器设计上,可利用csd常数乘法器替代传统复数乘法器,达到最小化硬件资源消耗的目的。

[0015]

综上所述,本发明提供的用于fft处理器芯片设计的新型改良蝶形单元算法结构,着眼点放在构成fft处理器的基本单元蝶形单元的改良上,通过简化后续旋转因子的复杂度的方式降低fft处理器的硬件开销与功耗,为新信息时代背景下低功耗、低硬件开销fft处理器的设计提供了新思路,具有重要的理论意义和工程应用价值。

附图说明

[0016]

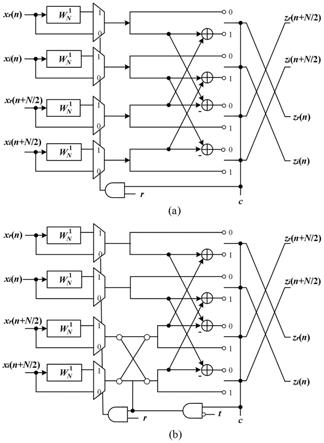

图1为本发明的原有蝶形单元架构(a)i型蝶形单元(b)ii型蝶形单元示意图。

[0017]

图2为本发明的新型改良蝶形单元架构(a)i型改良蝶形单元(b)ii型改良蝶形单元示意图。

[0018]

图3为本发明的改良64点基-25算法sdffft流水线架构示意图。

[0019]

图4为本发明的基于新型改良蝶形单元的64点基-25算法信号流图。

具体实施方式

[0020]

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一机构实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

[0021]

请参阅图1-图4,本发明提供一种技术方案:用于fft处理器芯片设计的新型改良蝶形单元算法结构:

[0022]

如图1所示,为原有蝶形单元架构,(a)为i型,(b)为ii型,其中xr(n)与xr(n+n/2)为输入复数序列的实部,xi(n)与xi(n+n/2)为输入复数序列的虚部,zr(n)与zr(n+n/2)为输出复数序列的实部,zi(n)与zi(n+n/2)为输出复数序列的虚部,“t”和“c”为蝶形单元逻辑控制端,它们与fft处理器的控制时钟相关联。

[0023]

如图2所示,在原有蝶形单元架构的基础上增加特定模块旋转因子以及额外的控制逻辑“r”形成新型改良蝶形单元架构模型,其中中的n是根据所设计fft处理器的点数来确定的,比如设计1024点fft处理器,那么n=1024,由于当n的值越大,的实部越接近1,虚部越接近0,在原有蝶形单元的基础上所增加的模块所占用的硬件资源越小,因此本发明所设计的改良蝶形单元在长点fft处理器芯片优化设计方面效果更好。

[0024]

在fft处理器芯片的设计上采用流行的基-2

k

算法和sdf流水线架构,这是由于基-2

k

算法拥有与基-2算法同样简单的蝶形架构同时又可以减少旋转因子的复杂度,而采用sdf流水线架构是因为一方面实现简单,执行速度快,资源使用占比高,针对基-2

k

算法sdf

流水线架构的fft处理器来说,新型改良蝶形单元的控制逻辑“r”可通过公式求出,其中“c”代表fft处理器的控制时钟,代表异或逻辑运算,“·”代表与逻辑运算,“k”代表基-2

k

算法的k值,“n”代表时钟的最高位值(如控制64点fft处理器运算的时钟最高位为5,即c5c4c3c2c1c0)。

[0025]

如图3所示,下面以基-25算法实现64点sdf架构fft处理器为例说明改良蝶形单元如何实现降低fft处理器设计时所消耗的硬件资源,图3为所示为改良64点基-25算法sdf fft流水线架构图,其中mod bfii部分即为改良蝶形单元部分,代表复数乘法运算,bfi和bfii分别代表了i型和ii型原始蝶形单元。

[0026]

图4所示为基于新型改良蝶形单元的64点基-25算法信号流图,由图4可知,框选的a蝶形部分为使用改良蝶形单元计算的部分,由于使用了改良蝶形单元,由框选的b部分的旋转因子由原来的转换成复杂度减少为原来的一半,同时,旋转因子的值呈现规律性重复(0,16,8,24,4,20,12,28,2,18,10,26,6,22,14,30

……

),大幅降低了复数乘法器控制逻辑的复杂度,通过使用本发明的改良蝶形单元后,能够大幅降低fft处理器的所消耗的硬件资源与功耗。

[0027]

本发明使用verilog hdl语言对设计进行硬件描述,在基于quartus prime平台进行开发,开发平台的评估报告显示,在实现64点fft处理器时,使用本发明的新型改良蝶形单元,与以往的研究相比,能够减少硬件资源消耗25%,功耗降低18%,由于改良蝶形单元的特性,对于点数更大的fft处理器效果更加好,因此,有理由证明将新型改良蝶形单元用于长点fft处理器的设计会有更好的表现。

[0028]

尽管参照前述实施例对本发明进行了详细的说明,对于本领域的技术人员来说,其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中机构技术特征进行等同替换,凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1