多屏幕显示控制装置的制作方法

1.本发明有关于多屏幕组装成的大屏幕的显示技术。

背景技术:

2.多屏幕显示有多种应用,如商场的超大规模液晶屏、或大规模的监控显示屏。由于液晶面板的制作瓶颈,大屏幕是由多个小屏幕组装而成;故此技术称多屏幕显示。

3.图1以方块图图解传统的多屏幕显示系统100,由2x2显示器102_1、102_2、102_3、102_4组装成大屏幕。主机104以高画质多媒体接口(high definition multimedia interface,缩写:hdmi)与分配器(splitter)106通信;主机104产生的4k高画质多媒体接口影像信号hdmi_0传递至分配器106,由分配器106复制为四个相同的4k高画质多媒体接口影像信号hdmi_1、hdmi_2、hdmi_3、hdmi_4,交予对应的图像缩放芯片(scaler)108_1、108_2、108_3、108_4。各图像缩放芯片会将接收到的4k高画质多媒体接口影像信号放大四倍,取其中四分之一画面(hdmi1080p)由对应的显示器播放。显示器102_1、102_2、102_3、102_4组合出的大屏幕画面。

4.传统多屏幕显示系统100的分配器106的hdmi影像复制技术成本高。特别是,多个图像缩放芯片108_1

…

108_4间有同步问题,可能会引入

±

1帧(16ms)的画面不同步现象。面对更大尺寸的画面播放需求,显示器数量激增,hdmi影像复制量更多,图像缩放芯片数量也更多;伴随而来的,是更惊人的成本,以及越发明显的画面不同步现象。此外,视频墙的屏幕有一定边框厚度且厚度不确定,需要裁剪掉一部分图像。使用分配器复制画面的方法,可以理解为"信号复制后裁剪",所以很难做到"边框消除"。

5.传统的另一个弊端是,纯硬件完成视频墙拼接,无法做到任意形态,比如16屏显示器,架构就是固定的4x4。

技术实现要素:

6.本发明提出低成本的多屏幕显示方案,且有效同步多屏幕显示。

7.根据本发明一种实施方是所实现的一多屏幕显示控制装置包括:多张卡;以及串接上述多张卡的多条通用串行总线(usb)。这些通用串行总线用于传递一主机提供的一影像数据。上述多张卡中的一第一级单卡包括多个第一级图像处理器(gpus)、以及一第一时钟缓冲器(clock buffer)。这些第一级图像处理器根据该影像数据产生多个高画质多媒体接口(hdmi)画面供多个显示器播放。该第一时钟缓冲器将一时钟信号以多路耦接至这些第一级图像处理器,使这些第一级图像处理器为时钟同源。该第一时钟缓冲器还分一路将该时钟信号耦接到该第一级单卡的一时钟信号输出端,供应给上述多张卡中的一第二级单卡。

8.一种实施方式中,该第一级单卡包括一第一晶振,供应该时钟信号给该第一时钟缓冲器。

9.一种实施方式中,该第二级单卡包括一时钟信号输入端、多个第二级图像处理器、

一第二晶振、一时钟多任务器、以及一第二时钟缓冲器。该时钟信号输入端耦接该第一级单卡的该时钟信号输出端。根据该影像数据,这些第二级图像处理器产生多个高画质多媒体接口画面供该第二级单卡所控制的多个显示器播放。该时钟多任务器具有一第一输入端耦接该第二晶振、以及一第二输入端耦接该时钟信号输入端。该第二时钟缓冲器耦接该时钟多任务器的一输出端,并具有多路输出耦接这些第二级图像处理器,使这些第二级图像处理器为时钟同源。

10.一种实施方式中,该第二级单卡还包括一时钟切换逻辑电路。该时钟切换逻辑电路耦接该时钟信号输入端,于该时钟信号输入端上检测不到时钟振荡时,切换一多任务器控制信号,操作该时钟多任务器耦接该第二晶振至该第二时钟缓冲器。一种实施方式中,该时钟切换逻辑电路提供的该多任务器控制信号默认操作该时钟多任务器耦接该时钟信号输入端至该第二时钟缓冲器。

11.一种实施方式中,该第二级单卡还包括一复位电路,在该时钟切换逻辑电路切换该时钟多任务器时,复位这些第二级图像处理器。一种实施方式中,该第二级单卡还包括一复位信号输入接口,用以接收该第一级单卡发出的一复位要求。该复位电路还耦接该复位信号输入接口,在该复位信号输入接口接收有该复位要求时,复位这些第二级图像处理器。一种实施方式中,该第二级单卡还包括一复位信号输出接口,耦接上述多张卡的一第三级单卡。复位这些第二级图像处理器时,该复位电路还透过该复位信号输出接口要求复位该第三级单卡的多个第三级图像处理器。

12.一种实施方式中,该复位电路包括一脉冲产生电路以及一逻辑闸。根据该多任务器控制信号、以及延时的该多任务器控制器信号的变动,该脉冲产生电路输出脉冲。该逻辑闸具有一第一输入端耦接该复位信号输入接口、一第二输入端接收该脉冲产生电路产生的脉冲、以及一输出端耦接这些第二级图像处理器各自的一复位脚位。该逻辑闸的该输出端可耦接该复位信号输出接口。

13.一种实施方式中,该逻辑闸包括:一电压比较器以及一与门。该电压比较器耦接该复位信号输入接口,判断是否为低位信号。该与门,接收该电压比较器的输出、以及该脉冲产生电路的输出,以产生该逻辑闸该输出端的信号。

14.一种实施方式中,该多屏幕显示控制装置还包括:一机壳,包装上述多张卡;一通用串行总线接口,用以耦接该主机,以接收该影像数据;以及多个高画质多媒体接口接口,用以耦接上述多张卡中各级单卡供应画面显像的这些显示器。该多屏幕显示控制装置可为一热插入装置,单卡间以复位信号输出接口以及复位信号输入接口相连即一起复位。

15.下文特举实施例,并配合所附图示,详细说明本发明内容。

附图说明

16.图1以方块图图解传统的多屏幕显示系统100,采用分配器(splitter)106以及图像缩放芯片(scaler)108_1

…

108_4;

17.图2图解根据本发明一种实施方式实现的一多屏幕显示系统200,采用usb接口与主机204通信,并采用hdmi接面连结显示器202_1、202_2、202_3、以及202_4;

18.图3根据本发明一种实施方式图解一单卡300,连结在前一级单卡302、以及后一级单卡304之间;

19.图4图解同步电路312的一种实施方式,为表决电路;

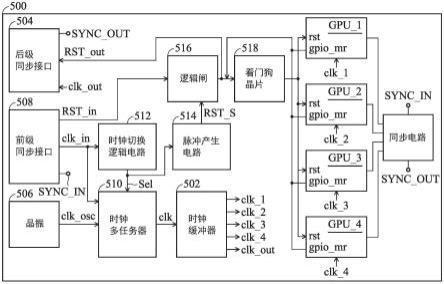

20.图5a图解根据本发明一种实施方式所实现的一单卡500,着眼于同步、以及当机修复技术;

21.图5b图解逻辑闸516的一种实施方式;

22.图6a图解用作时钟切换逻辑电路512的单稳态触发器600;

23.图6b图解图6a单稳态触发器的输入端a、b以及输出端q的信号;

24.图7a图解脉冲产生电路514的一种实施方式;

25.图7b图解图7a脉冲产生电路514的输入端a、b以及输出端y的信号;

26.图8根据本发明一种实施方式图解一多屏幕显示控制装置800。

27.【符号说明】

28.100~传统的多屏幕显示系统;

29.102_1、102_2、102_3、102_4~小屏幕;

30.104~主机;

31.106~分配器;

32.108_1、108_2、108_3、108_4~图像缩放芯片;

33.200~多屏幕显示系统;

34.202_1、202_2、202_3、以及202_4~显示器;

35.204~主机;

36.206~多屏幕显示控制装置;

37.208~影像压缩器;

38.210~通用串行总线接口;

39.212~通用串行总线集线器;

40.214_1、214_2、214_3、以及214_4~高画质多媒体接口;

41.300~单卡;

42.302、304~前一级、后一级单卡;

43.306~输入端通用串行总线接口;

44.308~通用串行总线集线器;

45.310~输出端通用串行总线接口;

46.312~同步电路;

47.500~单卡;

48.502~时钟缓冲器;

49.504~后级同步接口;

50.506~晶振;

51.508~前级同步接口;

52.510~时钟多任务器;

53.512~时钟切换逻辑电路;

54.514~脉冲产生电路;

55.516~逻辑闸;

56.518~看门狗芯片;

57.522~电压比较器522;

58.524~"与"门;

59.600~单稳态触发器;

60.800~多屏幕显示控制装置;

61.802~主机;

62.804~通用串行总线接口;

63.806~高画质多媒体接口;

64.808~多屏幕显示器;

65.810~前、后级同步接口;

66.a、b、q、y~单稳态触发器600/脉冲产生器514的输入、输出端;

67.bjt_1、bjt_2、bjt_3、bjt_4~三极管;

68.clk~时钟信号;

69.clk_1、clk_2、clk_3、clk_4、以及clk_out~复制时钟信号clk的多路;

70.clk_osc~晶振信号;

71.gpio_mr、gpio_rd、gpio_wr~通用输入输出脚位;

72.gpu_1、gpu_2、gpu_3、gpu_4~图像处理器;

73.hdmi_0、hdmi_1、hdmi_2、hdmi_3、hdmi_4~4k高画质多媒体接口影像信号;

74.rt~时间长度;

75.rst~复位脚位;

76.rst_in、rst_out~复位信号输入、输出;

77.rst_s~复位信号;

78.sel~多任务器控制信号;

79.sync_in、sync_out~同步控制输入、输出接口;

80.usb_s~通用串行总线接口传输的影像数据。

具体实施方式

81.以下叙述列举本发明的多种实施例。以下叙述介绍本发明的基本概念,且并非意图限制本发明内容。实际发明范围应由权利要求书界定。

82.本发明多屏幕显示技术不采用分配器(splitter)以及图像缩放芯片(scaler)。本发明多屏显示方案是由主机经通用串行总线(usb)接口提供高画质的影像数据,交由多个图像处理器(gpus)处理成多个小屏幕画面,再组合出大屏幕显示。相比传统多屏幕显示系统100,本发明有以下优点:

83.·

不若图像缩放芯片(scaler)有所限制,图像处理器(gpus)可以实现任意数量小屏幕的组合,如1x9、2x4、1x16 2x8 16x1

…

等;

84.·

不受主显示适配器的限制,图像处理器(gpus)有能力实现任意角度的旋转,以达到艺术墙的效果,也有能力实现高分辨率(如,4k、8k

…

)的图像拼接;

85.·

图像处理器(gpus)得以轻松去边框,优化显示器与显示器边缘的画面;

86.·

不若图像缩放芯片的放大失真,本发明大屏幕显示清晰度高;

87.·

除了高带宽(例如,usb 3.0的5g bps带宽),经通用串行总线(usb)传递的高画

质影像信号更可为压缩型式,足以驱动16个甚至更多的高画质多媒体接口(hdmi)显示器,低成本组成大屏幕画面;

88.特别是,本说明书对图像处理器(gpus)提供同步设计以及复位方案,使所有小屏幕显示器得以正确组出大屏幕画面。

89.图2图解根据本发明一种实施方式实现的一多屏幕显示系统200,由2x2显示器202_1、202_2、202_3、以及202_4组装成大屏幕。主机204以通用串行总线(如usb 3.0)与一多屏幕显示控制装置206通信。多屏幕显示控制装置206与显示器202_1、202_2、202_3、以及202_4系采高画质多媒体接口(high definition multimedia interface,缩写:hdmi)通信。多屏幕显示控制装置206中采用两个图像处理器(gpus)gpu_1、以及gpu_2。单个图像处理器可以应付两个小屏幕。

90.主机204可运行一影像压缩器208,可由主机204安装多屏幕显示控制装置206的驱动程序实现。经usb接口,压缩后的高画质(如4k)的影像数据usb_s透过usb接口传递至多屏幕显示控制装置206,由usb接口210接收,再经usb集线器(usb hub)212交予图像处理器gpu_1以及gpu_2。图像处理器gpu_1以及gpu_2有解压缩功能。图像处理器gpu_1对应显示器202_1以及202_2产生两个hdmi画面(如,两幅hdmi 1080p),经由两个hdmi接口214_1以及214_2供应给显示器202_1以及202_2播放。图像处理器gpu_2对应显示器202_3以及202_4产生两个hdmi画面(如,两幅hdmi 1080p),经由两个hdmi接口214_3以及214_4供应给显示器202_3以及202_4播放。显示器202_1、202_2、202_3、以及202_4所播放的四个hdmi 1080p画面组合成大屏幕画面。

91.由于主机204具有影像压缩器208、且是采用usb接口与多屏幕显示控制装置206通信,影像数据usb_s不只可为4k高画质影像信号,更可为8k或16k的大量数据,足以高质量实现超大屏幕的显示器。主机204可更安装有一个视频墙配置软件,目的是把大画面切割为2x 2个小画面后通过通用串行总线输出。如此一来,影像数据usb_s传递的4k高画质影像信号是2x 2个小画面串流组成。影像数据usb_s完全能够应付4k高画质影像信号的传递。同时,这个视频墙配置软件,可更负责边框消除,旋转等功能。

92.以上设计使得主机204提供的影像数据usb_s可以就是大屏幕显像需求。例如,应付8k大屏幕显像,主机204提供的影像数据usb_s可以就是8k的影像数据:应付16k大屏幕显像,主机204提供的影像数据usb_s可以就是16k的影像数据。

93.特别是,组合出来的画面越大,使用到的显示器越多,相应使用的图像处理器(gpus)数量也越多。为了兼容各种尺寸的大屏幕显示,本发明一种实施方式是设计单卡。每张单卡为一张印刷电路板,焊接有多个图像处理器。多张卡串接使用即可提供大量图像处理器。

94.图3根据本发明一种实施方式图解一单卡300,连结在前一级单卡302、以及后一级单卡304之间。各级单卡结构可以类似单卡300。

95.主机204提供的影像数据usb_s将自前一级单卡302的输出端usb接口传递至单卡300的输入端usb接口306,再经usb集线器308交予单卡300的输出端usb接口310输出,传递至下一级单卡304的输入端usb接口。usb集线器308更将影像数据usb_s传递至四个图像处理器gpu_1、gpu_2、gpu_3、以及gpu_4,使产生八个hdmi画面(如,八幅hdmi 1080p),经hdmi接口输出,交由八个显示器显像。除了单卡300所产生的八个hdmi画面,前一级单卡302、以

及后一级单卡304也根据影像数据usb_s各自产生八个hdmi画面。串接的多张卡可根据同一影像数据usb_s产生高质量的分割画面,控制数量庞大的显示器组合出大屏幕画面。

96.特别是,单卡300具有一同步电路312,除了同步单卡300上的四个图像处理器gpu_1、gpu_2、gpu_3、以及gpu_4,更用于不同级单卡的图像处理器(gpus)同步。

97.单卡300以一同步控制输入接口sync_in与前一级单卡302的同步控制输出接口sync_out链接。单卡300更以一同步控制输出接口sync_out与后一级单卡304的同步控制输入接口sync_in链接。不同单卡302、304、306上的同步电路因而耦接在一起,使单卡302、304、306上所有图像处理器(gpus)同步。

98.图4图解同步电路312的一种实施方式。由于不同图像处理器接收到影像数据usb_s的时间点可能有出入,所以不同图像处理器需要彼此握手通信后,再一起输出hdmi画面,使显示器同步显像。同步电路312以表决电路实现不同图像处理器之间的握手通信。

99.同步电路312对应四个图像处理器gpu_1、gpu_2、gpu_3、以及gpu_4提供四个三极管bjt_1、bjt_2、bjt_3、以及bjt_4。各图像处理器有两个通用输入输出(gpio)脚位被用于同步设计,标号为gpio_wr以即gpio_rd。通用输入输出脚位gpio_wr耦接对应的三极管的基极(base)。通用输入输出脚位gpio_rd耦接对应的三极管的集极(collector)。所有三极管bjt_1、bjt_2、bjt_3、以及bjt_4的集极连结在一起。

100.通用输入输出脚位gpio_wr默认值为高准位,使三极管bjt_1、bjt_2、bjt_3、以及bjt_4默认导通,具有低电平集极。图像处理器接收到影像数据usb_s时,拉低其通用输入输出脚位gpio_wr的准位(举手),关闭对应的三极管。四个图像处理器gpu_1、gpu_2、gpu_3、以及gpu_4全数收到影像数据usb_s时,四个三极管bjt_1、bjt_2、bjt_3、以及bjt_4全数关闭,集极准位拉高,并同步反应在四个图像处理器gpu_1、gpu_2、gpu_3、以及gpu_4的通用输入输出脚位gpio_rd上,使四个图像处理器gpu_1、gpu_2、gpu_3、以及gpu_4同步输出hdmi画面信号,达成多个显示器的同步显像。

101.如图所示,四个三极管bjt_1、bjt_2、bjt_3、以及bjt_4的集极(collectors)连结单卡上的同步控制输入接口sync_in(与前一级单卡连结)、以及同步控制输出接口sync_out(与后一级单卡连结)。如此一来,串接的多张卡上的所有图像处理器(gpus)都参与举手表决。

102.图像处理器(gpus)同步的另一项重要手段,是令其时钟同源。每颗图像处理器(gpus)使用相同时钟信号,可确保同步。以下段落说明多种时钟同源技术。

103.一种实施方式中,时钟信号是从第一级单卡一路耦接至最后一级单卡使用。一种实施方是在单卡上设计一时钟自动切换机制,预设选择前一级单卡提供的时钟信号,并在检测不到前一级单卡提供的时钟信号时,切换选择自身单卡上的晶振(oscillator)提供的时钟信号。

104.相应时钟信号切换,本发明一种实施方式提供复位设计:在时钟信号切换时,触发图像处理器的复位(例如,重新上电、或硬件复位)。特别是,复位要求会捆绑后级所有单卡。多张卡的串接可更包括复位信号输入/输出接口的串接。

105.本发明更有一种实施方式系用于应付图像处理器的当机状况。系以一看门狗芯片提供自动复位功能。

106.图5a图解根据本发明一种实施方式所实现的一单卡500,着眼于同步、以及当机修

复技术。

107.为了实现时钟同源,单卡500具备一时钟缓冲器(clock buffer)502,将同一时钟信号clk以四路clk_1、clk_2、clk_3、以及clk_4供应给四个图像处理器gpu_1、gpu_2、gpu_3、以及gpu_4。四个图像处理器gpu_1、gpu_2、gpu_3、以及gpu_4达成时钟同源,更稳定同步。

108.因应多张卡串接的应用,时钟缓冲器502更可将时钟信号clk复制在线路clk_out上,由后级同步接口504的一时钟信号输出端传递到下一级单卡。

109.时钟信号clk来源可能是单卡500本身的晶振(oscillator)506,也可能是前一级单卡经一前级同步接口508的一时钟信号输入端传来的一前级时钟信号clk_in。如图所示,单卡500包括一时钟多任务器510以及一时钟切换逻辑电路512。时钟切换逻辑电路512检测前级时钟信号clk_in。若前级时钟信号clk_in存在且正常工作,时钟切换逻辑电路512以多任务器控制信号sel令该时钟多任务器510将前级时钟信号clk_in输出作为时钟信号clk。若检测不到前级时钟信号clk_in,时钟切换逻辑电路512以多任务器控制信号sel令该时钟多任务器510将晶振506输出的晶振信号clk_osc输出作为时钟信号clk。

110.整理之,若仅使用单卡500,图像处理器gpu_1、gpu_2、gpu_3、以及gpu_4所采用的时钟信号为晶振506所产生的晶振时钟clk_osc,时钟同源。若串接多个单卡使用,第一级单卡的晶振信号串接到每一级单卡,不同单卡上的所有图像处理器(gpus)时钟同源。

111.不论是由晶振信号clk_osc切换到前级时钟信号clk_in、或是从前级时钟信号clk_in切换到晶振信号clk_osc,时钟信号切换事件可能引发图像处理器当机。一种实施方式中,根据512的电路,当发生板级插拔,必然触发时钟切换事件。时钟切换事件必然触发复位。因应复位需求的复位电路可单纯包括脉冲产生电路514、或更包括逻辑闸516、或更包括看门狗芯片518。

112.脉冲产生电路514耦接该时钟切换逻辑电路512,相应时钟切换事件产生脉冲作为复位信号rst_s,耦接图像处理器gpu_1

…

gpu_4的复位脚位rst,使图像处理器gpu_1

…

gpu_4重新上电,解决当机问题。

113.因应多级单卡串接的应用,复位事件也可能是由上一级单卡引发。前一级单卡可经前级同步接口508的一复位信号输入端得到复位输入rst_in。逻辑闸516将前级单卡传来的复位输入rst_in、与脉冲产生电路514产生的复位信号rst_s合成,耦接图像处理器gpu_1

…

gpu_4的复位脚位rst,使图像处理器gpu_1

…

gpu_4重新上电,解决当机问题。逻辑闸516运算前级单卡传来的复位输入rst_in、以及复位信号rst_s,其输出更耦接后级同步接口504做为复位输出rst_out,经后级同步接口504的一复位信号输出端传输到下一级单卡。

114.图5b图解逻辑闸516的一种实施方式。以低位复位为例,逻辑闸516可由两个电路组成,分别为电压比较器522及"与"门524。电压比较器522用于判断前级单卡传来的复位输入rst_in是否确实为低位。脉冲产生电路514(如"同或"门)的输出rst_s、和电压比较器522的输出作为"与"门524的输入,"与"门524的输出即用作图像处理器gpu_1

…

gpu_4的复位脚位rst控制,且为rst_out输出到后级。多卡级联时,如果出现前级板卡断电但前后级同步接口的物理连接未断开的情况,前级板卡的rst_in会因断电变低(因为前后级板卡同步接口连接,rst_in电压大约在1v左右),如果没有电压比较器,rst_in的1v电压直接传递给"与"门后会输出低,那么后级板卡的reset就会变低,从而导致所有后级板卡都不能正常工作了。加入电压比较器后,可以保证这种情况时,比较器的后端输出为高。

115.图示实施例为了更应付任一图像处理器当机的状况,在逻辑闸516之后更设置看门狗芯片518(选用),统整各种复位事件。看门狗芯片518除了接收逻辑闸516的输出,将前述复位操作反映在各图像处理器的复位脚位rst,更在图像处理器当机时,操作各图像处理器的复位脚位rst进行复位。

116.看门狗芯片518有自动复位的设计。图像处理器gpu_1

…

gpu_4各自提供一通用输入输出脚位gpio_mr连接至该看门狗芯片518作为输入。主机端可以根据各图像处理器的响应信号(心跳)发觉任一级单卡的任一图像处理器的异常。一种实施方式中,各图像处理器系经该通用串行总线接口定时输出信息给主机,使主机监控是否有当机的图像处理器。一旦定时信息消失,主机即认定相应的图像处理器当机。反之,图像处理器也可检测主机端的响应信号(心跳),判断是否与主机正常通信。一种实施方式中,图像处理器尝试解码失败或无法访问图像处理器存储器(如ddr)

…

等动作时,图像处理器无能力在规定时间内收到主机发送的"心跳包",从而通过通用输入输出脚位gpio_mr操作所链接的看门狗芯片518输出一复位信号(如,240ms的低电平脉冲),灌入所连结的图像处理器的复位脚位rst。举例来说,与主机通信中断的单卡上只要还有固件程序活着的图像处理器,便可实现所述自动复位,复位该张单卡上的所有图像处理器。倘若固件程序已跑飞,看门狗芯片518感测不到信号,也会操作各图像处理器的复位脚位rst进行复位。

117.一种实施方式中,图像处理器有内置紧密耦合存储器(tightly-coupled memory,tcm),为高可靠的内置存储区域,固件的中断向量表位于其中。当程序跑飞后,进阶精简指令集机器(advanced risc machine,arm)会进入abort分支,而预读取中断或资料中断异常发生时进入的特权模式(abort分支)在tcm区工作,处理的内容就是使用汇编代码控制该通用输入输出脚位gpio_mr,从而复位该看门狗芯片518。

118.一种实施方式中,时钟切换逻辑电路512是以一单稳态触发器实现。如图6a所示,用作时钟切换逻辑电路512的单稳态触发器600的输入端a接收前级时钟信号clk_in,输入端b固定高电平"1",输出端q提供多任务器控制信号sel操作时钟多任务器510。相应输入端a所接收的前级时钟信号clk_in的下降缘(有振荡),输出端q信号维持高电平至少一时间长度rt,使时钟多任务器510选择前级时钟信号clk_in作为时钟信号clk输出。倘若连结输入端a的前级时钟clk_in不存在,输出端q信号维持低电平,使时钟多任务器510选择晶振信号clk_osc作为时钟信号clk输出。

119.图6b图解图6a单稳态触发器的输入端a、b以及输出端q的信号。输入端a的前级时钟信号clk_in存在且正常工作,则输出端q信号为高电平。反之,输出端q信号为低电平。

120.图7a图解脉冲产生电路514的一种实施方式,采用的逻辑电路会将输入端a、b的电平变化反应在输出端y上。输入端a接收时钟切换逻辑电路512所产生的多任务器控制信号sel。多任务器控制信号sel更经rc延时输入该输入端b。输出端y信号即复位信号rst_s。

121.图7b图解图7a脉冲产生电路514的输入端a、b以及输出端y的信号。相应输入端a、b信号的电平变化,输出端y信号产生低电平脉冲,即复位信号rst_s。

122.图8根据本发明一种实施方式图解一多屏幕显示控制装置800。一主机802以usb接口804链接该多屏幕显示控制装置800。该多屏幕显示控制装置800以hdmi接口806链接多个显示器所组成的多屏幕显示器808,以实现大屏幕显示。多屏幕显示控制装置800包括串接的m张单卡,并可以一机壳包装所述m张单卡。各级单卡以usb接口链接,且有用于同步与复

位的前、后级同步接口810。各级单卡以图像处理器负责多个显示器的画面播放。用户可透过主机802上执行的人机接口(如,gui),设定如何驱动该些单卡。

123.一种实施方式中,使用者供应作业系统(如windows10)4k或者8k画面,由作业系统视为一个"大画面"经usb接口804传递给多屏幕显示控制装置800驱动多屏幕显示器808。如此设计是将多屏幕显示器808虚拟为完整的超大屏幕驱动,以虚拟显示器的方式上报作业系统,让它以为多屏幕显示器808是一个4k或者8k显示器。所述显卡驱动,等同于一般显卡驱动,把作业系统提供的图像,展现到视为单一完整屏幕的多屏幕显示器808上。所述虚拟画面同一般显示器画面,可以复制(使多组大萤幕显示同影像),也可以拓展(使影像拓展到多组大萤幕上)。

124.在视频墙方案中,主机802可安装有一个视频墙配置软件,目的是把大画面切割为a x b个小画面后通过usb输出。同时这个配置软件,可更负责边框消除,旋转等功能。

125.一种使用情境下,多屏幕显示控制装置800上电后,主机802以及多屏幕显示控制装置800之间的usb线才接上。多屏幕显示控制装置800为热插入装置。

126.说明之,单卡之间的同步接口插拔实现热插入。单卡经前、后级同步接口接上后(前级单卡的后级同步接口504接上后级单卡的前级同步接口508),切换成时脉同源会使得m级单卡一起复位,故正常运作。

127.虽然本发明已以较佳实施例揭示如上,然其并非用以限定本发明,任何熟悉本技术领域者,在不脱离本发明的精神和范围内,当可做些许更动与润饰,因此本发明的保护范围当以权利要求书界定者为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1