链路层-PHY接口适配器的制作方法

链路层

‑

phy接口适配器

1.本专利申请要求于2020年5月21日提交的美国临时专利申请no.63/028,412的权益,该美国临时专利申请全文以引用方式并入本文。

技术领域

2.本公开涉及计算系统,并且具体而言(但并非排他地)涉及计算机接口。

背景技术:

3.半导体处理和逻辑设计的进展已经许可增大集成电路设备上可以存在的逻辑单元的量。作为必然结论,计算机系统配置已经从系统中的单个或多个集成电路演进到个体集成电路上存在的多个核心、多个硬件线程和多个逻辑处理器、以及集成在这样的处理器内的其他接口。处理器或集成电路典型地包括单个物理处理器管芯,其中该处理器管芯可以包括任何数量的核心、硬件线程、逻辑处理器、接口、存储器、控制器集线器等。随着处理能力与计算系统中的设备的数量一起增长,插座和其他设备之间的通信变得更加关键。因此,互连已经从更传统的主要应对电通信的多点总线成长为便于快速通信的完全成熟的互连架构。不幸地,由于对将来处理器在更高速率下消费的需求,对现有互连架构的能力提出了对应需求。互连架构可以基于多种技术,包括快速外围部件互连(pcie)、通用串行总线等。

附图说明

4.图1示出了包括互连架构的计算系统的实施例。

5.图2示出了包括分层堆栈的互连架构的实施例。

6.图3示出了将在互连架构内产生或接收的请求或分组的实施例。

7.图4示出了用于互连架构的发射机和接收机对的实施例。

8.图5示出了包括通过链路耦合的主机处理器和加速器的计算系统的示例性实施方式。

9.图6示出了包括两个或更多个互连的处理器设备的计算系统的示例性实施方式。

10.图7示出了包括分层堆栈的设备的示例性端口的图示。

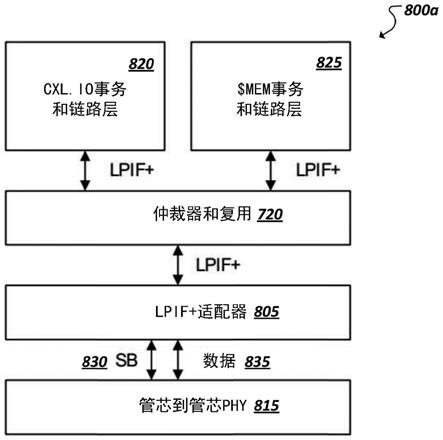

11.图8a

‑

图8c是示出了利用示例性适配器的接口的示例性实施方式的简化块图。

12.图9是示出了示例性适配器的简化块图。

13.图10是示出从示例性适配器到示例性phy的信令的简化块图。

14.图11是示出从示例性phy到示例性适配器的信令的简化块图。

15.图12是示出了示例性链路层到phy接口标准的示例性状态机的图示。

16.图13是示出了与时钟门控信号交换(handshake)相关联的信令的图示。

17.图14是示出与通过示例性适配器接口的数据传输相关联的信令的图示。

18.图15是示出与暂停信号交换相关联的信令的图示。

19.图16a

‑

图16f示出了表示使用示例性适配器的管芯之间的示例性信令的简化流程

图。

20.图17示出了用于包括多核处理器的计算系统的块图的实施例。

21.图18示出了用于计算系统的块图的另一实施例。

具体实施方式

22.在以下描述中,阐述了许多具体细节(例如,特定类型的处理器和系统配置、特定硬件结构、特定架构和微架构细节、特定寄存器配置、特定指令类型、特定系统部件、特定测量/高度、特定处理器流水线级和操作等的示例),以便提供对本公开的透彻理解。然而,对于本领域技术人员将显而易见的是,不一定采用这些具体细节来实践本发明。在其他实例中,没有详细地描述公知的部件或方法(例如,特定的和替代性的处理器架构、用于所描述的算法的特定逻辑电路/代码、特定固件代码、特定互连操作、特定逻辑配置、特定制造技术和材料、特定编译器实施方式、特定代码形式的算法表示、特定断电和门控技术/逻辑以及计算机系统的其他具体操作细节),以避免不必要地使本公开难以理解。

23.尽管可以参考在诸如计算平台或微处理器的特定集成电路中的能量节约和能量效率来描述以下实施例,但是其他实施例也适用于其他类型的集成电路和逻辑器件。本文所描述的实施例的类似技术和教导可以应用于其他类型的电路或半导体器件,其也可以受益于更好的能量效率和能量节约。例如,所公开的实施例不限于台式计算机系统或ultrabooks

tm

。并且还可以用于其他设备,例如,手持设备、平板式计算机、其他薄型笔记本、片上系统(soc)设备和嵌入式应用。手持设备的一些示例包括蜂窝电话、互联网协议设备、数字相机、个人数字助理(pda)和手持pc。嵌入式应用典型地包括微控制器、数字信号处理器(dsp)、片上系统、网络计算机(netpc)、机顶盒、网络中心、广域网(wan)交换机或可以执行下面教导的功能和操作的任何其他系统。此外,本文所描述的装置、方法和系统不限于物理计算设备,而是还可以涉及用于能量节约和效率的软件优化。

24.随着计算系统的发展,其中的部件变得更加复杂。因此,用于在部件之间耦合和通信的互连架构的复杂度也在增加,以确保针对最佳部件操作满足带宽要求。此外,不同的市场细分要求互连架构的不同方面适合市场的需要。例如,服务器要求更高的性能,而移动生态系统有时能够牺牲整体性能以节约功率。然而,大多数交换结构的唯一目的是以最大功率节约来提供可能的最高性能。下面讨论了多种互连,这些互连将潜在地受益于本文所描述的解决方案的方面。

25.一种互连交换结构架构包括快速外围部件互连(pci)(pcie)架构。pcie的主要目标是使得来自不同供应商的部件和设备能够在开放式架构中互操作,从而跨越多个市场细分:(台式的和移动的)客户端、(标准的和企业的)服务器以及嵌入式和通信设备。快速pci是针对各种未来的计算和通信平台定义的高性能的通用i/o互连。某些pci属性(例如,其使用模型、加载

‑

储存架构和软件接口)已经通过其修订版进行维护,而先前的并行总线实现方式已经由高度可扩展的完全串行接口取代。快速pci的最近的版本利用点对点互连、基于交换机的技术和分组协议中的发展,以递送新的性能和特征水平。快速pci支持的高级特征中的一些包括功率管理、服务质量(qos)、热插拔/热交换支持、数据完整性和错误处理。

26.参考图1,示出了由互连一组部件的点对点链路组成的交换结构的实施例。系统100包括与控制器集线器115耦合的处理器105和系统存储器110。处理器105包括任何处理

元件,例如,微处理器、主机处理器、嵌入式处理器、协处理器或其他处理器。处理器105通过前端总线(fsb)106耦合到控制器集线器115。在一个实施例中,fsb 106是如下面所描述的串行点对点互连。在另一实施例中,链路106包括符合不同的互连标准的串行、差分互连架构。

27.系统存储器110包括任何存储器设备,例如,随机存取存储器(ram)、非易失性(nv)存储器或可由系统100中的设备访问的其他存储器。系统存储器110通过存储器接口116耦合到控制器集线器115。存储器接口的示例包括双倍数据速率(ddr)存储器接口、双通道ddr存储器接口和动态ram(dram)存储器接口。

28.在一个实施例中,控制器集线器115是快速外围部件互连(pcie或pcie)互连层级中的根集线器、根联合体或根控制器。控制器集线器115的示例包括芯片组、存储器控制器集线器(mch)、北桥、互连控制器集线器(ich)、南桥和根控制器/集线器。术语芯片组经常指代两个物理上分离的控制器集线器,即,存储器控制器集线器(mch)耦合到互连控制器集线器(ich)。注意,当前系统经常包括与处理器105集成的mch,而控制器115以与下面所描述的方式类似的方式与i/o设备通信。在一些实施例中,可选地通过根联合体115来支持对等路由。

29.这里,控制器集线器115通过串行链路119耦合到交换机/桥120。输入/输出模块117和121(也可以称为接口/端口117和121)包括/实施分层协议堆栈以提供控制器集线器115与交换机120之间的通信。在一个实施例中,多个设备能够耦合到交换机120。

30.交换机/桥120将来自设备125的分组/消息向上游(即,沿着层级朝向根联合体向上)路由到控制器中心115,并且将来自处理器105或系统存储器110的分组/消息向下游(即,沿着层级远离根控制器向下)路由到设备125。在一个实施例中,交换机120被称为多个虚拟pci到pci桥设备的逻辑组件。设备125包括要耦合到电子系统的任何内部或外部设备或部件,例如,i/o设备、网络接口控制器(nic)、插入卡、音频处理器、网络处理器、硬盘驱动器、储存设备、cd/dvd rom、监视器、打印机、鼠标、键盘、路由器、便携式储存设备、火线设备、通用串行总线(usb)设备、扫描仪和其他输入/输出设备。通常在pcie中,诸如设备之类的日常用语被称为端点。尽管没有具体示出,但是设备125可以包括pcie到pci/pci

‑

x桥,以支持旧式的pci设备或其他版本的pci设备。pcie中的端点设备通常被分类为旧式的集成端点、pcie集成端点或根联合体集成端点。

31.图形加速器130也通过串行链路132与控制器集线器115耦合。在一个实施例中,图形加速器130耦合到与ich耦合的mch。然后,将交换机120以及因此i/o设备125耦合到ich。i/o模块131和118还用于实现分层协议堆栈以在图形加速器130与控制器集线器115之间进行通信。类似于上面关于mch的讨论,图形控制器或图形加速器130本身可以集成在处理器105中。应当认识到,图1中示出的部件(例如,105、110、115、120、125、130)中的一个或多个可以被增强以执行、储存和/或体现用于实施本文所描述的特征中的一个或多个的逻辑。

32.转到图2,示出了分层协议堆栈的实施例。分层协议堆栈200包括任何形式的分层通信堆栈,例如,快速路径互连(qpi)堆栈、pcie堆栈、下一代高性能计算互连堆栈或其他分层堆栈。尽管紧接着下面参考图1

‑

图4进行的讨论涉及pcie堆栈,但是相同的概念可以应用于其他互连堆栈。在一个实施例中,协议堆栈200是pcie协议堆栈,其包括事务层205、链路层210和物理层220。接口(例如,图1中的接口117、118、121、122、126和131)可以表示为通信

协议堆栈200。作为通信协议堆栈的表示也可以称为实施/包括协议堆栈的模块或接口。

33.快速pci使用分组以在部件之间传送信息。在事务层205和数据链路层210中形成分组以将信息从发送部件运送到接收部件。当发送的分组流经其他层时,利用在这些层处处理分组所必需的附加信息来对发送的分组进行扩展。在接收侧,发生相反的过程,并且分组从其物理层220表示变换为数据链路层210表示,并且(针对事务层分组)最终变换为可以由接收设备的事务层205处理的形式。

34.事务层

35.在一个实施例中,事务层205用于提供设备的处理核心与互连架构(例如,数据链路层210和物理层220)之间的接口。就这一点而言,事务层205的主要责任是对分组(即,事务层分组或tlp)的组装和拆分。转换层205典型地管理针对tlp的基于信用的流控制。pcie实施分离事务,即,请求和响应按时间分离的事务,从而在目标设备收集针对响应的数据时允许链路运送其他业务。

36.此外,pcie利用基于信用的流控制。在该方案中,设备在事务层205中通告接收缓冲器中的每一个的初始信用量。在链路的相对端处的外部设备(例如,图1中的控制器集线器115),对由每个tlp消耗的信用的数量进行计数。如果事务没有超过信用限制,则该事务可以被发送。在接收到响应后,将恢复信用量。信用方案的一个优点是,只要没有达到信用限制,则信用返还的延迟将不会影响性能。

37.在一个实施例中,四个事务地址空间包括配置地址空间、存储器地址空间、输入/输出地址空间和消息地址空间。存储器空间事务包括用于将数据传送到存储器映射位置/从存储器映射位置传送数据的读取请求和写入请求中的一个或多个。在一个实施例中,存储器空间事务能够使用两种不同的地址格式,例如,短地址格式(例如,32位地址)或长地址格式(例如,64位地址)。配置空间事务用于访问pcie设备的配置空间。针对配置空间的事务包括读取请求和写入请求。消息事务被定义以支持pcie代理之间的带内通信。

38.因此,在一个实施例中,事务层205组装分组报头/有效载荷206。可以在pcie规范网站处的pcie规范中找到当前分组报头/有效载荷的格式。

39.快速参考图3,示出了pcie事务描述符的实施例。在一个实施例中,事务描述符300是用于运送事务信息的机制。就这一点而言,事务描述符300支持对系统中的事务的标识。其他潜在用途包括跟踪对默认事务排序的修改以及事务与信道的关联。

40.事务描述符300包括全局标识符字段302、属性字段304和信道标识符字段306。在所示的示例中,全局标识符字段302被描绘为包括本地事务标识符字段308和源标识符字段310。在一个实施例中,全局事务标识符302对于所有未完成的请求是唯一的。

41.根据一种实现方式,本地事务标识符字段308是由请求代理生成的字段,并且本地事务标识符字段308对于对该请求代理而言要求完成的所有未完成请求是唯一的。此外,在该示例中,源标识符310唯一地标识pcie层级内的请求者代理。因此,本地事务标识符308字段连同源id 310一起提供层级域内的事务的全局标识。

42.属性字段304指定事务的特性和关系。就这一点而言,属性字段304潜在地用于提供允许对事务的默认处理进行修改的附加信息。在一个实施例中,属性字段304包括优先级字段312、保留字段314、排序字段316和非窥探(no

‑

snoop)字段318。这里,优先级子字段312可以由启动程序修改以向事务指派优先级。保留属性字段314被保留用于将来使用或供应

商定义的使用。可以使用保留属性字段来实施使用优先级或安全属性的可能的使用模型。

43.在该示例中,排序属性字段316用于供应传达可以修改默认排序规则的排序类型的可选信息。根据一个示例实现方式,排序属性“0”表示要应用的默认排序规则,其中,排序属性“1”表示放宽排序,其中写入可以在相同方向上传递写入,并且读取完成可以在相同方向上传递写入。窥探属性字段318用于确定事务是否被窥探。如图所示,信道id字段306标识与事务相关联的信道。

44.链路层

45.链路层210(也称为数据链路层210)用作事务层205与物理层220之间的中间级。在一个实施例中,数据链路层210的责任是提供用于在链路的两个部件之间交换事务层分组(tlp)的可靠机制。数据链路层210的一侧接受由事务层205组装的tlp,应用分组序列标识符211(即,标识号或分组号),计算并应用错误检测码(即,crc 212),并且将经修改的tlp提交给物理层220以用于跨物理到外部设备的传输。

46.物理层

47.在一个实施例中,物理层220包括逻辑子块221和电子块222,以将分组物理地发送到外部设备。这里,逻辑子块221负责物理层220的“数字”功能。就这一点而言,逻辑子块包括用于准备用于由物理子块222传输的传出信息的发送部分,以及用于在将接收到的信息传递到链路层210之前标识并准备接收到的信息的接收机部分。

48.物理块222包括发射机和接收机。发射机由逻辑子块221供应符号,发射机将该符号串行化并发送到外部设备上。接收机被供应有来自外部设备的经串行化的符号,并且将接收到的信号变换为位流。位流被解串行化并且供应给逻辑子块221。在一个实施例中,采用8b/10b传输码,其中发送/接收十位符号。这里,特殊符号用于利用帧223对分组进行组帧。此外,在一个示例中,接收机还提供从传入串行流恢复的符号时钟。

49.如上面所陈述的,尽管参考pcie协议堆栈的特定实施例讨论了事务层205、链路层210和物理层220,但是分层协议堆栈不限于此。实际上,可以包括/实施任何分层协议。作为示例,表示为分层协议的端口/接口包括:(1)用于组装分组的第一层(即,事务层);用于对分组进行排序的第二层(即,链路层);以及用于发送分组的第三层(即,物理层)。作为具体示例,使用公共标准接口(csi)分层协议。

50.接下来参考图4,示出了pcie串行点对点交换结构的实施例。尽管示出了pcie串行点对点链路的实施例,但是串行点对点链路不限于此,因为串行点对点链路包括用于发送串行数据的任何传输路径。在所示的实施例中,基本pcie链路包括两个低电压差分驱动信号对:发送对406/412和接收对411/407。因此,设备405包括用于将数据发送到设备410的发送逻辑406以及用于从设备410接收数据的接收逻辑407。换言之,在pcie链路中包括两个发送路径(即,路径416和417)以及两个接收路径(即,路径418和419)。

51.传输路径指代用于传输数据的任何路径,例如,传输线路、铜线路、光线路、无线通信信道、红外通信链路或其他通信路径。两个设备(例如,设备405与设备410)之间的连接被称为链路(例如,链路415)。链路可以支持一个通道——每个通道表示差分信号对的集合(一对用于发送,一对用于接收)。为了扩展带宽,链路可以聚合由xn表示的多个通道,其中n是任何支持的链路宽度,例如,1、2、4、8、12、16、32、64或更宽。在一些实现方式中,每个对称通道包含一个发送差分对和一个接收差分对。不对称通道可以包含不相等的比率的发送对

和接收对。一些技术可以利用对称通道(例如,pcie),而其他技术(例如,displayport)可以不利用对称通道并且甚至可以仅包括发送对或仅包括接收对,以及其他示例。

52.差分对指代用于发送差分信号的两个传输路径,例如,线路416和417。作为示例,当线路416从低电压电平切换到高电压电平(即,上升沿)时,线路417从高逻辑电平驱动到低逻辑电平(即,下降沿)。差分信号潜在地展示出更好的电特性,例如,更好的信号完整性(即,交叉耦合、电压过冲/下冲、振铃等)。这允许更好的时序窗口,从而实现更快的传输频率。

53.多种互连架构和协议可以利用本文论述的概念。随着计算系统和性能要求的发展,对互连交换结构和链路实施方式的改善一直在开发中,包括基于或利用pcie元件或其他旧式互连平台的互连。在一个示例中,已经开发了计算快速链路(cxl),从而提供了被设计成加快下一代数据中心性能的改善的高速cpu到设备和cpu到存储器互连,以及其他应用。cxl保持cpu存储器空间和附接设备上的存储器之间的存储器一致性,这允许资源共享以用于更高性能、减小的软件堆栈复杂性以及更低的总系统成本,以及其他示例性优点。cxl实现了主机处理器(例如,cpu)和一组工作载荷加速器(例如,图形处理单元(gpu)、现场可编程门阵列(fpga)器件、张量和矢量处理器单元、机器学习加速器、特定构建的加速器解决方案、以及其他示例)之间的通信。实际上,cxl被设计成提供用于高速通信的标准接口,因为加速器正越来越多用于在支持新兴计算应用(例如人工智能、机器学习和其他应用)中补充cpu。

54.cxl链路可以是低延迟、高带宽的离散或封装上链路,其支持一致性、存储器访问和输入/输出(i/o)协议的动态协议复用。除其他应用之外,cxl链路可以使加速器能够访问作为高速缓存代理和/或主机系统存储器、以及其他示例的系统存储器。cxl是被设计成支持广阔范围的加速器的动态多协议技术。cxl提供了丰富的协议集合,其包括类似于pcie的i/o语意(cxl.io)、高速缓存协议语意(cxl.cache)和通过离散或封装上链路的存储器存取语意(cxl.mem)。基于特定的加速器使用模型,可以启用全部cxl协议或仅协议的子集。在一些实施方式中,cxl可以构建于成熟、广泛采用的pcie基础结构(例如,pcie 5.0),从而利用pcie物理和电接口来提供包括i/o的区域中的高级协议、存储器协议(例如,从而允许主机处理器与加速器器件共享存储器)、以及一致性接口。

55.转到图5,示出了简化块图500,其示出了利用cxl链路550的示例性系统。例如,链路550可以将主机处理器505(例如,cpu)互连到加速器器件510。在本示例中,主机处理器505包括一个或多个处理器核心(例如,515a

‑

b)和一个或多个i/o设备(例如,518)。可以提供主机存储器(例如,560)与主机处理器(例如,在同一封装或管芯上)。加速器器件510可以包括加速器逻辑单元520,并且在一些实施方式中,可以包括其自己的存储器(例如,加速器存储器565)。在本示例中,主机处理器505可以包括实施一致性/高速缓存逻辑525和互连逻辑(例如,pcie逻辑530)的电路。还可以提供cxl复用逻辑(例如,555a

‑

b)以使得能够复用cxl协议(例如,i/o协议535a

‑

b(例如,cxl.io)、高速缓存协议540a

‑

b(例如,cxl.cache)、以及存储器存取协议545a

‑

b(cxl.mem)),由此使得能够通过在主机处理器505和加速器器件510之间的链路550以复用方式发送所支持的协议(例如,535a

‑

b、540a

‑

b、545a

‑

b)中的任一个的数据。

56.在一些实施方式中,可以与遵循cxl的链路合作利用flex bus

tm

端口以灵活地调整

器件来与各种其他器件(例如,其他处理器器件、加速器、开关、存储器件等)互连。flex bus端口是在统计上被配置为支持pcie或cxl链路(以及潜在地还有其他协议和架构的链路)的灵活的高速端口。flex bus端口允许设计为在通过高带宽封装外链路提供固有pcie协议或cxl之间选择。应用于端口处的协议的选择可以在启动时间期间经由自动协商来发生,并且基于插入到插槽中的器件。flex bus使用pcie电部件,从而使其与pcie重定时器兼容,并且遵循针对插入卡的标准pcie形状因数。

57.转到图6,(在简化块图600中)示出了利用flex bus端口(例如,635

‑

640)以实施cxl(例如,615a

‑

b、650a

‑

b)和pcie链路(例如,630a

‑

b)从而将各种器件(例如,510、610、620、625、645等)耦合到主机处理器(例如,cpu 505、605)的系统的示例。在本示例中,系统可以包括通过处理器间链路670(例如,利用ultrapath interconnect(upi)、infinity fabric

tm

或其他互连协议)互连的两个cpu主机处理器器件(例如,505、605)。每个主机处理器器件505、605可以耦合到本地系统存储器块560、660(例如,双倍数据速率(ddr)存储器件),该本地系统存储器块经由存储器接口(例如,存储器总线或其他互连)耦合到相应的主机处理器505、605。

58.如上所述,cxl链路(例如,615a,650b)可以用于互连各种加速器器件(例如,510,610)。因此,对应的端口(例如,flex bus端口635、640)可以被配置为(例如,cxl模式选定)使得能够建立cxl链路并将对应的主机处理器器件(例如,505、605)互连到加速器器件(例如,510、610)。如本示例中所示,flex bus端口(例如,636、639)或其他类似可配置的端口可以被配置为实施通用i/o链路(例如,pcie链路)630a

‑

b而非cxl链路,以将主机处理器(例如,505、605)互连到i/o设备(例如,智能i/o设备620、625等)。在一些实施方式中,可以例如通过如下来扩展:连接的加速器器件(例如,510、610)的存储器(例如,565、665)、或经由实施在flex bus端口(637、638)上的对应的cxl链路(例如,650a

‑

b)连接到(一个或多个)主机处理器505、605的存储器扩展器器件(例如,645)、以及其他示例性实施方式和架构。

59.图7是简化块图,其示出了用于实施cxl链路的示例性端口架构700(例如,flex bus)。例如,flex bus架构可以被组织为多个层以实施由端口支持的多种协议。例如,该端口可以包括事务层逻辑(例如,705)、链路层逻辑(例如,710)和物理层逻辑(例如,715)(例如,全部或部分实施在电路中)。例如,可以将事务(或协议)层(例如,705)细分成事务层逻辑725和逻辑730,事务层逻辑725实施基础pcie事务层755的pcie事务层755和cxl事务层增强760(用于cxl.io),并且逻辑730实施用于cxl链路的高速缓存(例如,cxl.cache)和存储器(例如,cxl.mem)协议。类似地,可以提供链路层逻辑735以实施基础pcie数据链路层765和表示pcie数据链路层765的增强版本的cxl链路层(用于cxl.io)。cxl链路层710还可以包括高速缓存和存储器链路层增强逻辑740(例如,用于cxl.cache和cxl.mem)。

60.继续图7的示例,除其他示例性实施方式之外,cxl链路层逻辑710可以与cxl仲裁/复用(arb/mux)逻辑720接口连接,这会交织来自两个逻辑流(例如,pcie/cxl.io和cxl.cache/cxl.mem)的流量。在链路训练期间,事务和链路层被配置为在pcie模式或cxl模式中操作。在一些实例中,除了其他示例之外,主机cpu可以支持pcie或cxl模式的实施方式,而其他器件(例如加速器)可以仅支持cxl模式。在一些实施方式中,端口(例如,flex bus端口)可以利用基于pcie物理层(例如,pcie电phy 750)的物理层715。例如,flex bus物理层可以被实施为收敛的逻辑物理层745,基于链路训练过程期间的替代模式协商的结果,

收敛的逻辑物理层745可以在pcie模式或cxl模式中操作。在一些实施方式中,物理层可以支持多个信令速率(例如,8gt/s、16gt/s、32gt/s等)和多个链路宽度(例如,x16、x8、x4、x2、x1等)。在pcie模式中,由端口700实施的链路可以完全符合固有pcie特征(例如,如pcie规范中定义的),而在cxl模式中,链路支持针对cxl定义的所有特征。因此,除了其他示例之外,flex bus端口可以提供点到点互连,该点到点互连可以传输固有pcie协议数据或动态多协议cxl数据,以通过pcie电器件提供i/o、一致性和存储器协议。

61.cxl i/o协议cxl.io为i/o设备提供不一致的载荷/储存接口。cxl.io中的事务类型、事务分组格式化、基于信用的流控制、虚拟信道管理和事务排序规则可以遵循pcie定义的全部或一部分。cxl高速缓存一致性协议cxl.cache将设备和主机之间的事务定义为若干请求,每个请求具有至少一个相关联的响应消息,并且有时具有数据传输。接口由每个方向上的三个信道构成:请求、响应和数据。

62.cxl存储器协议cxl.mem是处理器和存储器之间的事务接口,并且在跨管芯进行通信时使用cxl的物理层和链路层。cxl.mem可以用于多个不同的存储器附接选项,包括在存储器控制器位于主机cpu中时、在存储器控制器在加速器器件内时、或者在存储器控制器被移动到存储器缓冲器芯片时、以及其他示例。cxl.mem可以应用于涉及不同的存储器类型(例如,易失性、持久等)和配置(例如,平坦、层级等)以及其他示例性特征的事务。在一些实施方式中,主机处理器的一致性引擎可以使用cxl.mem请求和响应与存储器接口连接。在该配置中,cpu一致性引擎被视为cxl.mem主设备,而mem设备被视为cxl.mem从属设备。cxl.mem主设备是负责获取cxl.mem请求(例如,读取、写入等)的代理,而cxl.mem从属设备是负责响应于cxl.mem请求(例如,数据、完成等)的代理。在从属设备为加速器时,cxl.mem协议假设存在设备一致性引擎(dcoh)。假设这个代理负责实施一致性相关功能,例如基于cxl.mem命令的设备高速缓存的窥探以及元数据字段的更新。在元数据由设备附接的存储器支持的实施方式中,可以由主机使用来实施针对cpu的粗略窥探滤波器,以及其他示例性用途。

63.在一些实施方式中,可以提供接口以将实施链路层(例如,710)的电路或其他逻辑单元(例如,知识产权(ip)块或其他硬件元件)耦合到实施物理层(例如,715)协议的至少一部分的电路或其他逻辑单元(例如,ip块或其他硬件元件)。例如,基于逻辑phy接口(lpif)规范的接口定义链路层控制器、模块或其他逻辑单元与实施逻辑物理层(“逻辑phy”或“logphy”)的模块之间的公共接口,以针对通往物理互连的接口促进一个或多个链路层和物理层之间的互操作性、设计和验证重复使用,例如在图7的示例中。此外,如图7的示例中所示,可以用逻辑(例如,735、740)实施接口以同时实施和支持多种协议。此外,在这样的实施方式中,可以在链路层(例如,710)和物理层(例如,715)之间提供仲裁和复用层(例如,720)。在一些实施方式中,多种协议实施方式中的每个块(例如,715、720、735、740)可以经由独立的lpif接口(例如,780、785、790)与其他块接口连接。在支持分叉的情况下,每个分叉端口可以类似具有其自己独立的lpif接口,以及其他示例。

64.尽管本文论述的示例可以参考基于lpif的链路层

‑

逻辑phy接口的使用,但应当理解,本文论述的细节和原理可以同样适用于非lpif接口。同样,尽管一些示例可能参考公共链路层

‑

逻辑phy接口将phy耦合到实施cxl或pcie的控制器的使用,但其他链路层协议也可以利用这样的接口。类似地,尽管一些参考可以是对于flex bus物理层做出的,但在一些实

施方式中可以同样采用其他物理层逻辑并利用公共链路层

‑

逻辑phy接口,例如,如本文论述的,以及在本公开的范围内的其他示例性变化。

65.多芯片封装(mcp)技术的进展正在允许在同一封装内包括多个硅管芯。针对短距离而优化的高密度、低延迟管芯到管芯互连能够实现极低的位错误率(ber)(例如,好于1e

‑

18)。这样一来,这些互连典型地省略了串行器/解串行器(serdes)电路的开销以及与分组迹线传输相关的同步,并且还省略了逻辑phy中复杂的链路训练和状况状态机(ltssm)的开销。

66.各种不同的协议(例如,cxl、pcie、多路径互连(upi)、管芯中互连(idi)等)将受益于一般逻辑phy接口,以能够使用管芯到管芯互连,其中一般逻辑phy接口(或适配器)充当传送机构,所述传送机构提取用于初始化、电力管理和链路训练的信号交换。例如,传统逻辑phy实施方式可能对每种不同的协议要求与传统逻辑phy的定制信号交换。在改善的实施方式中,可以提供适配器电路以实施一般逻辑phy,其允许通过各种不同的管芯到管芯交换结构块传送上方协议层(例如,链路层)。适配器可以使得能够通过使用公共链路层到phy接口协议的子集的管芯到管芯接口(例如,lpif)传送原始位流。潜在地,任何管芯到管芯电接口可以通过提供此类适配器来利用此类接口。在一些实施方式中,适配器可以利用现有链路层控制器已经被配置为与其交互操作的定义的公共链路层到phy接口(例如,lpif)的子集(例如,用于pcie/flexbus/r

‑

link logphy的lpif等),以及其他示例性用途和优点。

67.转到图8a

‑

图8c,示出了简化块图800a

‑

c,其示出了利用适配器块(例如,805)辅助在各种链路层块和各种管芯到管芯phy块之间实施公共接口的接口的示例性实施方式。可以提供示例性适配器(例如,805)以对将通过管芯到管芯接口815发送的数据进行终止、修复和启动。例如,可以在封装上提供两个或更多个管芯,其中管芯到管芯互连815(例如,实施为同一封装上的高带宽管芯到管芯phy ip块)充当封装上的两个管芯之间的接口。适配器805可以提供有状态机逻辑以支持针对管芯

‑

管芯环境的简化状态集并在其之间转变。此外,适配器可以包括逻辑,以为将用于建立链路、提供电力管理和促进状态转变(以及其他示例性特征)的各种信号交换定义有效率的边带信道(例如,830)。这样的适配器设备可以提供一般且不知协议的管芯

‑

管芯接口,其包括带内数据信道(例如,835)和边带信道(例如,830)。适配器可以用于支持简化逻辑phy,这可能导致接口的更低的延迟和更低的功率,同时由于用于管芯

‑

管芯接口的可能的密集i/o,实现每毫米的管芯岸线(或边缘)的显著更高的带宽。此外,适配器可以支持由多种协议同时使用以允许这样的带宽可缩放,以及其他示例性优点。

68.如图8a

‑

图8c中所示,各种实施方式可以利用示例性适配器805(例如,基于公共链路层到phy接口(例如,lpif)),可以提供示例性适配器805以实施能够通过管芯到管芯phy 815发送和接收公共链路层到phy接口的数据(例如,lpif数据)的定义接口。链路层可以具有一个或多个功能管(例如,820、825),其中每个管对应于实施的协议。在一些实施方式中,例如图8a中所示,来自每个管820、825的流量可以与单个共享的lpif适配器805接口连接。此外,在一些实施方式中,例如图8a的示例中,可以在多协议链路层(例如,包括链路层控制器820、825)和适配器块805之间实例化arb/mux 720,其中在来自不同管(例如,820、825)的流量之间对arb/mux 720进行仲裁以驱动到适配器805。适配器可以终止和/或修复公共链路层到phy接口的数据以用于通过管芯到管芯phy(例如,815)进行传输。适配器805还可以

协调与链路层的各种信号交换以用于电力管理(pm)和时钟门控。在适用于错误/重置/电力管理传播时,适配器805还可以执行与远程管芯的信号交换,以及其他示例性特征。简而言之,如图8a

‑

图8c的示例中所示,使用基于lpif的适配器805允许已经或固有地支持lpif的链路层元件无缝地连接到用于pcie/cxl的逻辑phy或用于管芯到管芯传输的lpif适配器,其中lpif适配器实施极轻量级逻辑phy以用于管芯到管芯通信。

69.lpif适配器805用于通过多管芯接口发送原始协议流以用于管芯到管芯操作。在一些实施方式中,管芯到管芯phy 815被实施为简化的高密度管芯到管芯phy,从而实现比常规管芯到管芯phy更低的延迟和功率性能,以及其他示例。lpif适配器805可以包括用于和phy 815接口连接的数字逻辑单元。适配器805可以为管芯到管芯传输实施显著简化的逻辑phy。lpif适配器805可以根据lpif接口促进信号交换,同时传输原始数据位。lpif适配器805可以实施通往phy 815的边带信道830以交换适配器到适配器信号交换。这些信号交换也可以经由通过分配对于lpif适配器是唯一(并且未被协议使用)的特定分组/微片的主带来完成。

70.图8a示出了在arb/mux设备720和管芯到管芯phy 815之间提供接口的lpif适配器805的示例性实施方式。arb/mux电路720可以包括通往多个链路层功能管(通过对应的逻辑(例如,820、825)提供)中的每一个的lpif接口。arb/mux电路720可以额外地包括单个lpif接口以耦合到单个lpif适配器(例如,805)。在其他实施方式中,arb/mux电路可以被省略,例如图8b的示例中所示。在图8b的示例中,可以提供多个链路层控制器(例如,820、825),其与专用适配器实例(例如,805、805’)接口连接,而不是被复用到相同的lpif适配器,这在链路层管和管芯到管芯phy 815之间提供接口和逻辑phy。在图8a

‑

图8b的示例中,存在管芯到管芯phy的单个集群(例如,原子单元、或者管芯到管芯phy的集群,使得集群内的所有信号被固有地同步)。

71.可以提供多个lpif适配器(例如,805、805’),例如,以促进更高带宽的应用(例如,从而发送cxl.io和cxl.cache/cxl.mem数据的并行传输)。例如,在图8c中,可以通过提供多个管芯到管芯phy接口(例如,815、815’)来将带宽加倍(或以其它方式倍增)。相应的适配器(例如,805、805’)可以在链路层控制器(例如,820、825)和对应的管芯到管芯phy块(例如,815、815’)之间提供对应的逻辑phy和接口。在其他实例中,可以提供单个适配器作为逻辑phy实施方式以及通往多个管芯到管芯phy块(例如,815、815’)的接口。在本示例中,可以(例如,利用边带或其他信道(例如,830))耦合管芯到管芯phy块(例如,815、815’)以实现管芯到管芯phy块(例如,815、815’)之间的额外同步,以及其他示例性特征和实施方式。管芯到管芯phy(例如,815、815’)的不同集群之间的同步示出lpif数据宽度不需要约束(tied off)到管芯到管芯集群宽度。此外,应当理解,图8a

‑

图8c中所示的示例是简化示例,并且仅表示潜在的实施方式的小部分,其可以利用提供通往管芯到管芯phy的接口的适配器(例如,本文所述的)。

72.可以在适配器设备和链路层元件之间定义各种信号和交互。此外,在一些实施方式中,可以定义边带信道(例如,830)以执行与远程管芯(例如,远程管芯上的对应适配器)的辅助通信。在一些实例中,可以分配唯一的微片/分组以用于lpif适配器与远程管芯的lpif适配器通信。例如,互连管芯上的适配器之间的通信(例如,边带信号交换或专用分组)可以用于链路建立和操作。适配器可以利用在链路层到phy接口(例如,lpif)中定义的信号

子集来实施适配器轻量级逻辑phy。例如,可以省略一些信号,因为在一些管芯到管芯应用中,一旦进行操作,就可以不需要链路的重新训练(恢复)。此外,可以将适配器的范围扩展到包括使用对应的链路层到phy接口定义的机构的适配器。适配器和phy块(例如,管芯到管芯phy)之间的信令可以是灵活的和/或实施方式特定的,其中适配器被配置为根据特定的管芯到管芯phy设计而进行通信。

73.在一些实施方式中,lpif适配器和对应的phy块可以使用单个或多个实例化而随着数据宽度进行缩放。在这样的情况下,可以在phy中实施跨多个实例化的同步。也可以基于phy实施方式来缩放数据传输速比(gear ratio)。这样可以允许桥接管芯在不同频率下操作,以及其他示例性应用。示例性lpif适配器可以支持串行化/解串行化、或简单节流逻辑以确保通过不同的频率传递时不丢失数据。在一些实施方式中,如果需要的话,适配器还可以实施、包括或以其它方式实例化跨fifo队列的时钟。例如,可以使用对应的链路层到phy接口(例如,lpif中的pl_trdy)中定义的信号中的一个来控制对链路层的反向压力,以及其他示例。此外,在一些实施方式中,例如,适配器可以支持纠错以用于额外的链路保护,从而确保特定的ber要求,以及其他示例。可以在phy块和适配器的任一个(或两者)中实施纠错,以及其他示例性特征和实施方式。

74.在一些实施方式中,特定管芯上的链路层到phy接口的每个实例可以在相同的时钟频率下并在相同的功率域内操作。如果使用不同的时钟频率或时钟源,可以利用额外的fifo以用于时钟交叉。如果使用不同的功率域,则可以利用电压隔离,以及其他示例性特征。此外,链路层逻辑和对应的适配器块可以在相同的reset域内。次级侧适配器时钟(例如,phy时钟)可以从与初级侧时钟(lpif时钟)相同的锁相环(pll)电路导出。在一些实施方式中,适配器可以被配置使得适配器的一些或所有部分处于常导通功率域中,以能够(例如,经由边带或主带通信)从低功率状态唤醒,以及其他示例性特征。

75.转到图9,示出了示例性适配器的简化块图900。图9的示例示出了具有lpif接口的lpif适配器以用于促进两个链路层管905、910(例如,一个管905用于cxl.io,并且另一个管910用于cxl.cache/mem)。相应的链路层控制器可以包括用于实施适当的(一个或多个)接口(例如,lpif接口)以与适配器805通信的逻辑。适配器的部件可以实施在硬件电路、固件、软件或其组合中。在一种示例性实施方式中,适配器可以实施虚拟链路状态机(lsm)915a、b和对应的逻辑。虚拟lsm逻辑单元915a、b(例如,实施在硬件电路和/或固件中)可以实施全部所需的信号交换和通往arb/mux或链路层控制器的有效/数据接口。可以在通过对应的边带逻辑单元920a、b促进的边带编码上发送用于各种状态转变的信号交换信号。边带逻辑单元920a、b可以根据由phy块815提供的边带接口促进信号交换。适配器可以额外地提供速比串行器电路930。例如,在图9的示例中,示出了x2速比串行器作为示例,其中该速比促进接口和phy数据速率的匹配。实际上,通过速比串行器930提供的速比基于phy数据速率。在一些实施方式中,如果比硅数据路径运行地快得多,phy可以包含额外的serdes逻辑以减少引脚数,以及其他示例性实施方式。

76.图10是示出了示例性适配器805(到phy块815(例如,管芯到管芯phy))的发送数据路径的简化块图1000。该数据路径可以包括用于发送实体带内数据(例如,源自链路层或其他更高级逻辑(例如,由控制器1035实施))的发送数据通道1015以及用于发送流标识符以标识与带内数据相关联的协议的流通道1020。在一些实施方式中,适配器可以支持并发送

两种有效信号:数据有效1005和信道有效1010。在向phy 815发送带内数据(通过1015)或边带(通过发送边带通道1020)时,可以使信道有效1010生效。发送数据有效1005以标识通过数据通道1015发送数据(而使信道有效1010也生效)。

77.图11是示出了示例性适配器(来自phy块815)的接收器数据路径的简化块图1100。类似于发送数据路径的功能,适配器接收逻辑被配置为接收并解码有效的数据有效1105和信道有效1110信号,并通过接收数据通道1115接收带内数据,通过流通道1120发送对应于带内数据的流标识符信息,并通过接收边带通道1125接收边带数据。在一些实施方式中,phy块815可以内部包含serdes逻辑以分别在传输之前/之后对数据提高采样/降低采样。

78.图12示出了表示由对应的适配器设备支持的示例性链路层到phy接口(例如,lpif)的链路状态的图1200。该状态机示出了可允许的物理层状态状况(pl_state_sts)转变。在一些实例中,由对应的链路层到phy接口定义的一些状态可以被适配器实施方式省略。状态可以包括活动链路状态(例如,1205)、功率管理或低功率链路状态(例如,l1(和关联子状态)1210、l2(1215)等),以及其他示例性状态。在一些实施方式中,适配器可以实施重新训练状态(例如,1220)作为满足lpif信号交换所需的虚拟状态而实际上不重新训练phy。在重新训练是phy要求的实例中,可以增强适配器以将phy重新训练传播到链路层。额外的状态可以包括重置1225和链路重置状态1230、链路错误状态(例如,1235),以及其他示例性状态和实施方式。

79.如上所述,在一些实施方式中,除了(并独立于实施数据信道和接口的其他信道的物理通道)之外,适配器设备可以支持适配器和phy之间的边带信道(例如,可以通过所述边带信道在封装的相应管芯上的适配器之间传递边带信号)。在一个示例中,边带信道可以被实施为8通道边带(或不同宽度的信道)以实现对应的管芯之间的信号交换。边带可以在与实际数据总线相同的数据下操作,这可以简化时钟,以及其他示例性优点。在一些实例中,为了在边带上提供额外的链路保护,可以使用简单的secded方案,以及其他示例性实施方式。在替代性实施方式中,例如通过专用微片或其他实施方式可以代替地在带内促进通过特定phy块连接的管芯上的适配器之间的通信。

80.以下表1示出了针对示例性适配器的边带信道的示例性信号。在该表中,“req”指示请求以指示特定链路状态,并且sts指示进入到特定链路状态的状况响应或确认。此外,在本示例中,边带信道中使用的一部分位可以用作奇偶位(例如,位d4

‑

d7),例如以标识通过边带信道发送的边带消息的位错误,以及其他示例性特征:

[0081][0082]

表1:示例性边带编码

[0083]

如上所述,将与定位在链路层和phy之间的适配器接口连接的链路层控制器或arb/mux部件可以包括实施公共链路层到phy接口的逻辑,以将控制器或arb/mux耦合到适配器。此外,在arb/mux的情况下,可以提供额外的链路层到phy接口以将arb/mux耦合到馈送到arb/mux中的链路层协议代理(或管)中的每个。这些链路层到phy接口中的每个可以遵守针对接口的定义协议或标准。例如,在基于lpif的实施方式的情况下,链路层控制器和arb/mux和/或适配器之间的接口中的每个可以是lpif接口实例。可以根据链路层到phy接口的具体定义(例如,根据针对lpif接口的lpif规范)来实施若干信号、状态机、信号交换和其他协议特征。适配器可以同样地支持这些接口,不过可以在与物理phy(例如,管芯到管芯phy设备)接口连接时仅利用总体特征和信号的子集。

[0084]

例如,表2指示在lpif下定义的示例性信号并标识出适配器在其与phy接口连接时在多大程度(如果有的话)上采用或不采用每个信号。例如,可能仅有lpif信号的子集与管芯到管芯应用相关。例如,链路细分语意可能一般不适用于管芯到管芯接口,并且因此可以

假设仅存在单个端口。因此,在由表2所示的示例中,为了与链路层的无缝互操作性,pl_link_cfg可以始终反映x16配置。lpif适配器行为在管芯到管芯接口的上下文中描述适配器对具体基线lpif信号的功能。信号可以被约束、通过、配置为固定设置或用于接口信号交换,以及其他示例性用途。在一个示例中,所有信号都与lpif时钟(iclk)同步,除非在lpif规范中明确提到异步。此外,在表2的示例中,“pl_*”指示信号被驱动离开物理层到链路层,而“lp_*”指示信号被驱动离开链路层到物理层。

[0085]

[0086]

[0087]

[0088]

[0089]

[0090][0091]

表2:示例性基于lpif的适配器信号接口

[0092]

在一些示例中,在对应的示例性lpif适配器内利用lpif时钟(lclk)和phy时钟(例如,在一个示例中等于2x lclk)。边带可以在和数据相同的数据速率下操作。lclk和phy时钟两者可以由相同的pll产生。这样避免了时钟交叉fifo并减小了延迟,以及其他示例性优

点。

[0093]

在一些实施方式中,包括基于lpif的实施方式,可以通过时钟门控至少部分地促进示例性适配器处的功率管理。例如,在基于lpif的实施方式中,可以提供退出时钟门控req/ack机制,这是通过完整的信号交换促进的,如以下规则所述(并由图13的示例性时序图1300示出):

[0094]

1)可以通过使pl_exit_cg_req信号(1305)生效以通过接口的另一端上的实体请求时钟的非门控来(由适配器)请求时钟的非门控。仅在使lp_exit_cg_ack(1310)无效时,出现pl_exit_cg_req上的上升沿。

[0095]

2)其他部件使lp_exit_cg_ack生效以指示其未处于时钟门控状态并且准备好从物理层接收分组,一旦对lp_exit_cg_ack采样就可以在rx路径上发送分组。

[0096]

3)在进入活动状态之前将pl_exit_cg_req信号和lp_exit_cg_ack信号采样为生效。

[0097]

4)在lp_exit_cg_ack信号之前使pl_exit_cg_req信号无效。

[0098]

5)在退出重置或低功率状态(例如,l1、l2、重置或禁用)时,一旦生效,pl_exit_cg_req信号就保持生效,直到状态机转变除了低功率状态(例如,l1、l2或禁用)之外的状态。

[0099]

在从允许时钟门控的其他状态第一次进入活动状态、每次进入链路错误和每次进入活动状态之前去除时钟门控。例如,在低功率状态(例如l1、dapm、l2状态)中,可以利用功率管理时钟门控。在一些实施方式中,允许适配器和/或phy在任何时间发起exit_cg_req/ack信号交换,并且对应的链路层控制器将作出响应。例如,可以在初始启动期间发起和使用这种信号交换以确保链路层准备好接收用于pm退出的分组,或者物理层认为必要的任何其他条件。在某些协议中,对于在不实施时钟门控的两种状态之间的转变(例如,重新训练

‑

>活动转变),省略该信号交换也是允许的。在一些实施方式中,在初始化期间,适配器可以实施该信号交换以确保上层退出时钟门控,并在第一次进入活动状态之前准备好接收分组。

[0100]

在一些实施方式中,在上层逻辑正在发起pm退出时,则必须确保首先去除其pm和时钟门控。可以由上层通过将当前lp_state_req编码改变为新请求状态(除当前请求状态之外)来发起从l1退出的请求,可以由适配器使用lp_state_req中的改变来退出主干和本地时钟门控。在这种情况下,必须要保证lp_state_req信号的个体位没有故障,以避免多个时钟非门控请求。上层可以通过使lp_wake_req(与lclk可用性异步)生效来请求去除主干和本地时钟门控。适配器可以利用pl_wake_ack(与lclk同步)作出响应。当使pl_wake_ack生效时内部时钟非门控的范围可以是实施方式特定的,但此时lclk应当是可用的以能够从上层实现lpif接口转变。

[0101]

在一些实施方式中,可以在所实施的lpif中定义wake req/ack信号交换,例如:

[0102]

1)上层使lp_wake_req生效以通过适配器请求时钟的非门控。这可以与lp_state_req改变并行完成。

[0103]

2)适配器可以使pl_wake_ack生效以指示已经去除时钟门控。可以在lp_wake_req生效和pl_wake_ack生效之间执行至少一个时钟周期气泡(cycle bubble)。

[0104]

3)在使pl_wake_ack无效之前使lp_wake_req无效。在一些实施方式中,控制无效

的具体情形是上层的责任。例如,在为状态请求执行信号交换时,链路层控制器可以使lp_wake_req保持生效,直到其观察到期望的状态状况。

[0105]

4)lp_wake_req可能不是执行时钟门控的唯一考虑,例如,可以在执行主干和/或本地时钟门控之前考虑pl_state_sts和其他协议特定要求。

[0106]

在一些情况下,在适配器正在发起从功率管理状态退出时,其确保去除该上层时钟门控。发起从功率管理退出的对应信号交换可以通过使pl_exit_cg_req信号生效而利用退出时钟req/ack机制。可以保证pl_exit_cg req信号没有故障,以避免多个时钟非门控请求。在一些情况下,适配器可以发起进入链路错误状态(例如,基于适配器和/或phy上的错误检测逻辑),并且协同地确保去除上层时钟门控,以便向上层通知硬件故障。

[0107]

在一些实施方式中,lpif以pl_clk_req和lp_clk_ack信号交换的形式提供可选的机制,以允许适配器请求从上层去除时钟门控。这种机制可能在多个协议层在单个适配器实例上复用的状况中尤其有用,但仅由协议中的一个处理某些链路功能(例如,用于链路事件的中断生成)。在这种情况下,适配器可以使用pl_clk_req和lp_clk_ack信号交换以确保对应协议层已经去除其特定的时钟门控(例如,不论lpif状态如何)。例如:

[0108]

1)适配器可以使pl_clk_req生效以通过链路层请求去除时钟门控。这可以异步且独立于当前lpif状态来完成。

[0109]

2)链路层使lp_clk_ack生效以指示已经去除时钟门控。可以在pl_clk_req生效和lp_clk_ack生效之间执行至少一个时钟周期气泡。

[0110]

3)在lp_clk_ack之前使pl_clk_req无效。一旦这一信号交换所需的动作完成,控制无效的具体情形是逻辑phy的责任。

[0111]

4)pl_clk_req应当不是用于链路层执行时钟门控的唯一考虑,还可以在执行主干和/或本地时钟门控之前考虑pl_state_sts和其他协议特定要求。

[0112]

转到图14,示出了表示与lpif数据传输相关联的示例性信令的信号图1400。在一些实施方式中,在链路层控制器(通过适配器)向物理层发送数据时,在使lp_irdy(1420)(用于指示链路层准备好传输数据的信号)、pl_trdy(1425)(用于指示物理层准备好接受数据的信号)、以及lp_valid(1430)信号(用于指示在链路层到物理层上发送数据)生效的同时(在数据通道1015上)传输数据(例如,1405、1410、1415)。在一些情况下,关于何时能够使pl_trdy无效或在其再次生效之前其保持无效多少个周期,可以不定义限制,但在一些实施方式中,可以由适配器或phy执行或保证规则或策略以用于pl_trdy的无效和重新生效。类似协议和信号(例如,pl_valid用于指示在物理层到链路层上发送的数据生效)可以用于通过适配器从物理层到链路层传输数据。在一些实施方式中,在从物理层向链路层发送数据时,可以不执行反向压力机制,并可以在使pl_valid生效的任何时候传输数据,以及其他示例性特征。

[0113]

在一些示例中,lpif可以定义暂停req/ack信号交换机制以由物理层用于通过上层控制器中断分组传输(例如,在上层要求发送对准分组以通过接收链路层保证正确的帧对准和识别的条件下)。在退出活动状态时,可以使用暂停req/ack信号交换。还允许在整个信号交换中使用该机制并保持活动。例如,未利用暂停req/ack机制的链路层可以对stallreq进行浮点运算(flop)并将浮点运算输出反馈为stallack。lpif可以定义非阻挡stallreq信号交换(pl_nbstallreq/lp_nbstallack),以用于与对准相关的暂停,并且定义

pl_stallreq以用于状态转变。图15示出了表示暂停req/ack信号交换(使用暂停请求信号1505和暂停确认信号1510)的示例性实施方式的信令图1500。

[0114]

一些实施方式可以利用流信号以标识与通过接口发送的数据相关联的流id。流id可以标识多个不同的潜在支持协议中的哪个将与在接口上发送的对应数据相关联。例如,可以提供lp_stream[7:0]信号和pl_stream[7:0]信号以运送指示用于协议的流id编号的编码值。在一个示例中,该字段可以是8位宽,其中流id字段的定义是实施方式特定的。

[0115]

在一些实例中,流id信号可以关联或绑定到特定值(例如,其中链路层控制器不支持流id信号或者其中仅使用单一协议)。(例如,在两个方向上)允许链路层控制器提供流id信号。例如,在链路层和arb/mux或phy之间必须连接流id信号。流id编码的分配可以通过链路层完成,不并且pl_stream[7:0]的驱动程序可以对接收的流id解码并将分组转发到与接收的流id相关联的链路层。在连接到arb/mux时,arb/mux还可以包括用于意识到流id分配以及与链路层的关联的逻辑。

[0116]

lpif实施方式可以额外地定义状态请求和状况信号,以用于在基于lpif的状态机中定义的状态之间的转变中。例如,lp_state_req信号的值可以指示由链路层请求的lpif状态,并且信号pl_state_sts反映lpif接口的状态状况。

[0117]

一些实施方式还可以提供配置接口以促进信息在链路层和适配器之间的边带传输。例如,链路层可以使用该接口来读取适配器中的寄存器,以及其他示例性用途。

[0118]

图16a

‑

图16f示出了示例性信令图1600a

‑

f来示出涉及诸如上述的示例性适配器设备(例如,805a、805b)的各种事务流。可以在通过管芯到管芯phy 815互连的相应管芯(例如,1605a、1605b)上提供每个适配器805a、805b。一个或多个上层控制器(例如,链路层电路)可以提供在每个管芯上并通过链路层到phy接口1610a、1610b(例如,根据特定协议定义的接口)耦合到适配器设备(例如,805a、805b)中的相应适配器设备。在图16a

‑

图16f的示例中,提供了基于lpif的适配器,每个适配器耦合到相应的lpif接口(例如,1610a、1610b)。然而,应当理解,可以利用其他基于非lpif的适配器并实施与本文所述那些特征相同或类似的特征。

[0119]

图16a示出了从重置到活动的示例性启动流程。phy开始于重置状态(1611)并转变到活动l0(1612)中。例如,phy 815离开重置并执行训练以进入活动l0状态。可以在phy上定义并包括一个或多个线(和对应信号)(例如,dll锁定线/信号)以指示phy已经被训练到目标数据速率并且处于活动状态。每个适配器(例如,805a、805b)可以检测在phy上的信号并由此标识phy已经进入活动状态,并且初始地传输状态状况(state_sts)信号(1613)以指示在尝试通过凭借退出时钟门控请求exit_cg_req(1615、1616)来退出时钟门控从而发起lpif接口(例如,1610a、1610b)的激活之前,lpif接口当前处于重置。链路层可以发回退出时钟门控确认(1617、1618),其可能引起链路层被唤醒。在链路层中的一个(例如,“主要”管芯(例如,从应用角度、功率管理角度等,一个管芯可以是主要的,并且其他是“伴随的”)上的链路层)确定已经退出与功率管理相关的状况时,它可以用其他管芯通过phy 815发送请求以进入活动发送状态(state_req=active 1619)。适配器可以利用接口的将适配器(例如,805a)耦合到phy 815的边带信道来发送边带请求1620(以通过phy 815递送到其他适配器(例如,805b))以进入活动l0状态。在一些实施方式中,在phy 815退出重置到活动状态时,它保持在活动状态(例如,l0),直到转变回到重置。换言之,在phy 815上可能实际不进

入低功率、部分宽度或其他状态——相反,在phy保持活动的同时适配器维持不同的“状态”,以及其他示例性实施方式。

[0120]

继续图16a的示例,在接收边带请求1620以进入活动l0时,接收适配器805b可以向链路层发送第二时钟门控退出请求1621。在一些实施方式中,在可以定义重置之后发送第一时钟门控退出请求(例如,1615、1616)以不引起或不对应于活动状态请求。因此,在第二时钟门控退出请求1621之后,链路层控制器可以通过lpif接口1610b发送确认1622。作为响应,适配器805b可以发送边带状况信号1623,以标识适配器805b已经进入活动l0状态(例如,如lpif中定义的)。在本示例中,信号交换可以额外地涉及发送对应的活动状态请求1624的链路层,其使对应的适配器805b(向适配器805a)发送边带请求1625以进入活动l0。接收适配器同样可以在接收边带请求1625时向其对应的链路层控制器发送第二时钟门控退出请求1626。在从链路层接收确认1627时,适配器805a同样可以用边带状况信号1628作出响应。适配器在发送该信号1628时可以发送状态状况活动信号1629(具有无效的时钟门控退出信号和trdy信号的生效(其指示适配器准备好通过phy 815从链路层接收数据以用于传输))。对应地,在接收边带状况信号1628时,适配器805b可以产生类似的状态状况活动信号1630,以(通过lpif 1610b)向其对应的链路层控制器指示该链路是活动的并准备好来自链路层的数据。

[0121]

转到图16b,示出了从活动l0状态示例性地进入l1接口状态(例如,lpif l1状态)。在一些实施方式中,管芯和对应的适配器可以请求在活动和低功率状态之间转变,但在一些实施方式中,指定一个管芯作为“主要”或“伴随”可能隐含地或明确地符合使一个或另一个管芯始终发起状态转变中的至少一些的规则。例如,在一个示例中,边带请求将由伴随管芯发起以保持其与对应协议(例如,cxl、pcie等)的要求或惯例一致,其中主要管芯如果既从其链路层控制器(例如,1631)接收请求又从伴随管芯接收对应的边带请求通知(例如,1635)则等待采取动作,以及其他示例性规则、应用和流程。如上所述,在一些示例中,phy 815可以保持活动状态,尽管适配器和链路层在接口定义的链路状态之间(例如,在l0

‑

l1

‑

l2之间等)进行转变。phy 815可以依赖于动态时钟门控以用于节省功率,同时在活动中节省。在其他实施方式中,phy可以支持低功率状态,其可以由来自适配器的信号对应地进入接口定义的低功率状态来触发,以及其他示例性实施方式。在没有活动时,链路层可以对自身进行时钟门控,并允许完成其他系统级(例如,片上系统(soc))功率管理流程。

[0122]

在从链路层接收请求以进入l1(例如,state_req=l.1x(1632))时,适配器(例如,805b)可以响应于链路层停止发送额外数据的请求来发送暂停请求1633。链路层可以确认(在1634处)暂停请求1633。在接收该确认1634时,适配器可以通过其他适配器805a发送边带信号1635以请求进入l1,并使trdy信号(在1636处)无效以指示其不再从其对应的链路层接收数据。另一个适配器(例如,805a)在接收边带l1进入请求1635时,可以向其对应的链路层控制器发送其自己的暂停请求1637,这可以确认暂停(在1638处)以允许适配器805a也在其接口上(在1639处)使trdy无效。然后适配器805a可以通过发送指示进入l1的状态状况回复1640来确认转变到l1。适配器805a可以通过其lpif接口1610a向其链路层发送对应的状况消息1641。在接收状态状况回复1640时,适配器805a还可以通过其lpif接口1610b向其链路层发送状况消息1642。lpif接口(以及适配器和链路层)中的每个的状态现在全部可以处于定义的l1状态(例如,在1643、1644处),而phy保持活动l0(在1645处),以及其他示例性实

施方式。

[0123]

转到图16c,示出了从l1状态退出回到活动l0状态的示例。例如,在适配器805a、b和lpif接口1610a、b处于l1(1643、1644)时,链路层中的一个可以请求返回到活动l0状态(例如,在1646处)。在接收该请求1646时,适配器805b产生边带请求1647并通过phy 815发送边带请求1647以进入活动l0。另一个适配器805a可以接收边带请求1647并在lpif接口1610a上产生信号1648以指示用于退出时钟门控的请求,并指示重新训练的状态状况以转变回到l0。链路层可以向适配器805a返回用于退出时钟门控的请求的确认1649。作为响应,适配器805a可以发送进入l0的请求的边带状况确认1650。可以通过lpif接口1610a从链路层向适配器805a发送对应的活动状态请求1651,其可以导致适配器805a产生进入活动l0(1652)的边带请求并通过phy 815向另一个适配器805b发送该边带请求。适配器805b在接收边带请求1652时可以向其关联的链路层发送退出时钟门控请求1653。如其他管芯,链路层可以向适配器805b发送时钟门控退出确认1654。作为响应,适配器805b可以通过phy 815发送边带确认1655以指示该适配器也已经转变到l0状态。适配器805a、b中的每个可以向其关联的(一个或多个)链路层控制器发送状态状况信号(例如,1656、1657),连同使其时钟门控退出信号无效并使其trdy信号生效来指示该适配器准备好来自其关联的(一个或多个)链路层管的数据。

[0124]

转到图16d,示出了从活动发送状态(例如,l0)转变到低功率链路状态(例如,l1)的失败尝试的另一个示例。在图16d的示例中,类似于图16b中所示的信号交换尝试从lpif l0转变到l1。实际上,图16d的示例中所示的流程可以类似于图16b中所示的开始,其中伴随系统的链路层发信号到适配器805b以尝试将链路转变到低功率(l1)状态。然而,在图16d的示例中,“主要”管芯上的链路层可以通过适配器805a和phy 815向适配器805b发送下游数据分组(dp)1660,以用于递送到伴随链路层。因此,在适配器805a接收进入l1的边带请求1635时,它可以由于其必须发送的分组而确定其未被定位成进入l1。在本示例中,并非(例如,以边带状况信号的形式)向另一个适配器805b发送确认,上游适配器805a可以有效地忽略请求1635,从而引起链路状态保持在lpif l0。

[0125]

由于下游适配器805b使trdy=0(在1639处)无效与接收暂停确认1638一致,关联的链路层可以向适配器805b发送请求1661,以将链路恢复到活动状态(例如,基于标识将很快需要通过链路发送的数据)。适配器805b可以发送进入活动l0的对应边带请求1662。因为上游适配器已经保持在活动状态,并且其对应的lpif接口1610a是活动的,适配器805a可以立即通过phy 815向另一个下游适配器805b返回状态状况确认信号1663。作为响应,适配器805b可以使暂停请求信号无效并使trdy重新生效(在1664处)以指示适配器805b再次准备好(通过lpif接口1610b)从其对应的链路层管接受数据。然后可以(经由适配器805a)通过phy 815向另一管芯发送上游数据分组1665。在本示例中,对应于lpif适配器805a的控制器通过发送进入活动的请求1666而放弃l1进入请求,适配器805a用stall_req=0、trdy=1响应1667作出响应,从而允许进行其他上游数据分组1668,以及其他示例。

[0126]

尽管图16b

‑

图16d的示例涉及在适配器和phy设备(例如,管芯到管芯phy)之间向或从l1低功率状态转变的信令,但应当理解,可以将这些示例中示出的更一般化的原理和信令模式类似地应用于其他状态之间的转变,包括l1子状态、l2或其他低功率链路状态、以及可以在适配器兼容的对应的链路层到phy接口(例如,lpif或其他接口标准)中定义的其

他链路状态。

[0127]

转到图16e的示例,示出了在耦合到链路层到phy适配器设备(例如,805a、b)的phy(例如,815)的示例性实施方式中处理链路错误的示例。在本示例中,phy块可以配备有错误检测(例如,基于错误校正码)能力。在其他实例中,一个或两个适配器还可以或替代性地配备有错误检测功能,以标识通过连接两个管芯的链路发送或接收的数据(例如,分组数据)中的错误。在其他示例中,链路层控制器还可以或替代性地配备有错误检测能力,例如,致命错误检测(其可以通过向其适配器发送信号的lpif来指示)。

[0128]

在图16e中,链路处于活动(例如,l0)状态并且可以通过链路发送数据分组(例如,1675)。在本示例中,phy 815可以检测数据分组的一个或多个中的错误(例如,ecc错误)(例如,在1676处)并用信号向将接收包含错误的分组的适配器(例如,805b)通知1677该错误检测。响应于接收错误信号1677,适配器805b可以在传输中丢弃1678任何分组并发起进入链路错误状况。例如,适配器805b可以使退出时钟门控请求1679生效,这可以(在1680处)由对应的链路层控制器(例如,通过lpif接口1610b)确认。在接收确认1680时,适配器805b可以发送边带状况消息1681以向其他适配器805a指示链路错误。在接收链路错误状况信号1681时,另一个管芯上的伴随适配器805a同样可以通过类似的时钟门控退出信号交换1682发起进入链路错误状态(针对接口1610a)。在完成时钟门控退出信号交换(例如,在1679、1680、1682处)时,每个适配器可以状态状况消息并使trdy(例如,1683、1684)无效以停止分组传输(例如,以进入恢复或错误处理状态)。在一些实施方式中,信号1683、1684可以额外地指示错误类型和/或为所标识的链路错误发起的错误训练流程。

[0129]

转向图16f,示出了示例性链路重置流程,其可以用于从一个管芯(例如,主要管芯)向另一个管芯(例如,伴随管芯(类似于pcie中的热重置))传播重置。可以假设协议层在链路层发起链路重置流程之前静默。在图16f的示例中,在从主机链路层发送进入链路重置状态的请求1685时,链路处于活动l0状态。作为响应,适配器805a可以发送生效暂停请求信号(在1686处),链路层控制器可以(通过在lpif接口1610a上的信令)对该暂停请求信号进行确认1687。在接收暂停确认1687时,适配器805a可以在lpif接口1610a上使trdy无效1693,并通过phy 815发送边带请求1688以请求进入链路重置状态。伴随适配器805b可以接收边带请求1688并通过发起类似的暂停请求确认信号交换(例如,1689)来作出响应,在完成时,该信号交换使适配器805b通过phy 815利用边带状态状况信号1690作出响应,从而确认进入链路重置状态并发信号通知链路重置的状态状况以及在其lpif接口1610b上对trdy的无效(在1691处)。适配器805a在接收边带确认时可以通过lpif接口1610a发送状态状况信号1692。phy 815还可以进行到reset状态(例如,由于在其接口到soc处触发的片上系统(soc)reset流程)。

[0130]

注意,上面描述的装置、方法和系统可以在前述的任何电子设备或系统中实施。作为具体说明,以下附图提供了用于利用如本文所述的概念的示例性系统。例如,以下示例中示出的部件可以在独立管芯上实施,并且促成管芯到管芯连接的互连可以包括相应的链路层到phy适配器,例如上文所述,以促进通过管芯到管芯互连(例如,实施为专用管芯到管芯phy块)的数据传输。随着下面的系统被更详细地描述,从上面的讨论中公开、描述并重新讨论了许多不同的互连。并且显而易见的是,上面描述的发展可以应用于这些互连、交换结构或架构中的任一个。

[0131]

参考图17,描绘了包括多核心处理器的计算系统的框图的实施例。处理器1700包括任何处理器或处理设备,例如,微处理器、嵌入式处理器、数字信号处理器(dsp)、网络处理器、手持处理器、应用处理器、协处理器、片上系统(soc)或用于执行代码的其他设备。在一个实施例中,处理器1700包括至少两个核心——核心1701和核心1702,其可以包括不对称核心或对称核心(所示实施例)。然而,处理器1700可以包括任何数量的处理元件,这些处理元件可以是对称或不对称的。

[0132]

在一个实施例中,处理元件指代用于支持软件线程的硬件或逻辑。硬件处理元件的示例包括:线程单元、线程槽、线程、进程单元、上下文、上下文单元、逻辑处理器、硬件线程、核心和/或能够保持处理器的状态(例如,执行状态或架构状态)的任何其他元件。换言之,在一个实施例中,处理元件指代能够独立地与代码(例如,软件线程、操作系统、应用或其他代码)相关联的任何硬件。物理处理器(或处理器插座)典型地指代集成电路,该集成电路潜在地包括任何数量的其他处理元件,例如,核心或硬件线程。

[0133]

核心通常指代位于集成电路上的能够维持独立架构状态的逻辑,其中每个独立地维持的架构状态与至少一些专用执行资源相关联。与核心不同,硬件线程典型地指代位于集成电路上的能够维持独立架构状态的任何逻辑,其中独立地维持的架构状态共享对执行资源的访问权。如可以看出的,当某些资源是共享的并且其他资源专用于架构状态时,硬件线程和核心的命名法之间的界限重叠。然而通常地,核心和硬件线程被操作系统视为单独的逻辑处理器,其中操作系统能够单独地调度每个逻辑处理器上的操作。

[0134]

如图17中示出的,物理处理器1700包括两个核心——核心1701和核心1702。这里,核心1701和核心1702被认为是对称核心,即,具有相同配置、功能单元和/或逻辑的核心。在另一实施例中,核心1701包括乱序处理器核心,而核心1702包括有序处理器核心。然而,核心1701和核心1702可以从任何类型的核心(例如,本地核心、软件管理核心、适于执行本地指令集架构(isa)的核心、适于执行转换指令集架构(isa)的核心、共同设计的核心或其他已知的核心)中单独选择。在异构核心环境(即,非对称核心)中,可以利用某种形式的转换(例如,二进制转换)以在一个或两个核心上调度或执行代码。然而,为了进一步讨论,核心1701中示出的功能单元在下面进一步详细描述,因为核心1702中的单元在所描绘的实施例中以类似的方式操作。

[0135]

如所描绘的,核心1701包括两个硬件线程1701a和1701b,这些硬件线程也可以称为硬件线程槽1701a和1701b。因此,在一个实施例中,诸如操作系统之类的软件实体潜在地将处理器1700视为四个单独的处理器,即,能够同时执行四个软件线程的四个逻辑处理器或处理元件。如上面所提到的,第一线程与架构状态寄存器1701a相关联,第二线程与架构状态寄存器1701b相关联,第三线程可以与架构状态寄存器1702a相关联,并且第四线程可以与架构状态寄存器1702b相关联。这里,如上面所描述的,架构状态寄存器(1701a、1701b、1702a和1702b)中的每一个可以被称为处理元件、线程槽或线程单元。如所示的,架构状态寄存器1701a在架构状态寄存器1701b中被复制,因此能够针对逻辑处理器1701a和逻辑处理器1701b存储单独的架构状态/上下文。在核心1701中,还可以针对线程1701a和线程1701b复制其他较小的资源,例如,分配器和重命名器块1730中的指令指针和重命名逻辑。可以通过分区来共享一些资源,例如,重新排序/引退单元1735中的重新排序缓冲器、iltb 1720、加载/存储缓冲器和队列。其他资源(例如,通用内部寄存器、(多个)页表基址寄存器、

低级别数据高速缓存和数据tlb 1715、(多个)执行单元1740以及乱序单元1735的部分)是潜在地完全共享的。

[0136]

处理器1700通常包括其他资源,这些资源可以是完全共享的、通过分区共享的或由处理元件专用/专用于处理元件的。在图17中,示出了具有处理器的说明性逻辑单元/资源的纯示例性处理器的实施例。注意,处理器可以包括或省略这些功能单元中的任一个,以及包括未描绘出的任何其他已知的功能单元、逻辑或固件。如所示的,核心1701包括简化的、代表性的乱序(ooo)处理器核心。但是可以在不同的实施例中利用有序处理器。ooo核心包括用于预测要执行/采用的分支的分支目标缓冲器1720和用于存储用于指令的地址转换条目的指令转换缓冲器(i

‑

tlb)1720。

[0137]

核心1701还包括解码模块1725,该解码模块1725与获取单元1720耦合以对所获取的元素解码。在一个实施例中,获取逻辑包括分别与线程槽1701a、线程槽1701b相关联的单独的定序器。通常,核心1701与第一isa相关联,该第一isa定义/指定在处理器1700上可执行的指令。通常,作为第一isa的一部分的机器代码指令包括指令的一部分(称为操作码),该操作码引用/指定要执行的指令或操作。解码逻辑1725包括从其操作码识别这些指令并在流水线中传递经解码的指令以进行由第一isa定义的处理的电路。例如,如下面更详细讨论的,在一个实施例中,解码器1725包括被设计为或适于识别特定指令(例如,事务指令)的逻辑。由于解码器1725进行的识别,架构或核心1701采取特定的预定义动作来执行与适当指令相关联的任务。重要的是要注意,可以响应于单个或多个指令来执行本文所描述的任务、块、操作和方法中的任何一个;其中一些指令可能是新的或旧的指令。注意,在一个实施例中,解码器1726识别相同的isa(或其子集)。可替代地,在异构核心环境中,解码器1726识别第二isa(第一isa的子集或不同的isa)。

[0138]

在一个示例中,分配器和重命名器块1730包括用于保留资源(例如,用于存储指令处理结果的寄存器文件)的分配器。然而,线程1701a和线程1701b潜在地能够乱序执行,其中分配器和重命名器块1730还保留其他资源,例如,用于跟踪指令结果的重新排序缓冲器。单元1730还可以包括寄存器重命名器,以将程序/指令参考寄存器重命名为处理器1700内部的其他寄存器。重新排序/引退单元1735包括诸如上面提到的重新排序缓冲器、加载缓冲器和存储缓冲器之类的组件以支持乱序执行和乱序执行的指令的稍后有序引退。

[0139]

在一个实施例中,(多个)调度器和执行单元块1740包括用于调度执行单元上的指令/操作的调度器单元。例如,浮点指令在具有可用的浮点执行单元的执行单元的端口上被调度。还包括与执行单元相关联的寄存器文件以存储信息指令处理结果。示例性执行单元包括浮点执行单元、整数执行单元、跳转执行单元、加载执行单元、存储执行单元和其他已知的执行单元。

[0140]

较低级别数据高速缓存和数据转换缓冲器(d

‑

tlb)1750耦合到(多个)执行单元1740。数据高速缓存用于存储最近使用/操作的元素,例如,数据操作数,其潜在地保持在存储器一致性状态中。d

‑

tlb用于存储最近的虚拟/线性到物理地址转换。作为特定示例,处理器可以包括页表结构以将物理存储器分成多个虚拟页。

[0141]

这里,核心1701和核心1702共享对更高级别或更远的高速缓存(例如,与片上接口1710相关联的第二级高速缓存)的访问权。注意,更高级别或更远指代高速缓存级别增加或从(多个)执行单元进一步远离。在一个实施例中,更高级别高速缓存是最后一级数据高速

缓存——处理器1700上的存储器层级中的最后高速缓存——例如,第二或第三级数据高速缓存。然而,更高级别高速缓存不限于此,因为它可以与指令高速缓存相关联或包括指令高速缓存。迹线高速缓存——一种类型的指令高速缓存——相反可以在解码器1725之后耦合以存储最近解码的迹线。这里,指令潜在地指代宏指令(即,由解码器识别的通用指令),其可以解码为多个微指令(微操作)。

[0142]

在所描绘的配置中,处理器1700还包括片上接口模块1710。历史上,下面更详细描述的存储器控制器已经被包括在处理器1700外部的计算系统中。在这种场景中,片上接口1710用于与处理器1700外部的设备(例如,系统存储器1775、芯片组(通常包括用于连接到存储器1775的存储器控制器中心和用于连接外围设备的i/o控制器中心)、存储器控制器中心、北桥或其他集成电路)进行通信。并且在这种场景中,总线1705可以包括任何已知的互连,例如,多点总线、点对点互连、串行互连、并行总线、一致(例如,高速缓存一致)总线、分层协议架构、差分总线和gtl总线。

[0143]

存储器1775可以专用于处理器1700或者与系统中的其他设备共享。存储器1775的类型的常见示例包括dram、sram、非易失性存储器(nv存储器)和其他已知的存储设备。注意,设备1780可以包括图形加速器、与存储器控制器中心耦合的处理器或卡、与i/o控制器中心耦合的数据存储装置、无线收发器、闪存设备、音频控制器、网络控制器或其他已知的设备。

[0144]

然而,最近随着更多逻辑和设备被集成在诸如soc之类的单个管芯上,这些设备中的每一个可以合并在处理器1700上。例如,在一个实施例中,存储器控制器中心与处理器1700在同一封装和/或管芯上。这里,核心的一部分(核心上部分)1710包括一个或多个控制器,用于与诸如存储器1775或图形设备1780之类的其他设备相接合。包括用于与这种设备相接合的互连和控制器的配置通常被称为核心上(或非核心配置)。作为示例,片上接口1710包括用于片上通信的环形互连和用于片外通信的高速串行点对点链路1705。然而,在soc环境中,甚至更多的设备(例如,网络接口、协处理器、存储器1775、图形处理器1780和任何其他已知的计算机设备/接口)可以集成在单个管芯或集成电路上以提供具有高功能和低功耗的小形状因子。

[0145]

在一个实施例中,处理器1700能够执行编译器、优化和/或转换器代码1777以编译、转换和/或优化应用代码1776,以支持本文所描述的装置和方法或与其相接合。编译器通常包括用于将源文本/代码转换成目标文本/代码的程序或程序集。通常,利用编译器来编译程序/应用代码是在多个阶段和多遍中完成的,以将高级别编程语言代码变换为低级别机器或汇编语言代码。然而,单遍编译器仍然可以用于简单编译。编译器可以利用任何已知的编译技术并且执行任何已知的编译器操作,例如,词法分析、预处理、解析、语义分析、代码生成、代码变换和代码优化。

[0146]

较大的编译器通常包括多个阶段,但是大多数情况下这些阶段被包括在两个一般阶段中:(1)前端,即,通常在该处可以进行句法处理、语义处理和一些变换/优化,以及(2)后端,即,通常在该处进行分析、变换、优化和代码生成。一些编译器指代中间部分,其说明了编译器的前端与后端之间的界定的模糊处。因此,对编译器的插入、关联、生成或其他操作的引用可以在前述阶段或遍中的任何一个以及编译器的任何其他已知的阶段或遍中进行。作为说明性示例,编译器潜在地在编译的一个或多个阶段中插入操作、调用、函数等,例

如,在编译的前端阶段插入调用/操作,然后在变换阶段期间将调用/操作变换为较低级别的代码。注意,在动态编译期间,编译器代码或动态优化代码可以插入此类操作/调用,以及优化代码以便在运行时期间执行。作为特定说明性示例,可以在运行时期间动态地优化二进制代码(已编译的代码)。这里,程序代码可以包括动态优化代码、二进制代码或其组合。

[0147]

类似于编译器,诸如二进制转换器之类的转换器静态地或动态地转换代码以优化和/或转换代码。因此,对代码、应用代码、程序代码或其他软件环境的执行的引用可以指代:(1)动态地或静态地执行(多个)编译器程序、优化代码优化器或转换器,以编译程序代码、维护软件结构、执行其他操作、优化代码或转换代码;(2)执行包括操作/调用的主程序代码,例如,已经优化/编译的应用代码;(3)执行与主程序代码相关联的其他程序代码(例如,库),以维护软件结构、执行其他软件相关的操作或优化代码;或(4)其组合。

[0148]

现在参考图18,示出了根据本解决方案的实施例的第二系统1800的块图。如图18中示出的,多处理器系统1800是点对点互连系统,并且包括经由点对点互连1850耦合的第一处理器1870和第二处理器1880。处理器1870和1880中的每一个可以是处理器的某个版本。在一个实施例中,1852和1854是串行点对点一致(或非一致)互连交换结构的一部分。

[0149]

虽然仅示出了具有两个处理器1870、1880,但是应该理解的是,本发明的范围不限于此。在其他实施例中,一个或多个附加处理器可以存在于给定处理器中。

[0150]

处理器1870和1880被示为分别包括集成存储器控制器单元1872和1882。处理器1870还包括作为其总线控制器单元的一部分的点对点(p

‑

p)接口1876和1878;类似地,第二处理器1880包括p

‑

p接口1886和1888。处理器1870、1880可以使用p

‑

p接口电路1878、1888经由点对点(p

‑

p)接口1850交换信息。如图18中示出的,imc 1872和1882将处理器与相应的存储器(即,存储器1832和存储器1834)耦合,这些存储器可以是本地附接到相应处理器的主存储器的部分。

[0151]

处理器1870、1880各自使用点对点接口电路1876、1894、1886、1898经由单独的p

‑

p接口1852、1854与芯片组1890交换信息。芯片组1890还经由接口电路1892沿着高性能图形互连1839与高性能图形电路1838交换信息。

[0152]

共享高速缓存(未示出)可以被包括在任一处理器中或两个处理器外部;而经由p

‑

p互连与处理器连接,使得如果处理器被置于低功率模式,则任一处理器或两个处理器的本地高速缓存信息可以存储在共享高速缓存中。

[0153]

芯片组1890可以经由接口1896耦合到第一总线1816。在一个实施例中,第一总线1816可以是外围组件互连(pci)总线,或者诸如快速pci总线或另一第三代i/o互连总线之类的总线,但本公开的范围不限于此。

[0154]

如图18中示出的,各种i/o设备1814连同将第一总线1816耦合到第二总线1820的总线桥1818一起耦合到第一总线1816。在一个实施例中,第二总线1820包括低引脚计数(lpc)总线。在一个实施例中,各种设备与第二总线1820耦合,包括例如,键盘和/或鼠标1822、通信设备1827和存储单元1828(例如,磁盘驱动器或其他大容量存储设备,其通常包括指令/代码和数据1830)。此外,音频i/o 1824被示为与第二总线1820耦合。注意,其他架构是可能的,其中所包括的组件和互连架构不同。例如,除了图18的点对点架构,系统可以实现多点总线或其他这样的架构。

[0155]

计算系统可以包括组件的各种组合。这些组件可以实现为ic、其部分、分立电子设

备,或适配在计算机系统中的其他模块、逻辑、硬件、软件、固件或其组合,或者实现为以其他方式并入计算机系统的机箱内的组件。然而,应该理解,在其他实现方式中,可以省略所示出的组件中的一些组件,可以存在附加的组件,并且可以出现所示出的组件的不同布置。因此,上面描述的特征和部件可以在下面示出或描述的互连中的一个或多个互连的任何部分中实现。

[0156]

在一个实施例中,处理器包括微处理器、多核心处理器、多线程处理器、超低电压处理器、嵌入式处理器或其他已知的处理元件。在所示的实现方式中,处理器充当主处理单元和中央中心,用于与系统的各种组件中的许多组件通信。作为一个示例,处理器被实现为片上系统(soc)。作为具体的说明性示例,处理器包括基于architecture core

tm

的处理器(例如,i3、i5、i7)或可从intel公司(santa clara,ca)获得的另一这种处理器。然而,应理解,其他低功率处理器(例如,可从sunnyvale,ca的advanced micro devices公司(amd)获得的;来自sunnyvale,ca的mips technologies公司的基于mips的设计;从arm控股公司或其客户或者其被许可者或采用者许可的基于arm的设计)代替地可以存在于其他实施例中,例如,apple a5/a6处理器、qualcomm snapdragon处理器或ti omap处理器。注意,这种处理器的客户版本中的许多都是经修改和改变的;但是,这些处理器可以支持或识别执行如由处理器许可方阐述的所定义的算法的特定指令集。这里,微架构实现方式可能会改变,但处理器的架构功能通常是一致的。下面将进一步讨论关于处理器在一个实现方式中的架构和操作的特定细节,以提供说明性示例。

[0157]

在一个实施例中,处理器与系统存储器通信。作为说明性示例,这在实施例中可以经由多个存储器设备来实现以提供给定量的系统存储器。作为示例,存储器可以符合基于联合电子器件工程委员会(jedec)低功率双倍数据速率(lpddr)的设计,例如,根据jedec jesd 209

‑

2e(2009年4月发布)的当前lpddr2标准,或者被称为lpddr3或lpddr4的下一代lpddr标准,其将提供对lpddr2的扩展以增加带宽。在各种实现方式中,个体存储器设备可以具有不同的封装类型,例如,单管芯封装(sdp)、双管芯封装(ddp)或四管芯封装(13p)。在一些实施例中,这些设备直接焊接到主板上以提供较低轮廓的解决方案,而在其他实施例中,这些设备被配置为一个或多个存储器模块,这些存储器模块进而通过给定连接器耦合到主板。并且当然,其他存储器实现方式也是可能的,例如,其他类型的存储器模块,例如,不同种类的双列直插式存储器模块(dimm),包括但不限于microdimm、minidimm。在特定的说明性实施例中,存储器的大小在2gb和16gb之间,并且可以被配置为经由球栅阵列(bga)焊接到主板上的ddr3lm封装或lpddr2或lpddr3存储器。

[0158]

为了提供对诸如数据、应用、一个或多个操作系统等之类的信息的持久存储,大容量储存装置也可以耦合到处理器。在各种实施例中,为了实现更薄更轻的系统设计以及为了改进系统响应性,可以经由ssd实现该大容量存储装置。然而,在其他实施例中,大容量存储装置可以主要使用硬盘驱动器(hdd)来实现,其中较少量的ssd存储装置充当ssd高速缓存,以实现在断电事件期间对上下文状态和其他这样的信息的非易失性存储,从而可以在重新发起系统活动时发生快速上电。闪存设备可以例如经由串行外围接口(spi)耦合到处理器。该闪存设备可以提供对系统软件的非易失性存储,包括基本输入/输出软件(bios),以及系统的其他固件。

[0159]

在各种实施例中,系统的大容量储存装置由ssd单独实现或者实现为具有ssd高速

缓存的磁盘驱动器、光驱动器或其他驱动器。在一些实施例中,大容量存储装置实现为ssd或hdd以及恢复(rst)高速缓存模块。在各种实现方式中,hdd提供在320gb

‑

4太字节(tb)及以上之间的存储,而rst高速缓存利用容量为24gb

‑

256gb的ssd实现。注意,这种ssd高速缓存可以被配置为单级高速缓存(slc)或多级高速缓存(mlc)选项,以提供适当级别的响应性。在仅ssd选项中,模块可以容纳在各种位置,例如,在msata或ngff槽中。作为示例,ssd的容量范围为120gb

‑

1tb。

[0160]

各种外围设备可以经由低引脚计数(lpc)互连耦合到处理器。在所示的实施例中,各种组件可以通过嵌入式控制器耦合。这些组件可以包括键盘(例如,经由ps2接口耦合)、风扇和热传感器。在一些实施例中,触摸板也可以经由ps2接口耦合到ec。另外,诸如可信平台模块(tpm)(根据日期为2003年10月2日的可信计算组(tcg)tpm规范版本1.2)之类的安全性处理器也可以经由该lpc互连耦合到处理器。然而,应理解本公开的范围不限于此方面,并且对安全信息的安全处理和存储可以在另一受保护的位置(例如,安全性协处理器中的静态随机存取存储器(sram))进行,或者作为仅当受安全飞地(se)处理器模式保护时解密的加密数据二进制大对象。

[0161]

在特定实现方式中,外围端口可以包括高清晰度媒体接口(hdmi)连接器(其可以具有不同的形状因子,例如,全尺寸、迷你或微型);诸如根据通用串行总线修订版3.0规范(2008年11月)的全尺寸外部端口之类的一个或多个usb端口,当系统处于连接待机状态并插入到ac墙壁电源时,至少一个端口供电以对usb设备(例如,智能电话)充电。另外,还可以提供一个或多个thunderbolt

tm

端口。其他端口可以包括外部可访问的读卡器,例如,全尺寸sd

‑

xc读卡器和/或用于wwan的sim读卡器(例如,8引脚读卡器)。对于音频,可以存在具有立体声和麦克风能力(例如,组合功能)的3.5mm插孔,支持插孔检测(例如,仅支持使用盖板中的麦克风的耳机或使用电缆形式的麦克风的耳机)。在一些实施例中,该插孔可以在立体声耳机与立体声麦克风输入之间重新分配任务。另外,可以提供电源插孔以耦合到ac块。

[0162]

系统可以以各种方式与外部设备通信,包括无线地。在某些实例中,存在各种无线模块,其中的每个无线模块可以对应于针对特定无线通信协议配置的无线电。一种用于诸如近场之类的短距离的无线通信的方式可以是经由近场通信(nfc)单元,nfc单元在一个实施例中可以经由smbus与处理器通信。注意,经由该nfc单元,彼此非常接近的设备可以通信。例如,用户可以通过将两个设备紧密地适配在一起使得系统能够与另一(例如)便携式设备(例如,用户的智能电话)进行通信,并且使得能够传送诸如识别信息、支付信息之类的信息,诸如图像数据之类的数据等。还可以使用nfc系统来执行无线功率传送。

[0163]

使用本文描述的nfc单元,用户可以通过利用这种设备中的一个或多个设备的线圈之间的耦合来边对边地碰撞设备并且边对边地放置设备以用于近场耦合功能(例如,近场通信和无线功率传送(wpt))。更具体地,实施例提供具有策略性成形并放置的铁氧材料的设备,以提供线圈的更好耦合。每个线圈具有与其相关联的电感,可以结合系统的电阻、电容和其他特征来选择电感,以便针对系统实现共同的共振频率。

[0164]

此外,附加的无线单元可以包括其他短距离无线引擎,包括wlan单元和蓝牙单元。使用wlan单元,可以实现根据给定的电气和电子工程师协会(ieee)802.11标准的wi

‑

fi

tm

通信,同时经由蓝牙单元,可以发生经由蓝牙协议的短距离通信。这些单元可以经由例如usb链路或通用异步接收器发送器(uart)链路与处理器通信。或者这些单元可以根据快速外围

组件互连

tm

(pcie

tm

)协议经由互连耦合到处理器,例如,根据快速pci

tm

规范基础规范版本3.0(2007年1月17日公布),或诸如串行数据输入/输出(sdio)标准之类的另一这种协议。当然,这些外围设备(其可以配置在一个或多个插入卡上)之间的实际物理连接可以通过使ngff连接器适配于主板的方式。

[0165]

另外,例如根据蜂窝或其他无线广域协议的无线广域通信可以经由wwan单元发生,该wwan单元进而可以耦合到订户身份模块(sim)。另外,为了使得能够接收和使用位置信息,还可以存在gps模块。wwan单元和诸如相机模块之类的集成捕获设备可以经由给定的usb协议(例如,usb 2.0或3.0链路,或uart或i2c协议)进行通信。再次,这些单元的实际物理连接可以经由使ngff插入卡适配于在主板上配置的ngff连接器。

[0166]

在特定实施例中,无线功能可以例如以wifi

tm 802.11ac解决方案来模块化地提供(例如,与ieee 802.11abgn向后兼容的插入卡),以支持windows8cs。该卡可以配置在内部槽中(例如,经由ngff适配器)。附加模块可以提供蓝牙能力(例如,具有向后兼容性的蓝牙4.0)以及无线显示功能。另外,nfc支持可以经由分离的设备或多功能设备提供,并且作为示例可以放置在机箱的右前部分以易于访问。另外附加的模块可以是wwan设备,其可以提供对3g/4g/lte和gps的支持。该模块可以在内部(例如,ngff)槽中实现。可以针对wifi

tm

、蓝牙、wwan、nfc和gps提供集成天线支持,实现根据无线千兆比特(wigig)规范(2010年7月)从wifi

tm

到wwan无线电、无线千兆比特的无缝转变,反之亦然。

[0167]

如上所述,集成相机可以并入到盖板中。作为一个示例,该相机可以是高分辨率相机,例如,具有至少2.0兆像素(mp)的分辨率并且延伸到6.0mp或更高。

[0168]

为了提供音频输入和输出,可以经由数字信号处理器(dsp)实现音频处理器,该数字信号处理器可以经由高清晰度音频(hda)链路耦合到处理器。类似地,dsp可以与集成编码器/解码器(codec)和放大器通信,codec和放大器进而可以耦合到可以在机箱内实现的输出扬声器。类似地,放大器和codec可以耦合以接收来自麦克风的音频输入,在实施例中,麦克风可以经由双阵列麦克风(例如,数字麦克风阵列)来实现,以提供高质量的音频输入以便在系统内实现对各种操作的语音激活控制。还应注意,音频输出可以从放大器/codec提供给耳机插孔。

[0169]

在特定实施例中,数字音频编码解码器和放大器能够驱动立体声耳机插孔、立体声麦克风插孔、内部麦克风阵列和立体声扬声器。在不同的实现方式中,编码解码器可以集成到音频dsp中或者经由hd音频路径耦合到外围控制器中心(pch)。在一些实现方式中,除了集成立体声扬声器之外,还可以提供一个或多个低音扬声器,并且扬声器解决方案可以支持dts音频。

[0170]

在一些实施例中,处理器可以由外部电压调节器(vr)和集成在处理器管芯内部的多个内部电压调节器(称为完全集成的电压调节器(fivr))供电。在处理器中使用多个fivr使得能够将组件分组到分离的电源平面中,从而功率由fivr调节并仅提供给组中的那些组件。在功率管理期间,当处理器被置于特定低功率状态时,一个fivr的给定电源平面可以掉电或断电,而另一fivr的另一电源平面保持活动或完全供电。

[0171]

在一个实施例中,可以在一些深度睡眠状态期间使用维持电源平面来针对若干i/o信号使i/o引脚通电,例如,处理器与pch之间的接口,与外部vr的接口以及与ec的接口。该维持电源平面还对管芯上电压调节器供电,该管芯上电压调节器支持板载sram或在睡眠状

态期间存储处理器上下文的其他高速缓冲存储器。维持电源平面还用于使处理器的唤醒逻辑通电,该唤醒逻辑监测并处理各种唤醒源信号。

[0172]

在功率管理期间,当其他电源平面在处理器进入特定深度睡眠状态时掉电或断电时,维持电源平面保持通电以支持上面引用的组件。然而,这可能导致当不需要这些组件时不必要的功耗或耗散。为此,实施例可以提供连接待机睡眠状态以使用专用电源平面来维护处理器上下文。在一个实施例中,连接待机睡眠状态有助于使用pch的资源进行处理器唤醒,该pch本身可以与处理器一起存在于封装中。在一个实施例中,连接待机睡眠状态有助于维持pch中的处理器架构功能直到处理器唤醒,这使得能够关闭在深度睡眠状态期间先前保持通电的所有不必要的处理器组件,包括关闭所有时钟。在一个实施例中,pch包含时间戳计数器(tsc)和用于在连接待机状态期间控制系统的连接待机逻辑。用于维持电源平面的集成电压调节器也可以驻留在pch上。

[0173]

在实施例中,在连接待机状态期间,集成电压调节器可以用作专用电源平面,其在处理器进入深度睡眠状态和连接待机状态时保持通电以支持存储处理器上下文(例如,关键状态变量)的专用高速缓冲存储器。该关键状态可以包括与架构、微架构相关联的状态变量,调试状态和/或与处理器相关联的类似状态变量。

[0174]

可以在连接待机状态期间将来自ec的唤醒源信号发送到pch而不是处理器,从而pch而不是处理器可以管理唤醒处理。另外,tsc在pch中维护以有助于维持处理器架构功能。

[0175]

处理器中的功率控制可以导致增强的功率节省。例如,可以在核心之间动态地分配功率,个体核心可以改变频率/电压,并且可以提供多个深度低功率状态以实现非常低的功耗。另外,对核心或独立核心部分的动态控制可以通过在不使用组件时将组件断电来提供降低的功耗。

[0176]

在不同的实现方式中,诸如tpm之类的安全性模块可以集成到处理器中,或者可以是诸如tpm 2.0设备之类的分立设备。利用集成的安全性模块(也称为平台信任技术(ptt)),可以使能bios/固件以针对特定安全性特征公开特定硬件特征,包括安全指令、安全引导、防盗技术、身份保护技术、可信执行技术(txt)和可管理性引擎技术以及诸如安全键盘和显示器之类的安全用户接口。

[0177]

尽管已经关于有限数量的实施例描述了以上解决方案,但是本领域技术人员将理解由此产生的许多修改和变型。所附权利要求旨在覆盖落入本公开的真实精神和范围内的所有这些修改和变化。

[0178]

设计可以经历从创建到仿真到制造的各个阶段。表示设计的数据可以以多种方式表示设计。首先,如在仿真中有用,可以使用硬件描述语言或另一种功能描述语言来表示硬件。另外地,可以在设计过程的某些阶段产生具有逻辑和/或晶体管栅极的电路级模型。此外,大多数设计在某个阶段达到表示各种设备在硬件模型中的物理放置的数据级别。在使用常规半导体制造技术的情况下,表示硬件模型的数据可以是指定对于用于制造集成电路的掩模而言在不同掩模层上存在或不存在各种特征的数据。在设计的任何表示中,数据可以存储在任何形式的机器可读介质中。存储器或诸如磁盘之类的磁或光存储装置可以是用于存储经由光波或电波发送的信息的机器可读介质,该光波或电波被调制或以其他方式生成以发送这样的信息。当发送指示或携带代码或设计的电载波时,在执行对电信号的复制、

缓冲或重传的程度上,制作新的副本。因此,通信提供商或网络提供商可以将体现本公开的实施例的技术的诸如编码到载波中的信息之类的制品至少临时地存储在有形的机器可读介质上。

[0179]

如本文所使用的模块指代硬件、软件和/或固件的任何组合。作为示例,模块包括硬件(例如,微控制器),其与用于存储适合于由微控制器执行的代码的非暂时性介质相关联。因此,在一个实施例中,对模块的引用指代特别地被配置用于识别和/或执行要保持在非暂时性介质上的代码的硬件。此外,在另一实施例中,对模块的使用指代包括特别适合于由微控制器执行以执行预定操作的代码的非暂时性介质。并且,如可以推断的,在又一实施例中,术语模块(在该示例中)可以指代微控制器和非暂时性介质的组合。通常,示出为分离的模块界限通常变化并且潜在地重叠。例如,第一模块和第二模块可以共享硬件、软件、固件或其组合,同时潜在地保留一些独立的硬件、软件或固件。在一个实施例中,术语逻辑的使用包括硬件,例如,晶体管、寄存器或其他硬件(例如,可编程逻辑器件)。

[0180]

在一个实施例中,对短语“用于”或“被配置用于”的使用指代对装置、硬件、逻辑或元件进行布置、放在一起、制造、提供以售卖、导入和/或设计以执行指定或确定的任务。在该示例中,没有进行操作的装置或其元件仍“被配置用于”如果其被设计、耦合和/或互连以执行指定任务则执行所述指定任务。作为纯粹说明性的示例,逻辑门可以在操作期间提供0或1。但是“被配置用于”向时钟提供使能信号的逻辑门不包括可以提供1或0的每一个潜在的逻辑门。相反,逻辑门是以在操作期间1或0输出用于启用时钟的某种方式耦合的逻辑门。再次注意,对术语“被配置用于”的使用不要求操作,而是集中于装置、硬件和/或元件的潜在状态,其中在潜在状态下,装置、硬件和/或元件被设计为当装置、硬件和/或元件正在操作时执行特定任务。

[0181]

此外,在一个实施例中,对短语“能够/能够用于”和/或“可操作用于”的使用是指以这样的方式被设计为使得能够以指定方式使用装置、逻辑、硬件和/或元件的某种装置、逻辑、硬件和/或元件。如上文所提到的,在一个实施例中,对用于、能够用于或可操作用于的使用指代装置、逻辑、硬件和/或元件的潜在状态,其中装置、逻辑、硬件和/或元件没有在操作,但是以这样的方式被设计为使得能够以指定方式使用装置。

[0182]

如本文所使用的值包括数字、状态、逻辑状态或二进制逻辑状态的任何已知表示。通常,对逻辑电平、逻辑值(logic value)或逻辑上的值(logical value)的使用还称为对1和0的使用,其简单地表示二进制逻辑状态。例如,1指代高逻辑电平,并且0指代低逻辑电平。在一个实施例中,诸如晶体管或闪存单元之类的存储单元能够保持单个逻辑值或多个逻辑值。然而,已经使用了计算机系统中的值的其他表示。例如,十进制数十也可以表示为二进制值1010和十六进制字母a。因此,值包括能够保持在计算机系统中的信息的任何表示。

[0183]

此外,状态可以由值或值的部分表示。作为示例,诸如逻辑1之类的第一值可以表示默认或初始状态,而诸如逻辑0之类的第二值可以表示非默认状态。另外,在一个实施例中,术语重置和设置分别指代默认值或状态和更新后的值或状态。例如,默认值潜在地包括高逻辑值(即,重置),而更新后的值潜在地包括低逻辑值(即,设置)。注意,值的任何组合可以用于表示任意数量的状态。

[0184]

以下示例涉及根据本说明书的实施例。示例1是一种装置,包括:适配器,适配器包

括:耦合到特定设备的第一接口,其中将通过第一接口传递链路层数据;耦合到物理层(phy)设备的第二接口,其中phy设备包括多条线以实施链路的物理层,该链路将适配器经由phy设备耦合到另一适配器,并且第二接口包括:通过物理层传递链路层数据的数据信道;以及通过物理层在适配器和另一适配器之间传递边带消息的边带信道;以及实施用于链路的逻辑phy的电路。

[0185]

示例2包括示例1的主题,其中数据信道包括第一组引脚并且边带信道包括不同的第二组引脚。

[0186]

示例3包括示例1

‑

2中的任一项的主题,其中该特定设备包括以下中的一个:链路层控制器或用于复用多个链路层的数据的复用器。

[0187]

示例4包括示例3中的主题,其中该特定设备包括多个链路层控制器来实施多个不同的互连协议的链路层。

[0188]

示例5包括示例4中的主题,其中多个不同的互连协议包括基于快速外围部件互连(pcie)的协议。

[0189]

示例6包括示例4

‑

5中的任一项的主题,其中多个不同的互连协议包括计算快速链路(cxl)存储器协议、cxl高速缓存协议或cxl i/o协议中的两种或更多种。

[0190]

示例7包括示例1

‑

6中的任一项的主题,其中链路将第一管芯耦合到第二管芯,第一管芯将包括适配器,并且第二管芯将包括另一适配器。

[0191]

示例8包括示例1

‑

7中的任一项的主题,其中第一接口符合链路层到phy接口标准。

[0192]

示例9包括示例8的主题,其中该链路层到phy接口标准包括逻辑phy接口规范(lpif)接口。

[0193]

示例10包括示例8

‑

9中的任一项的主题,其中适配器还包括状态机电路,以实施状态机的由链路层到phy接口标准定义的至少一部分。

[0194]

示例11包括示例10的主题,其中状态机定义多个链路状态之间的转变,并且边带消息将用于在适配器和另一适配器之间协调多个链路状态之间的转变。

[0195]

示例12包括示例1

‑

11中的任一项的主题,其中第二接口还包括有效信道以指示正在通过第二接口发送有效数据。

[0196]

示例13包括示例12的主题,其中使有效信道生效以指示正在在数据信道上发送有效数据或者正在在边带信道上发送有效边带消息。

[0197]

示例14包括示例1

‑

13中的任一项的主题,其中第二接口还包括流信道以运送流信号,从而标识由在数据信道上发送的数据使用的特定协议。

[0198]

示例15是一种方法,包括:在适配器设备的第一接口处接收特定数据,其中第一接口基于链路层到phy接口标准,并且该特定数据基于链路层到phy接口标准,并且指示要转变到状态机中定义的活动链路状态的请求;在适配器设备的第二接口上发送请求边带信号,其中第二接口将适配器设备耦合到phy设备,第二接口包括数据信道和单独的边带信道,phy设备包括多个物理连接器以实施链路的物理层,并且边带信号将被发送到与phy设备耦合的另一适配器设备并指示要进入活动链路状态的请求;在第二接口的边带信道上从其他适配器设备接收确认边带信号以确认要进入活动链路状态的请求;在第一接口上发送信号以指示适配器设备准备好接收在链路上要传递的链路层数据;接收链路层数据;以及在第二接口的数据信道上传送链路层数据,以基于进入活动链路状态通过phy设备向另一

适配器设备传送链路层数据。

[0199]

示例16包括示例15的主题,还包括:在第二接口的边带信道上接收请求边带信号,其中所接收的请求边带信号指示要进入低功率链路状态的请求;在第一接口上传递一组信号以基于要进入低功率链路状态的请求而发起时钟门控;在第二接口的边带信道上发送确认边带信号以确认要进入低功率链路状态的请求;以及在适配器上从活动链路状态转变到低功率链路状态。

[0200]

示例17包括示例16的主题,其中phy设备在适配器转变到低功率链路状态之后保持在活动状态中。

[0201]

示例18包括示例15

‑

17中的任一项的主题,其中数据信道包括第一组引脚并且边带信道包括不同的第二组引脚。

[0202]

示例19包括示例15

‑

18中的任一项的主题,其中第一接口将适配器设备耦合到特定设备,并且该特定设备包括以下中的一个:链路层控制器或用于复用多个链路层的数据的复用器。

[0203]

示例20包括示例19的主题,其中该特定设备包括多个链路层控制器以实施多个不同互连协议的链路层。

[0204]

示例21包括示例20的主题,其中多个不同互连协议包括基于快速外围部件互连(pcie)的协议。

[0205]

示例22包括示例20

‑

21中的任一项的主题,其中多个不同的互连协议包括计算快速链路(cxl)存储器协议、cxl高速缓存协议或cxl i/o协议中的两种或更多种。

[0206]

示例23包括示例15

‑

22中的任一项的主题,其中链路将第一管芯耦合到第二管芯,第一管芯将包括适配器,并且第二管芯将包括另一适配器。

[0207]

示例24包括示例15

‑

23中的任一项的主题,其中链路层到phy接口标准包括逻辑phy接口规范(lpif)接口。

[0208]

示例25包括示例15

‑

24中的任一项的主题,其中适配器还包括状态机电路,以实施状态机的由链路层到phy接口标准定义的至少一部分。

[0209]

示例26包括示例25的主题,其中状态机定义多个链路状态之间的转变,并且边带消息将用于在适配器和另一适配器之间协调多个链路状态之间的转变。

[0210]

示例27包括示例15

‑

26中的任一项的主题,其中第二接口还包括有效信道以指示正在通过第二接口发送有效数据。

[0211]

示例28包括示例27的主题,其中使有效信道生效以指示正在在数据信道上发送有效数据或者正在在边带信道上发送有效边带消息。

[0212]

示例29包括示例15

‑

28中的任一项的主题,其中第二接口还包括流信道以运送流信号,从而标识由在数据信道上发送的数据使用的特定协议。

[0213]

示例30是一种系统,包括用于执行示例15

‑

29中的任一项的方法的模块(mean)。

[0214]

示例31包括示例30的主题,其中该模块包括其上储存有指令的储存介质,该指令可以由机器执行以使机器执行示例15

‑

29中的任一项的方法的至少一部分。

[0215]

示例32包括示例30的主题,其中模块包括硬件电路以执行示例15

‑

29中的任一项的方法的至少一部分。

[0216]

示例33是一种系统,包括:第一管芯,该第一管芯包括:实施协议的链路层的链路

层电路;适配器,该适配器包括:第一接口,其中与链路层电路相关联的链路层数据将通过第一接口进行传递;耦合到物理层(phy)设备的第二接口,其中phy设备包括多条线以实施链路的物理层,该链路经由phy设备将第一管芯耦合到第二管芯,并且第二接口包括:数据信道,该数据信道向phy设备传递链路层数据以便在链路上进行通信;以及边带信道,该边带信道在适配器和第二管芯上的另一适配器之间传递边带消息;以及实施用于链路的逻辑phy的电路。

[0217]

示例34包括示例33的主题,还包括:phy设备;以及第二管芯,其中第二管芯包括另一适配器,并且另一适配器包括相应的数据信道和相应的边带信道以用于耦合到phy设备。

[0218]

示例35包括示例33

‑

34中的任一项的主题,其中链路层电路包括第一链路层电路以用于实施第一互连协议的链路层,并且第一管芯还包括第二链路层电路以用于实施不同的第二互连协议的链路层。

[0219]

示例36包括示例35的主题,其中适配器包括第一适配器,并且管芯包括第二适配器以耦合在链路的第二链路层电路和物理层之间,其中第二适配器实施用于链路的逻辑phy的至少一部分。

[0220]

示例37包括示例35

‑

36中的任一项的主题,其中第一管芯还包括仲裁/复用(arb/mux)电路,以用于耦合到第一和第二链路层电路中的每个,并且arb/mux电路的输出被提供到适配器的第一接口。

[0221]

示例38包括示例35

‑

37中的任一项的主题,其中第一接口包括逻辑phy接口规范(lpif)接口,并且phy设备与协议无关。

[0222]

示例39包括示例38的主题,其中适配器还包括状态机电路以实施状态机的由链路层到phy接口标准定义的至少一部分。

[0223]

示例40包括示例39的主题,其中状态机定义多个链路状态之间的转变,并且边带消息将用于在适配器和另一适配器之间协调多个链路状态之间的转变。

[0224]

示例41包括示例33

‑

40中的任一项的主题,其中数据信道包括第一组引脚并且边带信道包括不同的第二组引脚。

[0225]

示例42包括示例33

‑

41中的任一项的主题,其中该特定设备包括以下中的一个:链路层控制器或用于复用多个链路层的数据的复用器。

[0226]

示例43包括示例42的主题,其中该特定设备包括多个链路层控制器以实施多个不同的互连协议的链路层。

[0227]

示例44包括示例43的主题,其中多个不同的互连协议包括基于快速外围部件互连(pcie)的协议。

[0228]

示例45包括示例43

‑

44中的任一项的主题,其中多个不同的互连协议包括计算快速链路(cxl)存储器协议、cxl高速缓存协议或cxl i/o协议中的两种或更多种。

[0229]

示例46包括示例33

‑

45中的任一项的主题,其中链路将第一管芯耦合到第二管芯,第一管芯将包括适配器,并且第二管芯将包括另一适配器。

[0230]

示例47包括示例33

‑

46中的任一项的主题,其中第二接口还包括有效信道以指示正在通过第二接口发送有效数据。

[0231]

示例48包括示例47的主题,其中使有效信道生效以指示正在在数据信道上发送有效数据或者正在在边带信道上发送有效边带消息。

[0232]

示例49包括示例33

‑

48中的任一项的主题,其中第二接口还包括流信道以运送流信号,从而标识由在数据信道上发送的数据使用的特定协议。

[0233]

上面所阐述的方法、硬件、软件、固件或代码的实施例可以经由存储在机器可访问、机器可读、计算机可访问或计算机可读介质上的、能够由处理元件执行的指令或代码来实现。非暂时性机器可访问/可读介质包括以诸如计算机或电子系统之类的机器可读的形式提供(即,存储和/或传输)信息的任何机制。例如,非暂时性机器可访问介质包括随机存取存储器(ram)(例如,静态ram(sram)或动态ram(dram));rom;磁或光存储介质;闪速存储器设备;电存储设备;光存储设备;声学存储设备;用于保持从暂时(传播)信号(例如,载波、红外信号、数字信号)接收到的信息的其他形式的存储设备(其用于区别于可以从其接收信息的非暂时性介质)等。

[0234]

用于对逻辑进行编程以执行本发明的实施例的指令可以存储在系统中的存储器(例如,dram、高速缓存、闪速存储器或其他存储装置)内。此外,可以经由网络或通过其他计算机可读介质的方式来分发指令。因此,机器可读介质可以包括用于以机器(例如,计算机)可读的形式存储或传输信息的任何机制,但不限于软盘、光盘、压缩盘只读存储器(cd

‑

rom)和磁光盘、只读存储器(rom)、随机存取存储器(ram)、可擦除可编程只读存储器(eprom)、电可擦除可编程只读存储器(eeprom)、磁卡或光卡、闪速存储器,或用于经由电、光、声学或其他形式的传播信号(例如,载波、红外信号、数字信号等)通过互联网传输信息的有形的机器可读存储装置。因此,计算机可读介质包括适合于以机器(例如,计算机)可读的形式存储或传输电子指令或信息的任何类型的有形机器可读介质。

[0235]

贯穿本说明书对“一个实施例”或“实施例”的引用表示结合该实施例描述的特定的特征、结构或特性包括在本发明的至少一个实施例中。因此,贯穿本说明书各处出现的短语“在一个实施例中”或“在实施例中”不一定指代同一实施例。此外,特定的特征、结构或特性可以以任何适合的方式组合在一个或多个实施例中。

[0236]

在前述说明书中,已经参考具体的示例性实施例进行了详细描述。然而,将显而易见的是,在不偏离如所附权利要求书中阐述的本发明的更宽泛的精神和范围的情况下,可以对其进行各种修改和改变。说明书和附图因此应被视为说明意义而非限制意义的。此外,对实施例和其他示范性语言的前述使用不一定指代同一实施例或同一示例,而是可以指代不同且独特的实施例以及潜在地指代同一实施例。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1