一种可重构芯片的内存耦合编译方法及系统与流程

[0001]

本发明涉及可重构处理器开发,应用于可重构编译器的编译器及编译过程。本发明具体涉及一种可重构芯片的内存耦合编译方法及系统。

背景技术:

[0002]

在基于llvm编译框架(low level virtual machine)编译框架的面向典型可重构处理器cgra的编译器编译过程中,其主要目标是将用户的应用程序通过可重构编译器的llvm编译框架前端通用的词法、语法和语义分析后,对中间表达式(ir,intermediate representation)进行优化后提取合适的数据流图,在通过任务划分和存储分配、算子调度和映射工作等,生成该应用程序需要在可重构处理器硬件上进行加速计算的二进制配置信息(context bitstream),最后通用处理器risc-v编译生成的二进制可执行文件交叉编译链接,生成完整的可重构处理器硬件系统最终的可执行文件,其中既包括了主控处理器的需要执行的传统串行或者控制类的软件代码的二进制指令信息,也包括了需要在可重构处理器单元上硬件加速代码的二进制配置信息。

[0003]

目前采用可重构处理器编译常用的高级软件编程语言(比如c/c++)的为编程模型,其中通过标签的形式,由程序员来进行软硬件任务的划分工作,对于需要由可重构处理器硬件加速的代码增加#pragram的作用类似,然后再通过编译流程生成相应加速代码的可重构配置信息。其中,映射和内存访存是编译器的重要因素,现有的编译方案对两者的使用模糊,已造成不能正确使用的情况。

技术实现要素:

[0004]

本发明的目的是提供一种可重构芯片的内存耦合编译方法,其通过对dfg数据流图中各节点的调整,使其满足可获取线性数组的要求,大幅缩减了编译时间,用户的编译体验感很强。实用性很高,不仅可用了可重构加速芯片,而且对于可编程器件上都有极高的复用性。

[0005]

同时本发明的另一个目的是提供一种可重构芯片的内存耦合编译系统,其大幅缩减了编译时间,用户的编译体验感很强。实用性很高,不仅可用了可重构加速芯片,而且对于可编程器件上都有极高的复用性。

[0006]

本发明的一个方面提供了一种可重构芯片的内存耦合编译方法,其包括:步骤s101,获取dfg数据流图的周期数。

[0007]

步骤s102,通过映射时间差获取周期数的线性转换矢量。

[0008]

步骤s103,判断是否能通过启发式算法获取线性转换矢量的线性数组,若能,则通过当前dfg数据流图获取内存映射结果,若否,则调整当前dfg数据流图后返回步骤s101,直到获取到线性数组为止。

[0009]

在本发明一种可重构芯片的内存耦合编译方法的一种实施方式中,步骤s103中则调整当前dfg数据流图后返回步骤s101的步骤还包括:根据最长路径周期数不变的原则调

整dfg数据流图中的节点获取当前dfg数据流图。

[0010]

在本发明一种可重构芯片的内存耦合编译方法的另一种实施方式中,根据最长路径周期数不变的原则调整dfg数据流图中的节点获取当前dfg数据流图的步骤还包括:判断dfg数据流图中是否存在可使最长路径周期数不变的节点,若是,则根据最长路径周期数不变的原则调整dfg数据流图中的节点获取当前dfg数据流图。若否,则根据最长路径周期数增加设定周期数个的原则调整dfg数据流图中的节点获取当前dfg数据流图。

[0011]

在本发明一种可重构芯片的内存耦合编译方法的再一种实施方式中,步骤s101中还包括:待运算数组通过可重构编译器经过clang编译器前端和llvm编译框架根据ddg有向多重图获取dfg数据流图。根据dfg数据流图中load节点和store节点的周期数获取dfg数据流图的周期数。

[0012]

在本发明一种可重构芯片的内存耦合编译方法的再一种实施方式中,启发式算法为公式1:公式1其中,gcd 代表取最大公约数;n为:可重构芯片中共享存储器的存储块数量。

[0013]

为:线性矢量; t为:转置; l代表数组的维度;代表寻求是否有交集,判断是否满足条件。本发明的另一个方面,提供了一种可重构芯片的内存耦合编译系统,其包括:获取单元,其配置为获取dfg数据流图的周期数。

[0014]

线性转换矢量单元,其配置为通过映射时间差获取周期数的线性转换矢量。和验证单元,其配置为判断是否能通过启发式算法获取线性转换矢量的线性数组,若能,则通过当前dfg数据流图获取内存映射结果,若否,则调整当前dfg数据流图后返回获取单元,直到获取到线性数组为止。

[0015]

在本发明一种可重构芯片的内存耦合编译系统的一种实施方式中,验证单元中则调整当前dfg数据流图后返回获取单元还包括:根据最长路径周期数不变的原则调整dfg数据流图中的节点获取当前dfg数据流图。

[0016]

在本发明一种可重构芯片的内存耦合编译系统的另一种实施方式中,根据最长路径周期数不变的原则调整dfg数据流图中的节点获取当前dfg数据流图的步骤还包括:判断dfg数据流图中是否存在可使最长路径周期数不变的节点,若是,则根据最长路径周期数不变的原则调整dfg数据流图中的节点获取当前dfg数据流图。若否,则根据最长路径周期数增加设定周期数个的原则调整dfg数据流图中的节点获取当前dfg数据流图。

[0017]

在本发明一种可重构芯片的内存耦合编译系统的再一种实施方式中,获取单元还配置为:待运算数组通过可重构编译器经过clang编译器前端和llvm编译框架根据ddg有向多重图获取dfg数据流图。根据dfg数据流图中load节点和store节点的周期数获取dfg数据流图的周期数。

[0018]

在本发明一种可重构芯片的内存耦合编译系统的再一种实施方式中,启发式算法为公式2:

ꢀ

公式2其中,gcd 代表取最大公约数;n为:可重构芯片中共享存储器的存储块数量;为:线性矢量; t为:转置; l代表数组的维度;代表寻求是否有交集,判断是否满足条件。下文将以明确易懂的方式,结合附图对一种可重构芯片的内存耦合编译方法及系统的特性、技术特征、优点及其实现方式予以进一步说明。

[0019]

附图说明

[0020]

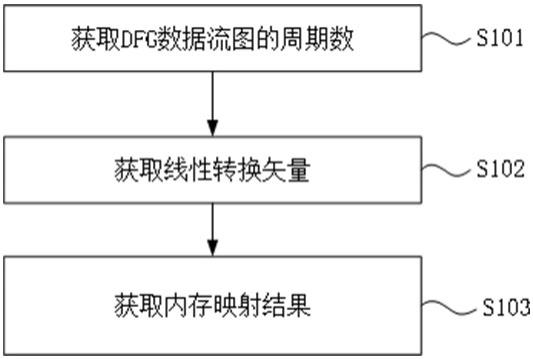

图1是用于说明在本发明一种实施方式中的可重构芯片的内存耦合编译方法的流程示意图。

[0021]

图2是用于说明在本发明一种实施方式中的可重构芯片的内存耦合编译的系统组成图。

[0022]

图3是用于说明在本发明另一种实施方式中的实例代码1的dfg数据流图。

[0023]

图4是用于说明在本发明另一种实施方式中的编译流程图。

具体实施方式

[0024]

为了对发明的技术特征、目的和效果有更加清楚的理解,现对照附图说明本发明的具体实施方式,在各图中相同的标号表示结构相同或结构相似但功能相同的部件。

[0025]

在本文中,“示意性”表示“充当实例、例子或说明”,不应将在本文中被描述为“示意性”的任何图示、实施方式解释为一种更优选的或更具优点的技术方案。为使图面简洁,各图中只示意性地表示出了与本示例性实施例相关的部分,它们并不代表其作为产品的实际结构及真实比例。

[0026]

本发明的一个方面提供了一种可重构芯片的内存耦合编译方法,如图1所示,可重构芯片的内存耦合编译方法其包括:步骤s101,获取dfg数据流图的周期数。

[0027]

本步骤中,获取待运算数组的dfg数据流图。根据该dfg数据流图获取其周期数。

[0028]

步骤s102,获取线性转换矢量。

[0029]

本步骤中,通过映射时间差获取周期数的线性转换矢量。

[0030]

步骤s103,获取内存映射结果。

[0031]

本步骤中,判断是否能通过启发式算法获取线性转换矢量的线性数组,若能,则通过当前dfg数据流图获取内存映射结果,若否,则调整当前dfg数据流图后返回步骤s101,直到获取到线性数组为止。

[0032]

在本发明一种可重构芯片的内存耦合编译方法的一种实施方式中,步骤s103中则调整当前dfg数据流图后返回步骤s101的步骤还包括:根据最长路径周期数不变的原则调整dfg数据流图中的节点获取当前dfg数据流图。

[0033]

在本发明一种可重构芯片的内存耦合编译方法的另一种实施方式中,根据最长路径周期数不变的原则调整dfg数据流图中的节点获取当前dfg数据流图的步骤还包括:

判断dfg数据流图中是否存在可使最长路径周期数不变的节点,若是,则根据最长路径周期数不变的原则调整dfg数据流图中的节点获取当前dfg数据流图。若否,则根据最长路径周期数增加设定周期数个的原则调整dfg数据流图中的节点获取当前dfg数据流图。

[0034]

在本发明一种可重构芯片的内存耦合编译方法的再一种实施方式中,步骤s101中还包括:待运算数组通过可重构编译器经过clang编译器前端和llvm编译框架ddg有向多重图获取dfg数据流图。根据dfg数据流图中ddgload加载节点和store存储节点的周期数获取dfg数据流图的周期数。

[0035]

在本发明一种可重构芯片的内存耦合编译方法的再一种实施方式中,启发式算法为公式1:公式1其中,gcd 代表取最大公约数;n为:可重构芯片中共享存储器的存储块数量;为:线性矢量; t为:转置; l代表数组的维度;代表寻求是否有交集,判断是否满足条件。本发明的另一个方面,如图2所示,提供了一种可重构芯片的内存耦合编译系统,其包括:获取单元101,其配置为获取dfg数据流图的周期数。

[0036]

线性转换矢量单元201,其配置为通过映射时间差获取周期数的线性转换矢量。和验证单元301,其配置为判断是否能通过启发式算法获取线性转换矢量的线性数组,若能,则通过当前dfg数据流图获取内存映射结果,若否,则调整当前dfg数据流图后返回获取单元101,直到获取到线性数组为止。

[0037]

在本发明一种可重构芯片的内存耦合编译系统的一种实施方式中,验证单元301中则调整当前dfg数据流图后返回获取单元101还包括:根据最长路径周期数不变的原则调整dfg数据流图中的节点获取当前dfg数据流图。

[0038]

在本发明一种可重构芯片的内存耦合编译系统的另一种实施方式中,根据最长路径周期数不变的原则调整dfg数据流图中的节点获取当前dfg数据流图的步骤还包括:判断dfg数据流图中是否存在可使最长路径周期数不变的节点,若是,则根据最长路径周期数不变的原则调整dfg数据流图中的节点获取当前dfg数据流图。若否,则根据最长路径周期数增加设定周期数个的原则调整dfg数据流图中的节点获取当前dfg数据流图。

[0039]

在本发明一种可重构芯片的内存耦合编译系统的再一种实施方式中,获取单元101还配置为:待运算数组通过可重构编译器经过clang编译器前端和llvm编译框架ddg有向多重图获取dfg数据流图。根据dfg数据流图中load加载节点和store存储节点的周期数获取dfg数据流图的周期数。

[0040]

在本发明一种可重构芯片的内存耦合编译系统的再一种实施方式中,启发式算法为公式2:

公式2其中,gcd 代表取最大公约数;n为:可重构芯片中共享存储器的存储块数量;为:线性矢量; t为:转置; l代表数组的维度;代表寻求是否有交集,判断是否满足条件。

[0041]

作为本发明一种可重构芯片的内存耦合编译方法的一种实施方式,本发明中的一种可重构芯片的内存耦合编译方法内容包括:cgra通常由主控制器(cpu),pe阵列,主存储器和本地存储器组成。cgra计算系统的执行流程如下:首先,cpu初始化cgra指令和输入数据进入主存储器。在cgra加速内核之前,应将输入数据从主内存传输到本地内存,并将指令加载到cgra的配置内存中。

[0042]

当cgra完成计算时,输出数据将从本地内存传输到主存储器。影响整体性能的过程包括数据传输任务和cgra计算任务。现有的优化方法仅优化cgra计算部分,而的方法则试图找到一种解决方案,以改善整个cgra计算流程。

[0043]

可重构处理器中负责任务处理的可重构处理单元阵列pea,主要由可重构配置信息来控制的,通过配置控制器来负责具体的配置信息的加载和分发。整个可重构pea阵列共享一个控制器,控制器负责为所有的pe单元生成一个共同的配置地址和配置序列,且整个pea的配置功能切换周期长,影响可重构处理器的动态重构和实用性。虽然每个pe对应的功能可以不同,但是每个pe单元却不能控制自己的执行过程。在可重构单元中严格的按照执行周期节拍来控制个每个pe单元,load单元的执行周期为5个周期,store单元的执行周期为5个周期,alu的执行周期为2个周期。

[0044]

如下实例代码1展示了多次访问同一个数组程序的例子。

[0045]

#include <stdlib.h>int main() {

ꢀꢀ

const s32_t frame_size = 200;

ꢀꢀ

s32_t frame[200];

ꢀꢀ

s32_t frame_verify[200];

ꢀꢀ

s32_t coef = 15;

ꢀꢀ

s32_t q_coef = 3;#pragma cgra map (to:coef, q_coef, frame_size) map(tofrom: frame[0:200])

ꢀꢀ

for (int i = frame_size

ꢀ-ꢀ

1; i > 1; i

--

) {

ꢀꢀꢀꢀ

s32_t tmp = ((s32_t)frame[i

ꢀ-ꢀ

1] * coef) >> q_coef;

ꢀꢀꢀꢀ

tmp = med3(min_q15, tmp, max_q15);

ꢀꢀꢀꢀ

tmp = (s32_t)frame[i]

ꢀ-ꢀ

tmp;

ꢀꢀꢀꢀ

frame[i] = med3(min_q15, tmp, max_q15);

ꢀꢀ

}}图3是可重构编译器经过clang 前端和llvm根据ddg分析出来的dfg数据流图,包括了所有运算的流程图,dfg节点将

‘0’

与frame[i-1],

‘1’

与frame[i] 和

‘

13

’

与frame[i]分别

对应,

‘0’

节点的启动的周期数是0,

‘1’

的启动周期是10,

‘

13

’

的启动周期是23。为了将循环流水化,每个时钟周期中三个元素(

‘0’

、

‘1’

,

‘

13

’

)将被同时访问。

[0046]

在此方案中,冲突将在每个周期发生,因为对于每次迭代,

‘1’

和

’

13

‘

分别对应的load和store操作,不能简单的将其合并,相同的库中(load frame[i]和store frame[i])将发生冲突,严重拖累程序运行性能。

[0047]

可重构处理器编译器映射内存之间是互相影响的,调整内存数组的拓扑结构会造成dfg节点的时间差不匹配,进而影响到映射是否需要补route节点和插入全局寄存器,相反映射后产生的新的时间节拍会影响到内存的拓扑结构。如果拓扑结构不合理不能满足硬件的banking结构,那么需要重复进行调整映射过程,而映射是需要消费大量的编译器的cpu时间,造成编译时间过长的,影响用户的开发效率。

[0048]

本发明中调整了映射和内存访存冲突的实现方式,将优先执行映射代码,然后利用映射代码计算各个load节点和store节点的周期数,然后将产生的周期数加到内存的拓扑结构中,然后尝试是否可以找个合理的内存分配机制,如果可以找到,既使用得到banking系数。

[0049]

如果不能找到合适的参数避免内存冲突,根据内存冲突反馈的情况下调整dfg流图,在dfg流图中插入route节点路由动态调整,最后将动态调整带有route节点的dfg流图进行重新映射,这种方式最多仅仅需要两次映射,一次banking策略就可以满足设计需求,流程图4所示:建立内存banking 数学模型,内存banking算法原理是核心是启发式算法,建立的数学模型如下:模型如下:模型如下:模型如下: 其中,为:线性矢量; t为:转置; l代表数组的维度;代表寻求是否有交集,判断是否满足条件。

[0050]

根据数学模型[1],针对上述实例代码1用例分别对frame[i-1], frame[i], frame[i]数组根据映射时间差建立了新的拓扑结构:r0=(1,0);r1=(1,-11);r2=(1,-24),根据启发式算法生成针对可重构处理器硬件资源的备选的集合,然后对产生的拓扑结构两

两使用[3]方法求解,最后得到了需要16bank就可以避免了内存访存的问题,而且也不需要调整dfg数据流图中load节点和store节点的位置。

[0051]

如果特殊的案例需要调整,就需要判断最长路径上的load节点和store节点是否满足设计内存要求,如果满足要求,就可以对分支load和store采用多目标遗传算法进行调整,对于不满足的要求,就需要在最长路径节点上插入不同的时间点,然后在重复上一次动作求解,直到找到一个可以满足设计要求的时间差,依据此时间差调整dfg,最后得到映射结果。

[0052]

从而本发明的有益效果在于:大幅缩减了编译时间,用户的编译体验感很强。使用不同的策略模式,不会在出现了因为映射和内存耦合关联下无法编译的问题。实用性很高,不仅仅可用了可重构加速芯片,而且对于可编程器件上都有极高的复用性。

[0053]

应当理解,虽然本说明书是按照各个实施方式中描述的,但并非每个实施方式仅包含一个独立的技术方案,说明书的这种叙述方式仅仅是为清楚起见,本领域技术人员应当将说明书作为一个整体,各实施例中的技术方案也可以经适当组合,形成本领域技术人员可以理解的其他实施方式。

[0054]

上文所列出的一系列的详细说明仅仅是针对本发明的可行性实施方式的具体说明,它们并非用以限制本发明的保护范围,凡未脱离本发明技艺精神所作的等效实施方式或变更均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1