一种量子线路中量子态振幅的模拟方法及装置与流程

1.本发明属于量子计算技术领域,特别是一种量子线路中量子态振幅的模拟方法及装置。

背景技术:

2.量子计算机是一类遵循量子力学规律进行高速数学和逻辑运算、存储及处理量子信息的物理装置。当某个装置处理和计算的是量子信息,运行的是量子算法时,它就是量子计算机。量子计算机因其具有相对普通计算机更高效的处理数学问题的能力,例如,能将破解rsa密钥的时间从数百年加速到数小时,故成为一种正在研究中的关键技术。

3.量子计算模拟是一个借助数值计算和计算机科学来仿真遵循量子力学规律的模拟计算,作为一个仿真程序,它依据量子力学的量子比特的基本定律,利用计算机的高速计算能力,刻画量子态的时空演化。

4.目前,可以先通过量子计算的相关理论,用经典计算机实现量子计算模拟,主要包括全振幅模拟与单振幅模拟,其中,全振幅模拟一次能够模拟出量子比特的量子态的所有振幅,单振幅模拟一次只模拟出所有量子态的振幅中的一个。但是,随量子程序中量子线路包含的量子比特数越多,两种模拟的内存开销随之增长,全振幅模拟的内存开销更呈指数增长,造成模拟效率降低。例如,对涉及30个量子比特的量子计算进行模拟,内存开销需16gbyte(吉字节);40个量子比特时,内存开销需16tbyte(太字节),即2

10

*(16gbyte);50个量子比特时,内存开销则需16pbyte(拍字节),即2

10

*(16tbyte)。并且,随着模拟的量子比特数越多,量子线路的复杂度增大,模拟效率也会随之下降。

技术实现要素:

5.本发明的目的是提供一种量子线路中量子态振幅的模拟方法及装置,以解决现有技术中的不足,它能够提高量子计算的模拟效率。本发明采用的技术方案如下:

6.为达到上述目的,本发明提供了一种量子线路中量子态振幅的模拟方法,所述方法包括:

7.根据目标量子线路包含的量子比特,拆分所述目标量子线路中的量子逻辑门,得到所述目标量子线路的子量子线路;

8.基于部分振幅的张量模拟算法,模拟各条所述子量子线路中待模拟的子量子态振幅;

9.利用各条所述子量子线路所模拟的子量子态振幅,计算所述目标量子线路中待模拟的量子态振幅。

10.可选的,所述根据目标量子线路包含的量子比特,拆分所述目标量子线路中的量子逻辑门,得到所述目标量子线路的子量子线路,包括:

11.将目标量子线路包含的总量子比特划分为第一量子比特和第二量子比特;

12.查找所述量子线路中操作所述第一量子比特和所述第二量子比特的量子逻辑门,

将查找出的量子逻辑门拆分为操作所述第一量子比特或所述第二量子比特的特定量子逻辑门的组合;

13.根据所述第一量子比特和所述第二量子比特,拆分当前量子线路,得到所述目标量子线路的子量子线路。

14.可选的,所述查找出的量子逻辑门包括:特定种类的双量子逻辑门;

15.所述将查找出的量子逻辑门拆分为操作所述第一量子比特或所述第二量子比特的特定量子逻辑门的组合,包括:

16.针对每一特定种类的双量子逻辑门,将该双量子逻辑门拆分成第一特定单门、第二特定单门和基础单量子逻辑门;

17.复制当前量子线路,将所述第一特定单门添加到当前量子线路中,将所述第二特定单门和基础单量子逻辑门添加到复制的量子线路中;其中,所述第一特定单门和所述第二特定单门操作的量子比特均为该双量子逻辑门的控制比特,所述基础单量子逻辑门操作的量子比特为该双量子逻辑门的受控比特,所述基础单量子逻辑门的种类由该双量子逻辑门的种类决定。

18.可选的,所述根据所述第一量子比特和所述第二量子比特,拆分当前量子线路,得到所述目标量子线路的子量子线路,包括:

19.拆分当前量子线路,将当前量子线路中包含所述第一量子比特的量子线路确定为第一子量子线路,将当前量子线路中包含所述第二量子比特的量子线路确定为第二子量子线路。

20.可选的,所述特定种类包括以下一种或多种:cnot门、cz门和cr门。

21.可选的,所述基于部分振幅的张量模拟算法,模拟各条所述子量子线路中待模拟的子量子态振幅,包括:

22.针对每一条子量子线路中的各个量子比特,更新该量子比特经所述子量子线路中的量子逻辑门操作后对应的张量单元以及记录相邻张量单元间纠缠信息的纠缠矩阵,其中,所述张量单元包括:|0》态和|1》态分别对应的振幅矩阵;

23.根据待模拟的子量子态,确定该子量子态中每一位分别对应的张量单元中的振幅矩阵;

24.根据所确定的振幅矩阵和所述纠缠矩阵,计算所述待模拟的子量子态的振幅。

25.可选的,所述利用各条所述子量子线路所模拟的子量子态振幅,计算所述目标量子线路中待模拟的量子态振幅,包括:

26.在各子量子线路中均包含量子逻辑门的情况下,利用各条子量子线路所模拟的子量子态振幅,计算所述目标量子线路中待模拟的量子态振幅;

27.否则,利用包含量子逻辑门的子量子线路所模拟的子量子态振幅,计算所述目标量子线路中待模拟的量子态振幅。

28.本技术的又一实施例提供了一种量子线路中量子态振幅的模拟装置,所述装置包括:

29.拆分模块,用于根据目标量子线路包含的量子比特,拆分所述目标量子线路中的量子逻辑门,得到所述目标量子线路的子量子线路;

30.模拟模块,用于基于部分振幅的张量模拟算法,模拟各条所述子量子线路中待模

拟的子量子态振幅;

31.计算模块,用于利用各条所述子量子线路所模拟的子量子态振幅,计算所述目标量子线路中待模拟的量子态振幅。

32.本技术的又一实施例提供了一种存储介质,所述存储介质中存储有计算机程序,其中,所述计算机程序被设置为运行时执行上述任一项中所述的方法。

33.本技术的又一实施例提供了一种电子装置,包括存储器和处理器,所述存储器中存储有计算机程序,所述处理器被设置为运行所述计算机程序以执行上述任一项中所述的方法。

34.与现有技术相比,本发明提供的一种量子线路中量子态振幅的模拟方法,首先根据目标量子线路包含的量子比特,拆分目标量子线路中的量子逻辑门,得到目标量子线路的子量子线路;基于部分振幅的张量模拟算法,模拟各条子量子线路中待模拟的子量子态振幅;利用各条子量子线路所模拟的子量子态振幅,计算目标量子线路中待模拟的量子态振幅。由于量子线路被拆分成多条子量子线路,所模拟的子量子线路中的量子比特数较少,能够减少内存资源的占用;通过部分振幅的张量模拟能够降低子量子线路的计算维度,且只需模拟所需模拟的部分数量个量子态振幅,无需模拟所有的量子态振幅,进一步提高量子计算的模拟效率。

附图说明

35.图1为本发明实施例提供的一种量子线路中量子态振幅的模拟方法的计算机终端的硬件结构框图;

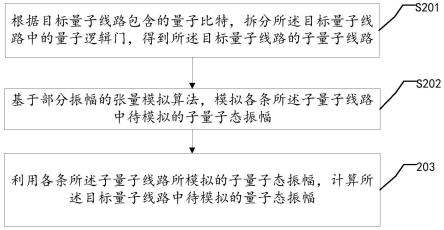

36.图2为本发明实施例提供的一种量子线路中量子态振幅的模拟方法的流程示意图;

37.图3为本发明实施例提供的一种量子线路的拆分示意图;

38.图4为本发明实施例提供的一种子量子线路的张量网络形式示意图;

39.图5为本发明实施例提供的一种量子线路中量子态振幅的模拟装置的结构示意图。

具体实施方式

40.下面通过参考附图描述的实施例是示例性的,仅用于解释本发明,而不能解释为对本发明的限制。

41.本发明实施例首先提供了一种量子线路中量子态振幅的模拟方法,该方法可以应用于电子设备,如计算机终端,具体如普通电脑、量子计算机等。

42.下面以运行在计算机终端上为例对其进行详细说明。图1为本发明实施例提供的一种量子线路中量子态振幅的模拟方法的计算机终端的硬件结构框图。如图1所示,计算机终端可以包括一个或多个(图1中仅示出一个)处理器102(处理器102可以包括但不限于微处理器mcu或可编程逻辑器件fpga等的处理装置)和用于存储数据的存储器104,可选地,上述计算机终端还可以包括用于通信功能的传输装置106以及输入输出设备108。本领域普通技术人员可以理解,图1所示的结构仅为示意,其并不对上述计算机终端的结构造成限定。例如,计算机终端还可包括比图1中所示更多或者更少的组件,或者具有与图1所示不同的

配置。

43.存储器104可用于存储应用软件的软件程序以及模块,如本技术实施例中的量子线路中量子态振幅的模拟方法对应的程序指令/模块,处理器102通过运行存储在存储器104内的软件程序以及模块,从而执行各种功能应用以及数据处理,即实现上述的方法。存储器104可包括高速随机存储器,还可包括非易失性存储器,如一个或者多个磁性存储装置、闪存、或者其他非易失性固态存储器。在一些实例中,存储器104可进一步包括相对于处理器102远程设置的存储器,这些远程存储器可以通过网络连接至计算机终端。上述网络的实例包括但不限于互联网、企业内部网、局域网、移动通信网及其组合。

44.传输装置106用于经由一个网络接收或者发送数据。上述的网络具体实例可包括计算机终端的通信供应商提供的无线网络。在一个实例中,传输装置106包括一个网络适配器(network interface controller,nic),其可通过基站与其他网络设备相连从而可与互联网进行通讯。在一个实例中,传输装置106可以为射频(radio frequency,rf)模块,其用于通过无线方式与互联网进行通讯。

45.需要说明的是,真正的量子计算机是混合结构的,它包含两大部分:一部分是经典计算机,负责执行经典计算与控制;另一部分是量子设备,负责运行量子程序进而实现量子计算。而量子程序是由量子语言如qrunes语言编写的一串能够在量子计算机上运行的指令序列,实现了对量子逻辑门操作的支持,并最终实现量子计算。具体的说,量子程序就是一系列按照一定时序操作量子逻辑门的指令序列。

46.在实际应用中,因受限于量子设备硬件的发展,通常需要进行量子计算模拟以验证量子算法、量子应用等等。量子计算模拟即借助普通计算机的资源搭建的虚拟架构(即量子虚拟机)实现特定问题对应的量子程序的模拟运行的过程。通常,需要构建特定问题对应的量子程序。本发明实施例所指量子程序,即是经典语言编写的表征量子比特及其演化的程序,其中与量子计算相关的量子比特、量子逻辑门等等均有相应的经典代码表示。

47.量子线路作为量子程序的一种体现方式,也称量子逻辑电路,是最常用的通用量子计算模型,表示在抽象概念下对于量子比特进行操作的线路,其组成包括量子比特、线路(时间线),以及各种量子逻辑门,最后常需要通过量子测量操作将结果读取出来。

48.不同于传统电路是用金属线所连接以传递电压信号或电流信号,在量子线路中,线路可看成是由时间所连接,亦即量子比特的状态随着时间自然演化,在这过程中按照哈密顿运算符的指示,一直到遇上逻辑门而被操作。

49.一个量子程序整体上对应有一条总的量子线路,本发明所述量子程序即指该条总的量子线路,其中,该总的量子线路中的量子比特总数与量子程序的量子比特总数相同。可以理解为:一个量子程序可以由量子线路、针对量子线路中量子比特的测量操作、保存测量结果的寄存器及控制流节点(跳转指令)组成,一条量子线路可以包含几十上百个甚至千上万个量子逻辑门操作。量子程序的执行过程,就是对所有的量子逻辑门按照一定时序执行的过程。需要说明的是,时序即单个量子逻辑门被执行的时间顺序。

50.需要说明的是,经典计算中,最基本的单元是比特,而最基本的控制模式是逻辑门,可以通过逻辑门的组合来达到控制电路的目的。类似地,处理量子比特的方式就是量子逻辑门。使用量子逻辑门,能够使量子态发生演化,量子逻辑门是构成量子线路的基础,量子逻辑门包括单比特量子逻辑门,如hadamard门(h门,阿达马门)、泡利-x门(x门)、泡利-y

门(y门)、泡利-z门(z门)、rx门、ry门、rz门等等;两比特或多比特量子逻辑门,如cnot门、cr门、cz门、iswap门、toffoli门等等。量子逻辑门一般使用酉矩阵表示,而酉矩阵不仅是矩阵形式,也是一种操作和变换。一般量子逻辑门在量子态上的作用是通过酉矩阵左乘以量子态右矢对应的矩阵进行计算的。

51.例如,量子态右矢|0》对应的矩阵为量子态右矢|1》对应的矩阵为

52.参见图2,图2为本发明实施例提供的一种量子线路中量子态振幅的模拟方法的流程示意图,可以包括如下步骤:

53.s201,根据目标量子线路包含的量子比特,拆分所述目标量子线路中的量子逻辑门,得到所述目标量子线路的子量子线路;

54.其中,目标量子线路包含的量子比特是指目标量子线路中的所有量子比特,拆分量子逻辑门是指将量子逻辑门等效转化为其他量子逻辑门的组合。可以通过遍历目标量子线路,提取并记录所有的量子逻辑门,然后进行拆分操作。

55.具体的,s201可以包括如下步骤:

56.s2011,将目标量子线路包含的总量子比特划分为第一量子比特和第二量子比特;

57.优选的,当总量子比特数为偶数时,可以一半划分为第一量子比特,另一半划分为第二量子比特;当总量子比特数为奇数时,尽量接近一半一半划分。

58.例如,总量子比特数为8位:q7q6q5q4q3q2q1q0,则前0-3位划分为第一量子比特,4-7位划分为第二量子比特;

59.再如,总量子比特数为7位:q6q5q4q3q2q1q0,则前0-3位(或前0-2位)划分为第一量子比特,4-6位(或3-6位)划分为第二量子比特。

60.s2012,查找所述量子线路中操作所述第一量子比特和所述第二量子比特的量子逻辑门,将查找出的量子逻辑门拆分为操作所述第一量子比特或所述第二量子比特的特定量子逻辑门的组合;

61.在划分完量子比特后,查找同时操作在第一量子比特和第二量子比特的量子逻辑门。其中,目标量子线路中查找出的量子逻辑门优选包括:特定种类的双量子逻辑门,优选cnot门、cz门和cr门等可以直接拆分的双量子逻辑门。其中,cnot门的矩阵形式(酉矩阵)为:cz门的矩阵形式为:cr门或称cr(θ)门的矩阵形式为:

62.具体的,可以针对每一特定种类的双量子逻辑门,将该双量子逻辑门拆分成第一特定单门、第二特定单门和基础单量子逻辑门;复制当前量子线路,将第一特定单门添加到当前量子线路中,将第二特定单门和基础单量子逻辑门添加到复制的量子线路中。

63.其中,第一特定单门和第二特定单门操作的量子比特均为该双量子逻辑门的控制

比特,基础单量子逻辑门操作的量子比特为该双量子逻辑门的受控比特,基础单量子逻辑门的种类由该双量子逻辑门的种类决定。

64.以cnot门、cz门和cr门为例,在一种拆分方式中,拆分后的第一特定单门设为p0门,其矩阵形式为:第二特定单门为p1门,其矩阵形式为:特定种类的双门(双量子逻辑门)与基础单量子逻辑门的对应决定关系如下:

65.cnot门,对应not门(非门,又称x门),矩阵形式:

66.cz门,对应z门,矩阵形式:

67.cr门,对应u1或称u1(θ)门,矩阵形式:

68.从矩阵形式可看出,能够被拆分的双门左上角的2*2部分可看成单位矩阵,右下角的2*2部分可看成拆分后对应的基础单量子逻辑门。其内在的数学原理,以cz门为例,可如下表示:

[0069][0070]

其中,p0=(1 0),p1=(0 1),单位矩阵i=(1 1),(1-1)表示z门,可得同理:同理:其中,表示直积。

[0071]

在实际应用中,查找出的量子逻辑门还可以包括不可直接拆分的多量子逻辑门以及其他个别双量子逻辑门如iswap、sqiswap、iswap(θ)、cu和swap等等,可以将其转化为多个可直接拆分的特定种类双量子逻辑门的组合,或者,单门和多个可直接拆分的特定种类双量子逻辑门的组合,然后进行拆分,这也是合理可行的。

[0072]

s2013,根据所述第一量子比特和所述第二量子比特,拆分当前量子线路,得到所述目标量子线路的子量子线路。

[0073]

具体的,可以拆分当前量子线路,将当前量子线路中包含第一量子比特的量子线路确定为第一子量子线路,将当前量子线路中包含第二量子比特的量子线路确定为第二子量子线路。

[0074]

如前述,优选的,如果原目标量子线路包含偶数个量子比特,则拆分得到的子量子线路的第一量子比特数和第二量子比特数相同,均为一半;如果包含奇数个量子比特,则拆分得到的子量子线路的量子比特数相近,接近一半。

[0075]

这样拆分的好处在于可以最大程度减少内存资源的占用。例如,如果将10比特量子线路拆分为2比特子量子线路和8比特子量子线路,至少需要提供8量子比特所需的内存资源,而拆分为多条5比特子量子线路,则只需提供5量子比特所需的内存资源,从而减少资源占用和量子线路模拟计算的复杂度。并且,在计算机设备内存有限的情况下,优选的拆分方式可以模拟计算更多量子比特的目标量子线路。

[0076]

示例性的,如图3所示,一目标量子线路配置有4个量子比特(即总比特数4)q3、q2、q1、q0,图中以量子比特的下标(即比特位)0、1、2、3简化表示。h 0表示h门操作的目标比特为q0,cnot 0,2即cnot(0,2)表示cnot门操作的控制比特和受控比特分别为q0、q2,cz 3,1即cz(3,1)表示cz门操作的控制比特和受控比特分别为q3、q1,p0 0表示p0门操作的目标比特为q0,p11表示p1门操作的目标比特为q1,其余同理。

[0077]

将前一半量子比特q0、q1划分为第一量子比特、后一半q2、q3划分为第二量子比特。查找出该量子线路中同时操作第一量子比特和第二量子比特的双门为cnot(0,2)和cz(3,1),且该两个双门均属于特定种类的双门,可以直接拆分。

[0078]

遍历目标量子线路,该量子线路中量子逻辑门的执行时序为h 0、cnot(0,2)、cz(3,1)和h 3。首先遍历到的双门为cnot门,将cnot(0,2)拆分为p0门、p1门和not门,复制当前量子线路(此时cnot门已不存在),复制的量子线路作为副本量子线路,根据po门操作的目标比特q0,将p0门添加到当前量子线路中,根据p1门操作的目标比特q0、not门操作的目标比特q2,将p1门和not门添加到副本量子线路中。此时的量子线路有两条,每条的量子比特总数为4,其中一条包括量子逻辑门h 0、p0 0、cz(3,1)和h 3,另一条包括h 0、p1 0、not 2、cz(3,1)和h 3。

[0079]

然后,针对当前两条量子线路中的cz门,对其中一条,将cz(3,1)拆分为p0门、p1门和z门,复制该条量子线路,根据该po门操作的目标比特q3,将p0门添加到该条量子线路中,根据该p1门操作的目标比特q3、not门操作的目标比特q1,将p1门和not门添加到复制该条量子线路所得到的副本量子线路中。对另一条同理操作,最终得到4条中间的新量子线路,每条的量子比特总数仍为4,分别如下:

[0080]

一条包括h 0、p0 0、p0 3和h 3,q1和q2无量子逻辑门操作;

[0081]

另一条包括h 0、p0 0、p1 3、z 1和h 3,q2无量子逻辑门操作;

[0082]

再一条包括h 0、p1 0、not 2、p0 3和h 3;

[0083]

最后一条包括h 0、p1 0、not 2、p1 3、z1和h 3。

[0084]

此时,所有特定种类的双门都被拆分,且经上述添加得到4条只有单门的新量子线路。拆分各条新量子线路,以量子比特总数4的前一半和后一半为界限拆分该量子线路,分别作为子量子线路,最终得到8条子量子线路,每条包含的总(量子)比特数为2,并且,根据计算机的计算特性,每条的量子比特位均从0开始编号,即对每条子量子线路来说,自身的量子比特均为q0、q1,分别如下:

[0085]

第1条包括h 0、p0 0,q1上无量子逻辑门操作;

[0086]

第2条包括p0 1、h 1,q0上无量子逻辑门操作;

[0087]

第3条包括h 0、p0 0、z1;

[0088]

第4条包括p1 1、h 1,q0上无量子逻辑门操作;

[0089]

第5条包括h 0、p1 0,q1上无量子逻辑门操作;

[0090]

第6条包括not 0、p0 1、h 1;

[0091]

第7条包括h 0、p1 0、z 1;

[0092]

第8条包括not 0、p1 1、h 1。

[0093]

同理,每多查找出一个同时操作第一量子比特和第二量子比特的特定种类的双门,最终得到的子量子线路数量将会翻一倍。

[0094]

本领域技术人员可理解的是,一条量子线路中量子比特总数的多少,对计算复杂度和内存的占用影响是极大的。由于每条子量子线路的量子比特数均减半,模拟需要的内存呈指数级递减,计算难度大大减少。

[0095]

s202,基于部分振幅的张量模拟算法,模拟各条所述子量子线路中待模拟的子量子态振幅;

[0096]

在量子计算领域,每个量子比特都可以同时处于|0》和|1》的叠加态,一个量子比特的量子态ψ可以表示为a|0》+b|1》,其中,a、b分别为|0》、|1》的振幅,均为复数。测量后,量子态塌缩至一个固定的量子态,其中,塌缩至|0》的概率是|a|2,塌缩至|1》的概率是|b|2,|a|2+|b|2=1。而n个量子比特的量子态则为2n个量子态的叠加态。举例而言,3个量子比特组成的量子态ψ为23(即8)个量子态的叠加态,其中,这8个量子态又称本征态,分别为|000》、|001》、|010》、|011》、|100》、|101》、|110》和|111》,此时,3个量子比特组成的量子态ψ可以表示为:

[0097]

ψ=c0|000》+c1|001》+c2|010》+c3|011》+c4|100》+c5|101》+c6|110》+c7|111》

[0098]

其中,8个量子态中的每个量子态或称为一个量子态分量,每个量子态分量对应的振幅,即c0至c7这些复数中的每一个可称作一个单振幅,每一个单振幅的下标值为该单振幅所属量子态的二进制对应的十进制值。全振幅模拟,便是指一次性模拟出n个量子比特的2n个量子态分量的振幅;而单振幅模拟,则是指一次性模拟2n个量子态中的任意一个量子态分量的振幅。

[0099]

在有些情况下,用户只需模拟计算量子线路的一个或多个量子态振幅并非全部振幅,使用全振幅模拟会浪费计算资源。并且,使用单振幅或全振幅模拟会对整条量子线路进行矩阵运算的操作(一个量子逻辑门对应一个矩阵形式,一条量子线路实际上也对应一个大的矩阵形式,量子态在数学表示上也是矩阵,因此量子态的演化模拟在数学上就是一系列矩阵运算的过程),涉及整条量子线路对应的矩阵维度,计算效率并不高。

[0100]

基于此,可以结合部分振幅的张量模拟待模拟的部分量子态振幅。其中,量子态定义为系数矩阵满足tt(tensor-train)形式,该系数矩阵用正则形式t0λ0t1λ1…

t

n-2

λ

n-2

t

n-1

表示量子态系数,即量子态振幅,每一个ti是表示量子比特位i的复数张量,每一个λi(纠缠谱)用于规范化量子比特位i和i+1的振幅,是实数矩阵(纠缠矩阵)。

[0101]

具体的,可以针对每一条子量子线路中的各个量子比特,更新该量子比特经所述子量子线路中的量子逻辑门操作后对应的张量单元以及记录相邻张量单元间纠缠信息的纠缠矩阵,其中,张量单元包括:|0》态和|1》态分别对应的振幅矩阵;根据待模拟的子量子态,确定该子量子态中每一位分别对应的张量单元中的振幅矩阵;根据所确定的振幅矩阵和纠缠矩阵,计算待模拟的子量子态的振幅。

[0102]

其中,子量子线路中量子比特的初始态为a|0》+b|1》,其中,a=1+0i,b=0+0i,可得|0》态对应1维的振幅矩阵[(1,0)],仅一个元素(1,0),表示复数1+0i;|1》态对应1维的振幅矩阵[(0,0)],仅一个元素(0,0),表示复数0+0i。进而,量子比特的初始张量单元可表示为并且,纠缠矩阵λ的初始值设为1。

[0103]

通过将量子比特与张量单元对应,量子逻辑门对量子比特的操作可转化为量子逻辑门的酉矩阵与张量的运算,能够减少矩阵运算的维度,从而提高计算效率,并且,可以根

据用户需求模拟计算想要模拟的量子态。

[0104]

示例性的,如图4所示,图4为一种3量子比特q0、q1、q2的子量子线路的张量网络表示形式。图4中每一个单元表示一个量子比特对应的张量单元,共3个张量单元t0、t1、t2;单元间的连线表示记录相邻张量单元间纠缠信息的纠缠矩阵λ,q0、q1之间连线表示λ0,q1、q2之间连线表示λ1,用于规范相邻量子比特位的振幅。

[0105]

假设子量子线路执行如下量子逻辑门操作,则张量单元中振幅矩阵和纠缠矩阵更新如下:

[0106]

初始:

[0107][0108]

λ0=1,λ1=1;

[0109]

对0号位量子比特q0执行h门操作,简写为:h 0,得到:

[0110][0111]

λ0=1,λ1=1;

[0112]

继续执行cnot 0,1得到:

[0113][0114][0115]

最后执行cnot 0,2得到:

[0116][0117][0118]

[0119]

其中,h门操作对应的量子比特的张量运算如下:

[0120]

由初始态得到0号比特的初始张量为将h门的酉矩阵作用于该张量:作用于该张量:故而,|0》态和|1》态的振幅矩阵均为1维矩阵写成复数元素形式为由于h门只操作0号比特,故λ保持不变。其余单量子逻辑门的张量运算同理。

[0121]

对于操作相邻量子比特位的cnot 0,1,涉及张量运算如下:

[0122]

将0号、1号比特的张量进行缩并:缩并过程为:

[0123]

|00》态:0号比特的|0》态振幅矩阵与1号比特的|0》态振幅矩阵[1]缩并:

[0124]

|01》态:0号比特的|0》态振幅矩阵与1号比特的|1》态振幅矩阵[0]缩并:

[0125]

|10》态:0号比特的|1》态振幅矩阵与1号比特的|0》态振幅矩阵[1]缩并:

[0126]

|11》态:0号比特的|1》态振幅矩阵与1号比特的|1》态振幅矩阵[0]缩并:

[0127]

将|00》态、|01》态、|10》态、|11》态振幅矩阵从上至下排布为(该4个振幅矩阵不论是1维或多维均写成这种形式),作用cnot门的酉矩阵得到:

[0128][0129]

将缩并后的张量对应|00》态、|01》态、|10》态、|11》态振幅矩阵[1]、[0]、[0]、[1],分别作为矩阵的左上、右上、左下、右下四部分,将其转化为待分解的张量:

[0130]

然后,可以利用tt(tensor-train)分解(具体可为svd奇异值分解),将其分解为:分别作为cnot门操作后的q0的张量单元、λ0、q1的张量单元。对于q0,其上半部分[1 0]作为|0》态的振幅矩阵,下半部分[0 1]作为|1》态的振幅矩阵;对于q1,其左半部分作为|0》态的振幅矩阵,右半部分作为|1》态的振幅矩阵,更新其余双量子逻辑门或受单比特控制的单量子逻辑门(形式上可看成双量子逻辑门)的张量运算同理。需要说明的是,对于任一矩阵a的svd分解获得usv

t

,使得a=usv

t

为现有技术,本发明在此对其不进行赘述。

[0131]

对于操作不相邻的量子比特位的双量子逻辑门cnot 0,2,则将其转化为两个操作相邻量子比特位的双量子逻辑门:可以先执行交换门swap 1,2,将1号与2号比特的量子位进行交换,量子位顺序变为0、2、1,然后执行cnot 0,1,实际上操作的就是0号和2号比特。对于swap 1,2和cnot 0,1,依次按照上述双量子逻辑门同理进行张量运算,最终得到上述更新后的结果。

[0132]

假设待模拟的子量子态为|000》,3位二进制值000从右至左对应q2、q1、q0,其振幅计算为:依次取0比特的|0》态的振幅矩阵、λ0、1比特的|0》态的振幅矩阵、λ1、2比特的|0》态的振幅矩阵相乘,得到:

[0133]

[0134]

如有模拟需求,同理可得其余子量子态的振幅:|001》:0;|010》:0;|011》:0;|100》:0;|101》:0;|110》:0;|111》:可见,该子量子线路执行后总的子量子态为|000》、|111》的叠加态,表示为:

[0135]

s203,利用各条所述子量子线路所模拟的子量子态振幅,计算所述目标量子线路中待模拟的量子态振幅。

[0136]

其中,子量子态是指子量子线路的量子态,由于子量子线路是原目标量子线路的一部分,子量子态从而也是目标量子线路中待模拟的量子态的组成部分。子量子态由用户预设的目标量子线路中待模拟的量子态所确定,通过模拟组成该目标量子线路待模拟的量子态的各子量子态振幅,然后计算得到该目标量子线路待模拟的量子态振幅。

[0137]

具体的,在各子量子线路中均包含量子逻辑门的情况下,利用各条子量子线路所模拟的子量子态振幅,计算目标量子线路中待模拟的量子态振幅;否则,利用包含量子逻辑门的子量子线路所模拟的子量子态振幅,计算目标量子线路中待模拟的量子态振幅。

[0138]

示例性的,某一量子线路l的量子比特总数为10,查找出共有2个同时操作第一量子比特和第二量子比特的量子逻辑门且均为特定种类的双量子逻辑门,最终构建出8条子量子线路a和b(由一条中间的新量子线路l1拆分)、c和d(由另一条中间新量子线路l2拆分)、e和f(由再一条中间的新量子线路l3拆分)、g和h(由最后一条中间新量子线路l4拆分)。每条子量子线路的量子比特数为5,高位至低位排序为q4q3q2q1q0,量子态为25=32个,量子态的下标值表示为0-31,二进制表示为00000-11111,量子态二进制右起第1位对应q0、第5位对应q4。

[0139]

假设b、d、f和h中的5量子比特分别代表原l1、l2、l3和l4的10个量子比特中前五位q

9-q5,a、c、e和g中的5量子比特分别代表原l1、l2、l3和l4的10个量子比特中后五位q

4-q0。每条子量子线路中的5量子比特的量子态均为00000-11111。

[0140]

如果每条子量子线路中均包含量子逻辑门,该条量子线路的10量子比特的量子态0000000000-1111111111的振幅计算公式如下:

[0141]

l(0000000000)=a(00000)*b(00000)+c(00000)*d(00000)+e(00000)*f(00000)+g(00000)*h(00000);

[0142]

l(0000000001)=a(00001)*b(00000)+c(00001)*d(00000)+e(00001)*f(00000)+g(00001)*h(00000);

[0143]

l(0000000010)=a(00010)*b(00000)+c(00010)*d(00000)+e(00010)*f(00000)+g(00010)*h(00000);

[0144]

……

[0145]

l(0000011111)=a(11111)*b(00000)+c(11111)*d(00000)+e(11111)*f(00000)+g(11111)*h(00000);

[0146]

l(0000100000)=a(00000)*b(00001)+c(00000)*d(00001)+e(00000)*f(00001)+g(00000)*h(00001);

[0147]

……

[0148]

l(1000000000)=a(00000)*b(10000)+c(00000)*d(10000)+e(00000)*f(10000)+

的量子态00-11的振幅,j4(00)-j4(11)为子量子线路j4中量子比特q1q0的量子态00-11的振幅。

[0167]

如果有子量子线路假设为j2和j3不包含量子逻辑门,则该条量子线路的3量子比特q2q1q0的量子态000-111的振幅的计算如下:

[0168]

j(000)=1*j1(0)+j4(00)*1=j1(0)+j4(00);

[0169]

j(001)=1*j1(1)+j4(00)*0=j1(1);

[0170]

j(010)=0*j1(0)+j4(01)*1=j4(01);

[0171]

j(011)=0*j1(1)+j4(01)*0=0;

[0172]

j(100)=0*j1(0)+j4(10)*1=j4(10);

[0173]

j(101)=0*j1(1)+j4(10)*0=0;

[0174]

j(110)=0*j1(0)+j4(11)*1=j4(11);

[0175]

j(111)=0*j1(1)+j4(11)*0=0。

[0176]

对于量子线路的全振幅模拟方法,能够在16g内存的计算机中模拟接近30个量子比特的量子线路。将目标量子线路进行拆分,将总比特数降低一半左右,通过模拟拆分后的子量子线路,实现原目标量子线路的模拟。从而在理论上,能够在16g内存的计算机中实现最多60位量子比特左右的目标量子线路的模拟。

[0177]

可见,由于量子线路被拆分成多条子量子线路,所模拟的子量子线路中的量子比特数较少,能够减少内存资源的占用;通过部分振幅的张量模拟能够降低子量子线路的计算维度,且只需模拟所需的一个或多个量子态振幅,无需模拟所有的量子态振幅,进一步提高量子计算的模拟效率。

[0178]

参见图5,图5为本发明实施例提供的一种量子线路中量子态振幅的模拟装置的结构示意图,与图1所示的流程相对应,所述装置包括:

[0179]

拆分模块501,用于根据目标量子线路包含的量子比特,拆分所述目标量子线路中的量子逻辑门,得到所述目标量子线路的子量子线路;

[0180]

模拟模块502,用于基于部分振幅的张量模拟算法,模拟各条所述子量子线路中待模拟的子量子态振幅;

[0181]

计算模块503,用于利用各条所述子量子线路所模拟的子量子态振幅,计算所述目标量子线路中待模拟的量子态振幅。

[0182]

具体的,所述拆分模块,包括:

[0183]

划分单元,用于将目标量子线路包含的总量子比特划分为第一量子比特和第二量子比特;

[0184]

第一拆分单元,用于查找所述量子线路中操作所述第一量子比特和所述第二量子比特的量子逻辑门,将查找出的量子逻辑门拆分为操作所述第一量子比特或所述第二量子比特的特定量子逻辑门的组合;

[0185]

第二拆分单元,用于根据所述第一量子比特和所述第二量子比特,拆分当前量子线路,得到所述目标量子线路的子量子线路。

[0186]

具体的,所述查找出的量子逻辑门包括:特定种类的双量子逻辑门;

[0187]

所述第一拆分单元,具体用于:

[0188]

针对每一特定种类的双量子逻辑门,将该双量子逻辑门拆分成第一特定单门、第

二特定单门和基础单量子逻辑门;

[0189]

复制当前量子线路,将所述第一特定单门添加到当前量子线路中,将所述第二特定单门和基础单量子逻辑门添加到复制的量子线路中;其中,所述第一特定单门和所述第二特定单门操作的量子比特均为该双量子逻辑门的控制比特,所述基础单量子逻辑门操作的量子比特为该双量子逻辑门的受控比特,所述基础单量子逻辑门的种类由该双量子逻辑门的种类决定。

[0190]

具体的,所述第二拆分单元,具体用于:

[0191]

拆分当前量子线路,将当前量子线路中包含所述第一量子比特的量子线路确定为第一子量子线路,将当前量子线路中包含所述第二量子比特的量子线路确定为第二子量子线路。

[0192]

具体的,所述特定种类包括以下一种或多种:cnot门、cz门和cr门。

[0193]

具体的,所述模拟模块,具体用于:

[0194]

针对每一条子量子线路中的各个量子比特,更新该量子比特经所述子量子线路中的量子逻辑门操作后对应的张量单元以及记录相邻张量单元间纠缠信息的纠缠矩阵,其中,所述张量单元包括:|0》态和|1》态分别对应的振幅矩阵;

[0195]

根据待模拟的子量子态,确定该子量子态中每一位分别对应的张量单元中的振幅矩阵;

[0196]

根据所确定的振幅矩阵和所述纠缠矩阵,计算所述待模拟的子量子态的振幅。

[0197]

具体的,所述计算模块,具体用于:

[0198]

在各子量子线路中均包含量子逻辑门的情况下,利用各条子量子线路所模拟的子量子态振幅,计算所述目标量子线路中待模拟的量子态振幅;

[0199]

否则,利用包含量子逻辑门的子量子线路所模拟的子量子态振幅,计算所述目标量子线路中待模拟的量子态振幅。

[0200]

可见,由于量子线路被拆分成多条子量子线路,所模拟的子量子线路中的量子比特数较少,能够减少内存资源的占用;通过部分振幅的张量模拟能够降低子量子线路的计算维度,且只需模拟所需的一个或多个量子态振幅,无需模拟所有的量子态振幅,进一步提高量子计算的模拟效率。

[0201]

本发明实施例还提供了一种存储介质,所述存储介质中存储有计算机程序,其中,所述计算机程序被设置为运行时执行上述任一项方法实施例中的步骤。

[0202]

具体的,在本实施例中,上述存储介质可以被设置为存储用于执行以下步骤的计算机程序:

[0203]

s1,根据目标量子线路包含的量子比特,拆分所述目标量子线路中的量子逻辑门,得到所述目标量子线路的子量子线路;

[0204]

s2,基于部分振幅的张量模拟算法,模拟各条所述子量子线路中待模拟的子量子态振幅;

[0205]

s3,利用各条所述子量子线路所模拟的子量子态振幅,计算所述目标量子线路中待模拟的量子态振幅。

[0206]

具体的,在本实施例中,上述存储介质可以包括但不限于:u盘、只读存储器(read-only memory,简称为rom)、随机存取存储器(random access memory,简称为ram)、移动硬

盘、磁碟或者光盘等各种可以存储计算机程序的介质。

[0207]

本发明实施例还提供了一种电子装置,包括存储器和处理器,其特征在于,所述存储器中存储有计算机程序,所述处理器被设置为运行所述计算机程序以执行上述任一项方法实施例中的步骤。

[0208]

具体的,上述电子装置还可以包括传输设备以及输入输出设备,其中,该传输设备和上述处理器连接,该输入输出设备和上述处理器连接。

[0209]

具体的,在本实施例中,上述处理器可以被设置为通过计算机程序执行以下步骤:

[0210]

s1,根据目标量子线路包含的量子比特,拆分所述目标量子线路中的量子逻辑门,得到所述目标量子线路的子量子线路;

[0211]

s2,基于部分振幅的张量模拟算法,模拟各条所述子量子线路中待模拟的子量子态振幅;

[0212]

s3,利用各条所述子量子线路所模拟的子量子态振幅,计算所述目标量子线路中待模拟的量子态振幅。

[0213]

具体的,本实施例中的具体示例可以参考上述实施例及可选实施方式中所描述的示例,本实施例在此不再赘述。

[0214]

以上依据图式所示的实施例详细说明了本发明的构造、特征及作用效果,以上所述仅为本发明的较佳实施例,但本发明不以图面所示限定实施范围,凡是依照本发明的构想所作的改变,或修改为等同变化的等效实施例,仍未超出说明书与图示所涵盖的精神时,均应在本发明的保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1