一种基于SW3231处理器实现的计算机控制板的制作方法

一种基于sw3231处理器实现的计算机控制板

技术领域

1.本实用新型涉及计算机技术领域,尤其是一种基于sw3231处理器实现的计算机控制板。

背景技术:

2.计算机技术是世界上发展最快的科学技术之一,产品不断升级换代,目前计算机硬件产品主要以intel为代表,通常安全设备的计算机控制板采用的基本都是国外品牌的处理器和南北桥芯片,采用开放式结构,主要考虑的是计算、可靠性及功耗等非安全性的因素,从而导致处理器存在很多安全漏洞,使得不法分子可以很容易地植入监听、监视装置窃取国家秘密信息,如计算机技术缺陷、病毒、信息垃圾、黑客和信息勒索等一系列安全威胁。随着我国信息化的进一步发展,信息安全问题日益引起重视,为保证信息安全,承载信息安全的计算机控制板显得尤为重要,因此对国产化的硬件平台的需求也越来越迫切。

技术实现要素:

3.本发明人针对上述问题及技术需求,提出了一种基于sw3231处理器实现的计算机控制板,本实用新型的技术方案如下:

4.一种基于sw3231处理器实现的计算机控制板,该计算机控制板包括:

5.sw3231处理器的8个64位数据宽度的ddr4存储器接口分别对应内置的8个支持ecc校验的ddr4存储控制器,sw3231处理器的8个ddr4存储器接口分别连接内存颗粒芯片;sw3231处理器还连接cpld芯片,sw3231处理器还连接flash芯片实现板载128g ssd硬盘,sw3231处理器还连接到计算机控制板对外提供的db9串口;

6.sw3231处理器的两组pciex4接口以及由一组pciex16接口所拆分出的两组pciex8接口分别连接到计算机控制板对外提供的4个pcie接口连接器的pice3.0x4接口;

7.sw3231处理器的另一组pciex16接口所拆分出的一组pciex8接口连接到pcie总线扩展芯片;

8.pcie总线扩展芯片连接pcie转usb芯片输出usb信号到计算机控制板对外提供usb3.0接口;

9.usb转多功能接口芯片连接pcie转usb芯片将usb信号转换成串口信号和jtag信号,串口信号输出到计算机控制板对外提供的4个pcie接口连接器的rs232串口,jtag信号输出到计算机控制板对外提供的4个pcie接口连接器的jtag接口;

10.pcie总线扩展芯片连接pcie转mdi芯片输出信号到计算机控制板对外提供的rj45千兆网络接口;

11.pcie总线扩展芯片连接pcie转sata芯片输出信号到计算机控制板对外提供的sata3.0接口;

12.pcie总线扩展芯片连接pcie转vga芯片连接计算机控制板对外提供的vga接口。

13.其进一步的技术方案为,sw3231处理器的每个ddr4存储器接口分别连接4个内存

颗粒芯片,计算机控制板共内置40颗x16颗粒的内存颗粒芯片,单颗内存颗粒芯片的容量1gb,计算机控制板板载实现32gb内存。

14.其进一步的技术方案为,内存颗粒芯片采用mt40a512m16ha

‑

062e。

15.其进一步的技术方案为,计算机控制板对外提供6个usb3.0接口,pcie转usb芯片包括两片upd720201芯片共提供8路usb信号,6路usb信号分别连接至6个usb3.0接口,其余2路usb信号连接至usb转多功能接口芯片形成4路串口信号和4路jtag信号。

16.其进一步的技术方案为,usb转多功能接口芯片包括两片ft4232hl芯片,每片ft4232hl芯片分别连接一路usb信号转换形成2路串口信号和2路jtag信号。

17.其进一步的技术方案为,每片ft4232hl芯片还分别连接两片max232芯片和两片sn74avch4t245芯片,每片ft4232hl芯片产生的每路串口信号分别经过max232芯片输出到一路pcie接口连接器的rs232串口,每片ft4232hl芯片产生的每路jtag信号分别经过sn74avch4t245芯片输出到一路pcie接口连接器的jtag接口。

18.其进一步的技术方案为,计算机控制板对外提供的sata3.0接口包括msata接口和7脚sata,pcie转sata芯片为88se9215芯片,88se9215芯片还连接flash芯片。

19.其进一步的技术方案为,pcie转vga芯片为sm750芯片,sm750芯片的ddr接口还连接4颗ddr sdram芯片,4颗ddr sdram芯片的总容量为64mb。

20.其进一步的技术方案为,计算机控制板对外提供两个rj45千兆网络接口,pcie转mdi芯片包括两片i210芯片,每片i210芯片分别连接到一个rj45千兆网络接口,每片i210芯片还分别连接flash芯片。

21.其进一步的技术方案为,计算机控制板还包括复位开关、电源开关、电源指示灯、硬盘指示灯和蜂鸣器。

22.本实用新型的有益技术效果是:

23.本技术公开了一种基于sw3231处理器实现的计算机控制板,该计算机控制板基于申威sw3231处理器实现,并对其外围接口电路进行了配套设计,提供了实际所需的各类接口,还设计了便于程序文件烧写的jtag接口,实用性强,提供上位机的控制功能,有效降低信息安全隐患,可广泛应用在信息安全领域,如航天航空、智能交通、电力铁路等行业。

附图说明

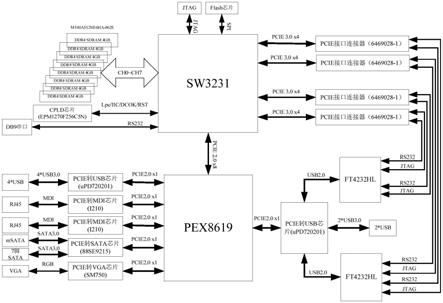

24.图1是本技术的计算机控制板的总体设计框图。

25.图2是本技术的计算机控制板中内存部分的设计框图。

26.图3是本技术的计算机控制板中pcie总线部分的设计框图。

27.图4是本技术的计算机控制板中usb接口部分的设计框图。

28.图5是本技术的计算机控制板中rs232串口及jtag接口部分的设计框图。

29.图6是本技术的计算机控制板中sata接口部分的设计框图。

30.图7是本技术的计算机控制板中rj45千兆网络接口部分的设计框图。

31.图8是本技术的计算机控制板中vga接口部分的设计框图。

32.图9是本技术的计算机控制板中供电示意图。

33.图10是本技术的计算机控制板的上电时序示意图。

具体实施方式

34.下面结合附图对本实用新型的具体实施方式做进一步说明。

35.本技术公开了一种基于sw3231处理器实现的计算机控制板,请参考图1所示的总体设计框图,该计算机控制板包括的主要器件有:sw3231处理器、内存颗粒芯片、cpld芯片、flash芯片、pcie总线扩展芯片、pcie转usb芯片、usb转多功能接口芯片、pcie转mdi芯片、pcie转sata芯片、pcie转vga芯片。

36.该计算机控制板对外提供的接口主要包括:4个pcie接口连接器、usb3.0接口、rj45千兆网络接口、vga接口、sata3.0接口和db9串口。

37.该计算机控制板的各部分方案设计如下:

38.(1)内存方案设计

39.sw3231处理器内部集成8个ddr4存储控制器,每个ddr4存储控制器对应1个64位数据宽度的ddr4存储器接口,且支持8位ecc校验,传输速率可达3200mbps。sw3231处理器的8个ddr4存储器接口分别连接内存颗粒芯片。为了充分利用cpu内存带宽,本技术采用8通道单rank方案设计,采用x16颗粒的内存颗粒芯片,单颗内存颗粒芯片的容量1gb,算机控制板共内置40颗内存颗粒芯片,每个ddr4存储器接口分别连接4个内存颗粒芯片,如图2所示,整个计算机控制板板载实现32gb内存。本技术中的内存颗粒芯片采用mt40a512m16ha

‑

062e。

40.(2)pcie方案设计

41.sw3231处理器集成最多6个符合4.0标准且向下兼容3.0/2.0标准的pcie接口,默认情况下具有4组pcie接口,其中两组(pe0和pe2)为x16接口,两组(pe1和pe3)为x4接口。

42.本技术按6个rc拆分处理器的pcie接口,将每组pciex16接口分别拆分成两组pciex8接口,其中两组pciex4接口以及由一组pciex16接口所拆分出的两组pciex8接口分别连接到计算机控制板对外提供的4个pcie接口连接器的pice3.0x4接口,如图3所示,另一组pciex16接口所拆分出的一组pciex8接口连接到pcie总线扩展芯片,还有一组pciex8接口不用。本技术中的pcie总线扩展芯片采用pex8619芯片。

43.(3)usb接口方案设计。

44.pcie总线扩展芯片连接pcie转usb芯片输出usb信号到计算机控制板对外提供usb3.0接口。本技术的计算机控制板对外提供6个usb3.0接口,pcie转usb芯片包括两片upd720201芯片共提供8路usb信号,其中6路usb信号分别连接至6个usb3.0接口,如图4所示。

45.(4)rs232串口和jtag接口方案设计。

46.usb转多功能接口芯片连接pcie转usb芯片将usb信号转换成串口信号和jtag信号,串口信号输出到计算机控制板对外提供的4个pcie接口连接器的rs232串口,jtag信号输出到计算机控制板对外提供的4个pcie接口连接器的jtag接口。如上所述,两片upd720201芯片共可以提供8路usb信号,而usb3.0接口只使用了其中6路usb信号,剩余2路usb信号连接至usb转多功能接口芯片形成4路串口信号和4路jtag信号。本技术中的usb转多功能接口芯片包括两片ft4232hl芯片,则每路usb信号连接到一片ft4232hl芯片,每片ft4232hl芯片分别将一路usb信号转换形成2路串口信号和2路jtag信号。

47.本技术中jtag接口所需电平为2.5v,而ft4232hl芯片转换出的jtag电平为3.3v,因此在本技术中,如图5所示,每片ft4232hl芯片还分别连接两片max232芯片和两片

sn74avch4t245芯片,每片ft4232hl芯片产生的每路串口信号分别经过max232芯片输出到一路pcie接口连接器的rs232串口,每片ft4232hl芯片的每路jtag信号分别经过sn74avch4t245芯片输出到一路pcie接口连接器的jtag接口,sn74avch4t245芯片为电平转换芯片,其将ft4232hl芯片输出的3.3v转换为2.5v连接至pcie接口连接器。

48.(5)sata接口方案设计。

49.pcie总线扩展芯片连接pcie转sata芯片输出信号到计算机控制板对外提供的sata3.0接口。本技术的计算机控制板对外提供的sata3.0接口包括msata接口和普通的7脚sata,msata接口通过插座as0b226

‑

s68q

‑

7h引出,普通的7脚sata通过插座ld1807v

‑

s51p引出。本技术使用的pcie转sata芯片为88se9215芯片,其连接2路sata3.0接口,如图6所示。88se9215芯片还连接flash芯片,速率为6gbps,ssd支持容量为128gb,存储类型采用mlc nand flash。

50.(6)以太网方案设计。

51.pcie总线扩展芯片连接pcie转mdi芯片输出信号到计算机控制板对外提供的rj45千兆网络接口。本技术的计算机控制板对外提供两个rj45千兆网络接口,所使用的pcie转mdi芯片包括两片i210芯片,每片i210芯片分别连接到一个rj45千兆网络接口,如图7所示每片i210芯片还分别连接flash芯片,烧写实现copper接口的固件,则该计算机控制板提供2路10/100/1000自适应电口。

52.(7)显示接口方案设计。

53.该计算机控制板集成显卡,pcie总线扩展芯片连接pcie转vga芯片连接计算机控制板对外提供的1路db15的vga接口。本技术使用的pcie转vga芯片为sm750芯片,显存采用external memory,sm750芯片的ddr接口还连接4颗ddr sdram芯片,4颗ddr sdram芯片的总容量为64mb,如图8所示。

54.除此之外,sw3231处理器还通过自带的lpc/iic/dcok/rst口连接cpld芯片,本技术使用的cpld芯片为epm1270f256c5n。sw3231处理器还连接flash芯片实现板载128g ssd硬盘,本技术使用的flash芯片为w25q16jvssig。sw3231处理器还通过自带的rs232口连接到计算机控制板对外提供的db9串口。除此之外,该计算机控制板还提供复位开关、电源开关、电源指示灯、硬盘指示灯和蜂鸣器等,这些都是现有的计算机控制板较为常规的组件,本技术不再详细介绍实现方案。

55.(8)电源方案设计。

56.该计算机控制板的供电为单一12v供电,12v通过四个pcie接口连接器馈入,同时可支持宽电压14v

‑

15v输入,通过电源管理芯片转换为各部分所需的电压,本技术所使用到的电源管理芯片主要有tps53319芯片、zldo1117

‑

adj芯片、aoz1232芯片、rt9059芯片、isl8225芯片、tps51200芯片、mp2888a芯片以及mp86945a芯片,电源方案框图如图9所示,主板功耗≤200w。基于图9所示的电路方案,本技术对该计算机控制板的上电时序介绍如下,请参考图10的时序示意图:

57.主板单电源12v供电后,直接输出待机电5v、3.3vsb和1.8vsb,此时cpld芯片正常工作,当按下主板上电开关时,可以产生一个低电平的脉宽信号cpld_psin给cpld芯片,cpld芯片产生后续电源模块工作的使能信号cpld_pson,该使能信号cpld_pson驱动电源芯片tps53319,产生3.3v电源,3.3v的powergood信号给到cpld芯片。3.3v的pg信号有效后,

cpld芯片输出驱动信号分别使能2个tps53319、rt9059产生2.5v、1.8v和1.1v电压,三个电源模块对应的pg信号输出给cpld。1.8v的pg信号有效后,cpld输出驱动信号分别使能aoz1232、tps53355、rt9059产生1v、1.2v(cpu)、1.2v(sm750),3个电源模块对应的pg信号输出给cpld芯片。1.2v的pg信号有效后,cpld输出驱动信号分别使能tps51200、isl68127多相电源产生0.6v和0.75v,2个电源模块对应的pg信号输出给cpld。所有电源模块的pg均有效后,输出驱动信号点亮板卡电源灯。

58.基于本技术所设计的这些结构,该计算机控制板的工作特性及功能如下:

59.(a)显示接口:集成显卡,1路db15的vga接口,分辨率根据外部显示器自适应,最高支持1920x1080分辨率。

60.(b)pcie接口:支持4路pcie总线,其中4路为x4的pcie 3.0接口,通过pcie接口连接器引出。

61.(c)sata接口:2路sata3.0信号,其中1路msata接口,1路7脚sata接口。

62.(d)存储:板载128g ssd硬盘。

63.(e)内存:板载不小于16gb ddr4 sdram,带ecc校验。

64.(f)以太网络:2路1000base

‑

t网络接口,提供2路rj45千兆网络接口。

65.(g)usb口:6路usb3.0接口,通过前面板usb3.0接口引出。

66.(h)串口:5路,4路内置rs232串口分别连接至四个pcie接口连接器,另有1路db9串口。

67.(i)jtag接口:电平标准2.5v,4路标准jtag接口,分别连接到四个pcie接口连接器。

68.以上所述的仅是本技术的优选实施方式,本实用新型不限于以上实施例。可以理解,本领域技术人员在不脱离本实用新型的精神和构思的前提下直接导出或联想到的其他改进和变化,均应认为包含在本实用新型的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1