输入电压保护的制作方法

输入电压保护

1.相关申请的交叉引用

2.本技术要求于2019年3月29日递交的、题为“输入电压保护(input voltage protection)”、发明人为uan

‑

zo

‑

li等人的美国专利申请序列号16/369,529的申请日的权益,并且通过引用将该申请并入本文。

技术领域

3.本公开涉及使用到处理器的扼制(throttle)来保护输入电压。例如,本公开还涉及允许处理器(例如,中央处理单元或者cpu)在更低的电压电平下进行操作,和/或保护处理器免受黑屏影响。

背景技术:

4.通过新的硅工艺来提高处理器性能、中央处理单元(central processing unit,cpu)性能和/或片上系统(system on chip,soc)性能正变得越来越困难。这可能导致soc(和/或处理器)的峰值功率的增大。此外,例如,泄漏在总的处理器或soc功耗中的百分比可变得越来越高。从动态电流的角度来看,功率病毒(power virus,pv)电流可能继续增长。

5.限制处理器核心电压或者vid(电压标识、核心电压和/或功能电压)可能很重要,并且关键是要确保核心电压不下降到低于最小值,例如由cpu工艺和频率限定的最小值。因此,在一些电力输送(power delivery,pd)实现方式中,所要求的电压设置可能是使用pv电流值来计算的。然而,增大电流比率,例如i(pv)/i(app)(功率病毒电流与应用电流的比率),可能导致诸如vid之类的功能电压的大幅增大,并且可能导致功率和性能损失。

附图说明

6.通过参考附图可更好地理解以下详细描述,附图包含所公开主题的许多特征的具体示例。

7.图1图示了根据一些实施例的系统;

8.图2图示了根据一些实施例的系统;

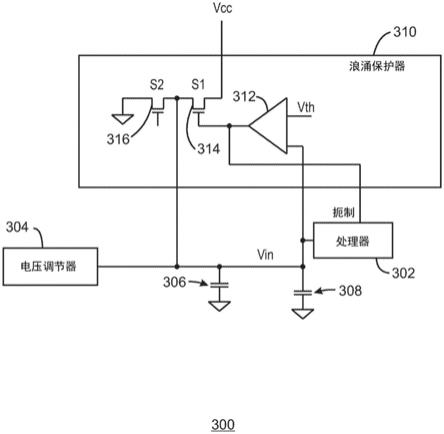

9.图3图示了根据一些实施例的系统;

10.图4图示了根据一些实施例的时序图;

11.图5图示了根据一些实施例的系统;

12.图6图示了根据一些实施例的时序图;

13.图7图示了根据一些实施例的系统;

14.图8图示了根据一些实施例的系统;

15.图9图示了根据一些实施例的系统;

16.图10图示了根据一些实施例的系统;

17.图11图示了根据一些实施例的系统;

18.图12图示了根据一些实施例的系统;

19.图13图示了根据一些实施例的系统;

20.图14图示了根据一些实施例的系统;

21.图15图示了根据一些实施例的计算系统;

22.图16图示了根据一些实施例的一个或多个处理器和一个或多个介质;

23.在一些情况下,相同的数字在本公开和附图各处用于表示相似的组件和特征。在一些情况下,100系列的数字指代最初出现于图1中的特征;200系列的数字指代最初出现于图2中的特征;等等。

具体实施方式

24.一些实施例涉及功率浪涌保护(power surge protection)。一些实施例涉及可提高性能和降低功耗的浪涌保护器(例如,可提高一个或多个处理器和/或一个或多个处理器核心的性能和降低功耗的浪涌保护器)。一些实施例涉及允许处理器(例如,中央处理单元或cpu)在较低的电压电平下进行操作(例如,通过保护处理器免受黑屏影响)。一些实施例允许处理器输入电压的电平被设置为低于最大处理器电流和最小处理器电压所要求的电平,而没有违反最小处理器电压的风险。

25.一些实施例涉及使用到处理器的扼制(和/或到处理器核心的扼制)来保护输入电压不下降到低于最小值(例如,保护处理器输入电压不下降到低于最小值)。在一些实施例中,如果处理器输入电压下降,则在扼制处理器的同时尽可能长时间地维持输入电压。例如,在一些实施例中,当输入电压接近阈值电压电平(或者最小电压电平)时,例如,监视输入电压的比较器可向处理器发送扼制信号,以扼制处理器。此外,在一些实施例中,可提供足够的电力,以为扼制机制的工作创造足够的时间,补充来自处理器的主电源的电力。

26.根据一些实施例,对处理器进行扼制可包括例如调整处理器的时钟速度。这也可被称为例如动态频率缩放。处理器扼制(例如,中央处理单元扼制)例如可用于自动减慢处理器以便使用更少的能量和节约电池。处理器扼制例如可包括调整处理器的频率,这可帮助节约电力和减少处理器生成的热量。扼制处理器还可包括停止执行某些指令(例如,停止执行不提供大量价值的指令)。此外,处理器的扼制可包括减小处理器的动态电容(cdyn)。处理器的扼制也可包括在管线中添加已知要求很少能量的指令。

27.在一些实施例中,由于实现了电压阈值保护,所以vid(处理器电压标识、核心电压和/或功能电压)可被设置到与它在其他情况下可能被设置的相比更低的值。由于处理器消耗的功率与电压平方(v2)成比例,所以当把vid设置到更低电平时,可能会有更少的处理器功耗。这可允许更高的处理器频率设置。

28.如上所述,限制处理器核心电压或vid可能很重要。这例如可通过确保vid(电压标识、核心电压和/或功能电压)不下降到低于最小值来实现。因此,在一些电力输送(pd)实现方式中,所要求的电压设置可能是使用pv电流值来计算的。然而,增大电流比率,例如i(pv)/i(app)(功率病毒电流与应用电流的比率),可能导致诸如vid之类的功能电压的大幅增大,并且可能导致功率和性能损失。

29.可基于核心和主板(mb)中的参数来设置处理器核心电压,例如中央处理单元(cpu)核心电压,这些参数会添加到最小核心电压。这些参数可能包括以下各项中的一项或多项:

30.最大核心电流(imax)

31.主板(mb)负载线(load line,ll),这可包括ac负载线和dc负载线

32.主板电压调节器(motherboard voltage regulator,mb vr)由于纹波、dc偏移和负载线不准确(例如电压容差带(voltage tolerance band,tob))而导致其输出电压不准确

33.制造中的额外保护带,包括可靠性、诸如ll2和ll1之类的负载线、磨损,等等(产品保护带用来确保质量和可靠性)。

34.诸如上述的参数可增大到处理器核心的输入电压。注意,在许多情况下,现实的核心峰值电流(峰值icore)可能比最大电流病毒(imax病毒)低得多,因为动态电容(cdyn)的应用比最坏情况的动态电容(最坏情况cdyn)低得多。此外,大多数主板电压调节器(mb vr)可能不会表现出可用于计算电压容差带(tob)的最坏情况场景。另外,产品保护带可能是针对病毒条件来估计的,并且可能考虑到负载线电压下降(例如,ll2电压下降)。更高的电压可能对处理器功耗产生很大的影响,因为动态功率与电压平方(v2)成比例,而泄漏功率至少与电压立方(至少v3)成比例。

35.一些soc电力输送实现方式使用一个或多个全集成电压调节器(fully integrated voltage regulator,fivr),其可使得负载线能够接近零(例如,实际上为零的ll3和ll2)。非线性控制器(nlc,例如nlc2)可用于减轻第一下降的影响。为了减小由主板电压调节器(mb vr)(例如,连接到fivr的输入轨道的mbvr)提供的电流,如果电流超过给定的值,则处理器可实现soc的扼制。

36.在一些实现方式中,可以检测和扼制与高频率带相关联的功率。非线性控制器(non

‑

linear controller,nlc)可被用作处理器核心电压的短期快速下降的安全网。然而,由于不断增大的处理器核心输出电压和fivr输入网上的下降,nlc的效率可能会降低。为了应对快速瞬变,可以启动fivr输入电压和处理器核心的输出平面之间的低阻抗连接。

37.在一些实施例中,可实现有利的益处,而不要求完全集成电压调节器(fivr)的底层框架。根据一些实施例,可以监视和管理中频行为(例如,从dc到几十mhz)。一些实施例使用替代电源,该替代电源使用可切换和可控制的路径连接到处理器(例如,到cpu、soc、处理器核心,等等)。管芯上专用电路可被用于监视封装解耦电容器上的电压。当电压(或者其时间导数,或者其时间积分,或者电压、其时间导数和其时间积分中的两个或更多个的组合)超过预定的阈值时,可发送信号来请求处理器扼制(例如,cpu、soc和/或核心扼制),并且将处理器连接到替代电源的路径可被切换到低阻抗,从而允许额外的电流流入处理器(例如,流入cpu、soc和/或核心等等)。以这种方式,过剩电流(例如,高于阈值的电流)需求可得到支持,直到它在扼制事件之后衰减为止。

38.在一些实施例中,可以使用额外的电源来延长扼制期间的“宽限期”。然而,在一些实施例中,处理器扼制(例如,cpu扼制)可能比阻抗峰值的频率更快。在这种情况下,在一些实施例中,可以在没有额外的电源来延长扼制期间的“宽限期”的情况下实现保护。

39.在一些实施例中,可以利用机器代码(例如,pcode)来为vid计算计入实际应用消耗。可能会发生(i

pv

‑

i

app

)*r

ll

的电压增益节省,其中i

pv

是功率病毒电流,i

app

是应用电流,并且r

ll

是负载线电阻。这例如可对应于大约50mv到大约150mv之间的电压节省的电压范围,这取决于具体产品和主板电压调节器(vr)特性。它还可减小保护带,甚至消除对保护带的需

求。这可帮助降低功耗。

40.在一些实施例中,为了防止处理器过载(例如,cpu、soc和/或处理器核心过载),管芯上电压监视器可包括最小和最大电压阈值两者。除了对高压替代电源的钳位以外,还可启用v

ss

钳位。因此,封装解耦电容上的电压可保持在预定的限度内。

41.在一些实施例中,可以减小最大电压(vmax)与最小电压(vmin)的差距。这可使得能够针对给定的频率设置更低的核心电压(vid),并且可实现更高的性能。另外,在一些实施例中,通过将有效的管芯上电压维持在预定的限度内,可减小可靠性保护带,可减小功耗,并且可提高性能。

42.图1图示了根据一些实施例的示例系统100的框图。系统100包括处理器102、电压调节器(vr)104、以及浪涌保护器110。在一些实施例中,处理器102例如可以是中央处理单元(cpu)、片上系统(soc)、和/或处理器核心。在一些实施例中,电压调节器104例如可以是主板电压调节器(mbvr)。

43.当核心电压或者输入电压(例如,电压vin)下降到低于设置的阈值电平(例如,电压vth)时,浪涌保护器110可向处理器102断言扼制信号。到处理器102的扼制信号可被用来确保核心电压(或者输入电压)vin不会下降到低于阈值电压vth。

44.在一些实施例中,浪涌保护器110包括监视电压vin(例如,监视封装解耦电容器上的电压)的管芯上专用电路。根据一些实施例,当这个电压(或者其时间导数,或者其时间积分,或者该电压、其时间导数和其时间积分中的两个或更多个的组合)超过预定的阈值(例如,超过阈值电压vth)时,扼制信号被发送以请求对处理器102进行扼制,以便扼制处理器102来保护输入电压vin,并且将处理器102连接到替代电源的路径可被切换到低阻抗,从而允许额外的电流流向处理器102。

45.图2图示了根据一些实施例的示例系统200的框图。系统200包括处理器202、电压调节器(vr)204、电容器206(例如,封装解耦电容器)、电容器208(例如,封装解耦电容器)、以及浪涌保护器210。在一些实施例中,处理器202例如可以是中央处理单元(cpu)、片上系统(soc)、和/或处理器核心。在一些实施例中,电压调节器204例如可以是主板电压调节器(mbvr)。

46.浪涌保护器210包括比较器212。当核心电压或者输入电压(例如,电压vin)下降到低于设置的阈值电平(例如,电压vth)时,比较器212可向处理器202断言扼制信号。到处理器202的扼制信号可被用来确保核心电压(或者输入电压)vin不会下降到低于阈值电压vth。

47.在一些实施例中,浪涌保护器210包括监视电压vin(例如,监视封装解耦电容器上的电压)的管芯上专用电路。根据一些实施例,当这个电压(或者其时间导数,或者其时间积分,或者该电压、其时间导数和其时间积分中的两个或更多个的组合)超过预定的阈值(例如,超过阈值电压vth)时,扼制信号被发送以请求对处理器202进行扼制,以便扼制处理器202来保护输入电压vin,并且将处理器202连接到替代电源的路径可被切换到低阻抗,从而允许额外的电流流向处理器202。

48.图3图示了根据一些实施例的示例系统300的框图。系统300包括处理器302、电压调节器(vr)304、电容器306(例如,封装解耦电容器)、电容器308(例如,封装解耦电容器)、以及浪涌保护器310。在一些实施例中,处理器302例如可以是中央处理单元(cpu)、片上系

统(soc)、和/或处理器核心。在一些实施例中,电压调节器304例如可以是主板电压调节器(mbvr)。

49.浪涌保护器310包括比较器312。当核心电压或者输入电压(例如,电压vin)下降到低于设置的阈值电平(例如,电压vth)时,比较器312可向处理器302断言扼制信号。到处理器302的扼制信号可被用来确保核心电压(或者输入电压)vin不会下降到低于阈值电压vth。在一些实施例中,输入电压(vin)相对于阈值电压(vth)被维持。例如,在一些实施例中,输入电压(vin)被维持在等于阈值电压(vth)的电平、略高于阈值电压(vth)的电平、或者介于处理器最小电压vmin和阈值电压vth之间的电平。在一些实施例中,例如,输入电压(vin)也可以(或者改为)被维持在最小工艺水平,或者被维持在介于阈值电压和最小处理器电压的电平之间。

50.浪涌保护器310包括比较器312、一些控制电路、以及在一些实施例中包括连接到更高输入电压vcc(例如,1.8v、3.3v等等的供应电压)的至少一个晶体管314(例如,场效应晶体管和/或开关s1)。浪涌保护器310还例如可包括连接到地电压的第二晶体管316(例如,场效应晶体管和/或开关s2)。当核心电压vin下降到低于设置的阈值电平(例如,电压vth)时,比较器312向处理器302断言扼制信号并且将开始操作晶体管314(或者开关s1),以便将电压vin调节到高于最小处理器电压(例如,vmin)。在一些实施例中,晶体管314和316(例如,开关s1和s2)可被操作以在滞后操作模式中控制电压vin。晶体管316(例如,开关s2)在一些实施例中可用于防止vin过冲。在一些实施例中,只有晶体管314(例如,开关s1)被切换。

51.在系统300中提供晶体管314和316(开关s1和s2),以用于在扼制速度不足以将电压vin维持得高于阈值电压vth(和/或高于vmin和/或高于vid)的情形中提供电力的实现方式。以这种方式,如果没有迅速提供扼制,则晶体管314和316可提供电力以补充主电源。然而,在一些实施例中,如果可以非常迅速地提供扼制,则晶体管314和316(开关s1和s2)可能是不必要的。例如,在这种情形中,可以使用系统200。

52.在一些实施例中,浪涌保护器310包括监视电压vin(例如,监视封装解耦电容器上的电压)的管芯上专用电路。根据一些实施例,当这个电压(或者其时间导数,或者其时间积分,或者该电压、其时间导数和其时间积分中的两个或更多个的组合)超过预定的阈值(例如,超过阈值电压vth)时,扼制信号被发送以请求对处理器302进行扼制,以便扼制处理器302来保护输入电压vin,并且将处理器302连接到替代电源的路径(例如,包括晶体管314和/或316的路径)被切换到低阻抗,从而允许额外的电流流向处理器302。

53.一些实施例允许降低vid电压(例如,电压标识和/或核心电压),因为可以保护处理器免受欠压下降的影响(例如,在病毒电流、主板电压调节器缺陷的情况下,例如在主板上同时发生所有控制器不准确的情形中,以及处理器在精确的峰值阻抗(例如,负载线或ll2等等)下吸取电流的情形中)。

54.在一些实施例中,由于实现了电压阈值保护,所以vid可被设置到与它在其他情况下可能被设置的相比更低的值。由于处理器消耗的功率与电压平方(v2)成比例,所以当把vid设置到更低电平时,可能会有更少的功耗。这可允许更高的频率设置。

55.图4图示了根据一些实施例的波形400。波形400可包括例如动态电容乘以频率(cdyn*f)波形402、输入电压(vin)波形404、以及扼制信号波形406。波形400可用于说明根

据一些实施例可如何使用处理器扼制来确保输入电压vin不会降低到低于阈值电压vth或者处理器最小电压vmin。

56.波形402包括不使用阈值电压保护的示例实现方式的波形(cdyn*f)422和使用阈值电压保护的示例实现方式的波形(cdyn*f)424。例如,波形424可说明根据(例如,由图3的系统300实现的)一些实施例的实现方式。注意,处理器消耗的总功率可与cdyn*f成比例,因此处理器消耗的功率可以以类似于波形402的方式来增大和减小。

57.波形404包括不使用阈值电压保护的示例实现方式的波形(vin)442和使用阈值电压保护的示例实现方式的波形(vin)444。例如,波形444可说明根据(例如,由图3的系统300实现的)一些实施例的实现方式。

58.波形406包括波形(扼制)464(例如,使用阈值电压保护的示例实现方式的波形(扼制)464,例如图3的系统300中说明的扼制信号)。

59.波形422和442说明了与不使用阈值电压保护来保护输入电压vin的系统有关的波形。vid(例如,主板vid)可被设置得足够高,使得即使有最坏的处理器扰动,处理器电压也将高于最小电平。波形422和442说明,如果处理器活动增加,并且处理器开始消耗更多的功率,则处理器输入电压vin下降,直到它达到某个值为止。当处理器随后减少其活动时,功率下降,并且电压vin恢复。

60.波形424和444说明了根据一些实施例的与使用阈值电压保护来保护输入电压vin的系统有关的波形。例如,波形424和444可说明与使用浪涌保护器310的图3的系统300有关的波形。在一些实施例中,vid(例如,主板vid)可被设置得更低,并且由于更低的电压,处理器功耗可更低,并且实际处理器频率可更高。当处理器使用率由于更高的应用比率而激增时,处理器开始消耗更多的功率,并且处理器输入电压(vin)可开始下降。然而,根据一些实施例,可以检测到输入电压(vin)的低于阈值电平(vth)的下降(例如,使用浪涌保护器,例如浪涌保护器310)。当检测到输入电压(vin)已下降到低于阈值电平(vth)时,例如,可发送扼制信号(扼制)以命令处理器进行扼制,并且可提供电力来维持处理器输入电压(vin)略高于阈值(vth),如波形424、444和464所说明。虽然在图4中不一定图示了,但在一些实施例中,例如,输入电压(vin)也可以(或者改为)被维持在最小工艺水平,或者被维持在介于阈值电压和最小处理器电压的电平之间。

61.在一些实施例中,如图4中的波形所示,例如,频率f可被增大,并且性能可得到提高,因为一旦实现了处理器的扼制,就可以较少担心电压下降到低于阈值电压。这在图4中例如由波形424的部分高于图4中波形422的相应部分来说明。因此,在一些实施例中,由于实现了电压阈值保护,所以vid可被设置到与它在其他情况下可能被设置的相比更低的值。由于处理器消耗的功率与电压平方(v2)成比例,所以当把vid设置到更低电平时,可能会有更少的功耗。这可允许更高的频率设置。

62.可以实现许多不同的实施例,以将输入电压(vin)控制在这个电平(例如,略高于阈值电压vth,处于最小工艺水平,和/或介于阈值电压和最小处理器电压的电平之间)。根据一些实施例,例如,除其他外,可以实现以下各项中的一项或多项:

63.开关的滞后控制,例如开关s1,有可能还使用开关s2来克服过冲;

64.具有高电阻的开关的阵列(代替s1或者除s1外),以及控制器来接通和/或关断部分或者全部开关,以便将电压维持在略高于阈值电平的电平(在一些实施例中,例如,电压

也可以或者改为被维持在最小工艺水平,或者被维持在介于阈值电压和最小处理器电压的电平之间)。

65.使用线性调节器(代替s1或者除s1外),其电阻由控制器直接控制,以维持vccin电压;和/或

66.使用切换式电压调节器(代替s1或者除s1外),具有串联的已知和/或预定的寄生电感(例如,传统降压转换器的模拟版)。

67.在一些实施例中,可以为特定的持续时间设置扼制,和/或扼制可在给定的延迟之后被解除断言。在一些实施例中,电压调节器可在延迟时间期满之后被关闭,和/或因为电压超过了上限而被关闭。在一些实施例中,延迟的持续时间可基于扼制功能的延迟(例如,基于扼制处理器、cpu、soc和/或核心要花费多少时间,等等)。

68.图5图示了根据一些实施例的示例系统500的框图。在一些实施例中,系统500可以与系统300相似或相同,其中从系统中去除了晶体管316(开关s2)。系统500包括处理器502、电压调节器(vr)504、电容器506(例如,封装解耦电容器)、电容器508(例如,封装解耦电容器)、以及浪涌保护器510。在一些实施例中,处理器502例如可以是中央处理单元(cpu)、片上系统(soc)、和/或处理器核心。在一些实施例中,电压调节器504例如可以是主板电压调节器(mbvr)。

69.浪涌保护器510包括比较器512。当核心电压或者输入电压(例如,电压vin)下降到低于设置的阈值电平(例如,电压vth)时,比较器512可向处理器502断言扼制信号。到处理器502的扼制信号可被用来确保核心电压(或者输入电压)vin不会下降到低于阈值电压vth。在一些实施例中,输入电压(vin)相对于阈值电压(vth)被维持。例如,在一些实施例中,输入电压(vin)被维持在等于阈值电压(vth)的电平、略高于阈值电压(vth)的电平、或者介于处理器最小电压vmin和阈值电压vth之间的电平。在一些实施例中,例如,输入电压(vin)也可以(或者改为)被维持在最小工艺水平,或者被维持在介于阈值电压和最小处理器电压的电平之间。

70.浪涌保护器510包括比较器512、一些控制电路、以及连接到更高输入电压vcc(例如,1.8v、3.3v等等的供应电压)的晶体管514(例如,场效应晶体管和/或开关s1)。当核心电压vin下降到低于设置的阈值电平(例如,电压vth)时,比较器512向处理器502断言扼制信号并且将开始操作晶体管514(或者开关s1),以便将电压vin调节到高于最小处理器电压(例如,vmin)。

71.在一些实施例中,浪涌保护器510包括监视电压vin(例如,监视封装解耦电容器上的电压)的管芯上专用电路。根据一些实施例,当这个电压(或者其时间导数,或者其时间积分,或者该电压、其时间导数和其时间积分中的两个或更多个的组合)超过预定的阈值(例如,超过阈值电压vth)时,扼制信号被发送以请求对处理器502进行扼制,以便扼制处理器502来保护输入电压vin,并且将处理器502连接到替代电源的路径(例如,包括晶体管514的路径)被切换到低阻抗,从而允许额外的电流流向处理器502。

72.图6图示了根据一些实施例的波形600。波形600可包括例如动态电容乘以频率(cdyn*f)波形602、输入电压(vin)波形604、以及扼制信号波形606。波形600可用于说明根据一些实施例可如何使用处理器扼制来确保输入电压vin不会降低到低于阈值电压vth。

73.波形602包括不使用阈值电压保护的示例实现方式的波形(cdyn*f)622和使用阈

值电压保护的示例实现方式的波形(cdyn*f)624。例如,波形624可说明根据(例如,由图5的系统500实现的)一些实施例的实现方式。注意,处理器消耗的总功率可与cdyn*f成比例,因此处理器消耗的功率可以以类似于波形602的方式来增大和减小。

74.波形606包括不使用阈值电压保护的示例实现方式的波形(vin)642和使用阈值电压保护的示例实现方式的波形(vin)644。例如,波形644可说明根据(例如,由图5的系统500实现的)一些实施例的实现方式。

75.波形606包括波形(扼制)664(例如,使用阈值电压保护的示例实现方式的波形(扼制)664,例如图5的系统500中说明的扼制信号)。

76.波形622和642说明了与不使用阈值电压保护来保护输入电压vin的系统有关的波形。vid(例如,主板vid)可被设置得足够高,使得即使有最坏的处理器扰动,处理器电压也将高于最小电平。波形622和642说明,如果处理器活动增加,并且处理器开始消耗更多的功率,则处理器输入电压vin下降,直到它达到某个值为止。当处理器随后减少其活动时,功率下降,并且电压vin恢复。

77.波形624和644说明了根据一些实施例的与使用阈值电压保护来保护输入电压vin的系统有关的波形。例如,波形624和644可说明与使用浪涌保护器510的图5的系统500有关的波形。在一些实施例中,vid(例如,主板vid)可被设置得更低,并且由于更低的电压,处理器功耗可更低,并且实际处理器频率可更高。当处理器使用率由于更高的应用比率而激增时,处理器开始消耗更多的功率,并且处理器输入电压(vin)可开始下降。然而,根据一些实施例,可以检测到输入电压(vin)的低于阈值电平(vth)的下降(例如,使用浪涌保护器,例如浪涌保护器510)。当检测到输入电压(vin)已下降到低于阈值电平(vth)时,例如,可发送扼制信号(扼制)以命令处理器进行扼制,并且可提供电力来维持处理器输入电压(vin)略高于阈值(vth),如波形624、644和664所说明。虽然在图6中不一定图示了,但在一些实施例中,例如,输入电压(vin)也可以(或者改为)被维持在最小工艺水平,或者被维持在介于阈值电压和最小处理器电压的电平之间。

78.在一些实施例中,如图6中的波形所示,例如,频率f可被增大,并且性能可得到提高,因为一旦实现了处理器的扼制,就可以较少担心电压下降到低于阈值电压。这在图6中例如由波形624的部分高于图6中波形622的相应部分来说明。因此,在一些实施例中,由于实现了电压阈值保护,所以vid可被设置到与它在其他情况下可能被设置的相比更低的值。由于处理器消耗的功率与电压平方(v2)成比例,所以当把vid设置到更低电平时,可能会有更少的功耗。这可允许更高的频率设置。

79.图7图示了根据一些实施例的时序图700。在一些实施例中,时序图700包括说明输入电压vin随时间变化的波形704。例如,在一些实施例中,波形704涉及诸如图5的系统500之类的系统,在该系统中可以实现阈值电压保护(例如,通过扼制处理器来保护输入电压(例如,vin),和/或将其相对于阈值电压(例如,vth)进行维持)。如图7所示,当开关s1(例如,晶体管514)接通时,输入电压vin从最小电压vmin增大到最大电压vmax。类似地,如图7所示,当开关s1(例如,晶体管514)关断时,输入电压vin从最大电压vmax下降到最小电压vmin。

80.图8图示了根据一些实施例的示例系统800的框图。系统800包括处理器802、电压调节器(vr)804、电容器806(例如,封装解耦电容器)、电容器808(例如,封装解耦电容器)、

以及浪涌保护器810。在一些实施例中,处理器802例如可以是中央处理单元(cpu)、片上系统(soc)、和/或处理器核心。在一些实施例中,电压调节器804例如可以是主板电压调节器(mbvr)。

81.浪涌保护器810包括比较器812。当核心电压或者输入电压(例如,电压vin)下降到低于设置的阈值电平(例如,电压vth)时,比较器812可向处理器802断言扼制信号。到处理器802的扼制信号可被用来确保核心电压(或者输入电压)vin不会下降到低于阈值电压vth。

82.浪涌保护器810包括比较器812、一些控制电路、以及连接到更高输入电压vcc(例如,1.8v、3.3v等等的供应电压)的至少一个晶体管(例如,场效应晶体管和/或开关)。浪涌保护器810可包括比较器810、晶体管816、以及开关的阵列820(例如,晶体管的阵列,和/或场效应晶体管的阵列)。在一些实施例中,系统800与图3的系统300相似或相同,在系统800中开关的阵列820替换了晶体管314(开关s1)(或者是额外添加了开关的阵列820)。在一些实施例中,开关的阵列820是具有高电阻的开关的阵列。在一些实施例中,输入电压(vin)相对于阈值电压(vth)被维持。例如,在一些实施例中,输入电压(vin)被维持在等于阈值电压(vth)的电平、略高于阈值电压(vth)的电平、或者介于处理器最小电压vmin和阈值电压vth之间的电平。在一些实施例中,例如,输入电压(vin)也可以(或者改为)被维持在最小工艺水平,或者被维持在介于阈值电压和最小处理器电压的电平之间。在一些实施例中,控制器可将阵列820中的一些开关接通和/或关断以相对于阈值电压vth来维持输入电压vin(例如,维持在阈值电压vth,维持在略高于阈值电压vth,维持在介于处理器最小电压vmin和阈值电压vth之间,或者维持在某个其他电压电平)。

83.第二晶体管816(例如,场效应晶体管和/或开关s2)例如连接到地电压。当核心电压vin下降到低于设置的阈值电平(例如,电压vth)时,比较器812向处理器802断言扼制信号并且将开始操作开关的阵列820,以便将电压vin调节到等于或高于最小处理器电压(例如,vmin)。在一些实施例中,晶体管816和开关的阵列820可被操作以在滞后操作模式中控制电压vin。晶体管816在一些实施例中可用于防止vin过冲。在一些实施例中,只有开关的阵列820中的开关被切换,而晶体管816不被切换。

84.在一些实施例中,浪涌保护器810包括监视电压vin(例如,监视封装解耦电容器上的电压)的管芯上专用电路。根据一些实施例,当这个电压(或者其时间导数,或者其时间积分,或者该电压、其时间导数和其时间积分中的两个或更多个的组合)超过预定的阈值(例如,超过阈值电压vth)时,扼制信号被发送以请求对处理器802进行扼制,以便扼制处理器802来保护输入电压vin,并且将处理器802连接到替代电源的路径(例如,包括开关的阵列820和/或晶体管816的路径)被切换到低阻抗,从而允许额外的电流流向处理器802。

85.图9图示了根据一些实施例的示例系统900的框图。系统900包括处理器902、电压调节器(vr)904、电容器906(例如,封装解耦电容器)、电容器908(例如,封装解耦电容器)、以及浪涌保护器910。在一些实施例中,处理器902例如可以是中央处理单元(cpu)、片上系统(soc)、和/或处理器核心。在一些实施例中,电压调节器904例如可以是主板电压调节器(mbvr)。

86.浪涌保护器910包括比较器922、924、926和928。当核心电压或者输入电压(例如,电压vin)下降到低于设置的阈值电平(例如,电压vth4)时,比较器928可向处理器902断言

扼制信号。到处理器902的扼制信号可被用来确保核心电压(或者输入电压)vin不会下降到低于阈值电压vth4。

87.浪涌保护器910包括比较器922、924、926和928,一些控制电路,以及晶体管的阵列932、934和936(例如,场效应晶体管的阵列932、934、936和/或开关的阵列932、934、936)。根据一些实施例,可以使用任何数量的晶体管932、934和936以及任何数量的比较器922、924、926和928。晶体管932、934和936连接到更高的输入电压vcc(例如,1.8v、3.3v等等的供应电压)。浪涌保护器910可包括比较器的阵列和开关的阵列(例如,晶体管的阵列,和/或场效应晶体管的阵列)。在一些实施例中,系统900与图3的系统300、图5的系统500和/或图8的系统800相似或者相同。在一些实施例中,开关的阵列932、934、936是具有高电阻的开关的阵列。在一些实施例中,输入电压(vin)相对于阈值电压(vth1、vth2、vth3和/或vth4)被维持。例如,在一些实施例中,输入电压(vin)被维持在略高于阈值电压(vth1、vth2、vth3和/或vth4)的电平。在一些实施例中,例如,输入电压(vin)也可以(或者改为)被维持在最小工艺水平,或者被维持在介于阈值电压和最小处理器电压的电平之间。在一些实施例中,控制器可接通和/或关断阵列中的一些开关932、934、936,以相对于一个或多个阈值电压vth来维持输入电压vin(例如,维持在略高于一个或多个阈值电压,或者维持在某个其他电压电平)。

88.当核心电压vin下降到低于设置的阈值电平(例如,电压vth1、vth2、vth3和/或vth4,和/或这些电压的组合)时,比较器928向处理器902断言扼制信号并且将开始操作开关的阵列932、934、936和/或比较器922、924、926,以便将电压vin调节到等于或高于最小处理器电压(例如,vmin)。在一些实施例中,开关的阵列可被操作以在滞后操作模式中控制电压vin。晶体管中的一个或多个在一些实施例中可被用于防止vin过冲。在一些实施例中,开关的阵列中只有一些开关被切换,而其他的开关不被切换。

89.在一些实施例中,浪涌保护器910包括监视电压vin(例如,监视封装解耦电容器上的电压)的管芯上专用电路。根据一些实施例,当这个电压(或者其时间导数,或者其时间积分,或者该电压、其时间导数和其时间积分中的两个或更多个的组合)超过预定的阈值(例如,超过阈值电压vth1、vth2、vth3、vth4和/或其某种组合)时,扼制信号被发送以请求对处理器902进行扼制,以便扼制处理器902来保护输入电压vin,并且将处理器902连接到替代电源的路径(例如,包括开关的阵列中的一个或多个的路径)被切换到低阻抗,从而允许额外的电流流向处理器902。

90.图10图示了根据一些实施例的示例系统1000的框图。系统1000包括处理器1002、电压调节器(vr)1004、电容器1006(例如,封装解耦电容器)、电容器1008(例如,封装解耦电容器)、以及浪涌保护器1010。在一些实施例中,处理器1002例如可以是中央处理单元(cpu)、片上系统(soc)、和/或处理器核心。在一些实施例中,电压调节器1004例如可以是主板电压调节器(mbvr)。

91.浪涌保护器1010包括比较器1012。当核心电压或者输入电压(例如,电压vin)下降到低于设置的阈值电平(例如,电压vth)时,比较器1012可向处理器1002断言扼制信号。到处理器1002的扼制信号可被用来确保核心电压(或者输入电压)vin不会下降到低于阈值电压vth。

92.浪涌保护器1010包括比较器1012和一些控制电路。浪涌保护器1010还可包括线性

调节器1020和/或连接到更高输入电压vcc(例如,1.8v、3.3v等等的供应电压)的至少一个晶体管(例如,场效应晶体管和/或开关)。浪涌保护器1010可包括比较器1012、晶体管1016、以及线性调节器1020。在一些实施例中,系统1000与图3的系统300相似或相同,在系统1000中线性调节器1020替换了晶体管314(开关s1)(或者是额外添加了线性调节器1020)。在一些实施例中,线性调节器1020的电阻由控制器直接控制以维持vccin电压。在一些实施例中,输入电压(vin)相对于阈值电压(vth)被维持。例如,在一些实施例中,输入电压(vin)被维持在等于阈值电压(vth)的电平、略高于阈值电压(vth)的电平、或者介于处理器最小电压vmin和阈值电压vth之间的电平。在一些实施例中,例如,输入电压(vin)也可以(或者改为)被维持在最小工艺水平,或者被维持在介于阈值电压和最小处理器电压的电平之间。在一些实施例中,控制器可控制线性调节器1020以相对于阈值电压vth来维持输入电压vin(例如,维持在阈值电压vth,维持在略高于阈值电压vth,维持在介于处理器最小电压vmin和阈值电压vth之间,或者维持在某个其他电压电平)。

93.第二晶体管1016(例如,场效应晶体管和/或开关s2)例如连接到地电压。当核心电压vin下降到低于设置的阈值电平(例如,电压vth)时,比较器1012向处理器1002断言扼制信号并且将开始操作线性调节器1020,以便将电压vin调节到高于最小处理器电压(例如,vmin)。在一些实施例中,晶体管1016和线性调节器1020可被操作以在滞后操作模式中控制电压vin。晶体管1016在一些实施例中可被用来防止vin过冲。在一些实施例中,晶体管1016不被切换。

94.在一些实施例中,浪涌保护器1010包括监视电压vin(例如,监视封装解耦电容器上的电压)的管芯上专用电路。根据一些实施例,当这个电压(或者其时间导数,或者其时间积分,或者该电压、其时间导数和其时间积分中的两个或更多个的组合)超过预定的阈值(例如,超过阈值电压vth)时,扼制信号被发送以请求对处理器1002进行扼制,以便扼制处理器1002来保护输入电压vin,并且将处理器1002连接到替代电源的路径(例如,包括线性调节器1020和/或晶体管1016的路径)被切换到低阻抗,从而允许额外的电流流向处理器1002。

95.图11图示了根据一些实施例的示例系统1100的框图。系统1100包括处理器1102、电压调节器(vr)1104、电容器1106(例如,封装解耦电容器)、电容器1108(例如,封装解耦电容器)、以及浪涌保护器1110。在一些实施例中,处理器1102例如可以是中央处理单元(cpu)、片上系统(soc)、和/或处理器核心。在一些实施例中,电压调节器1104例如可以是主板电压调节器(mbvr)。

96.浪涌保护器1110包括比较器1112。当核心电压或者输入电压(例如,电压vin)下降到低于设置的阈值电平(例如,电压vth)时,比较器1112可向处理器1102断言扼制信号。到处理器1102的扼制信号可被用来确保核心电压(或者输入电压)vin不会下降到低于阈值电压vth。

97.浪涌保护器1110包括比较器1112和一些控制电路。浪涌保护器1110包括阻抗1132(z1)和1134(z2)。浪涌保护器1110还可包括线性调节器和/或连接到更高输入电压vcc(例如,1.8v、3.3v等等的供应电压)的至少一个晶体管1114(例如,场效应晶体管和/或开关)。浪涌保护器1110可包括比较器1112、晶体管1114、以及线性调节器。在一些实施例中,晶体管1114(开关s1)可被用作线性调节器。在一些实施例中,系统1100与图3的系统300相似或

相同,在系统1100中线性调节器替换了晶体管314(开关s1)(或者是额外添加了线性调节器)。在一些实施例中,线性调节器的电阻由控制器直接控制以维持vccin电压。在一些实施例中,输入电压(vin)相对于阈值电压(vth)被维持。例如,在一些实施例中,输入电压(vin)被维持在等于阈值电压(vth)的电平、略高于阈值电压(vth)的电平、或者介于处理器最小电压vmin和阈值电压vth之间的电平。在一些实施例中,例如,输入电压(vin)也可以(或者改为)被维持在最小工艺水平,或者被维持在介于阈值电压和最小处理器电压的电平之间。在一些实施例中,控制器可控制线性调节器以相对于阈值电压vth来维持输入电压vin(例如,维持在阈值电压vth,维持在略高于阈值电压vth,维持在介于处理器最小电压vmin和阈值电压vth之间,或者维持在某个其他电压电平)。

98.第二晶体管1114(例如,场效应晶体管和/或开关s1)例如连接到地电压。当核心电压vin下降到低于设置的阈值电平(例如,电压vth)时,比较器1112向处理器1102断言扼制信号并且将开始操作线性调节器,以便将电压vin调节到高于最小处理器电压(例如,vmin)。在一些实施例中,晶体管1114和线性调节器可被操作以控制电压vin。晶体管1114在一些实施例中可被用来防止vin过冲。在一些实施例中,晶体管1114不被切换。

99.在一些实施例中,浪涌保护器1110包括监视电压vin(例如,监视封装解耦电容器上的电压)的管芯上专用电路。根据一些实施例,当这个电压(或者其时间导数,或者其时间积分,或者该电压、其时间导数和其时间积分中的两个或更多个的组合)超过预定的阈值(例如,超过阈值电压vth)时,扼制信号被发送以请求对处理器1102进行扼制,以便扼制处理器1102来保护输入电压vin,并且将处理器1102连接到替代电源的路径(例如,包括线性调节器和/或晶体管1114的路径)被切换到低阻抗,从而允许额外的电流流向处理器1102。

100.图12图示了根据一些实施例的示例系统1200的框图。系统1200包括处理器1202、电压调节器(vr)1204、电容器1206(例如,封装解耦电容器)、电容器1208(例如,封装解耦电容器)、以及浪涌保护器1210。在一些实施例中,处理器1202例如可以是中央处理单元(cpu)、片上系统(soc)、和/或处理器核心。在一些实施例中,电压调节器1204例如可以是主板电压调节器(mbvr)。

101.浪涌保护器1210包括比较器1212。当核心电压或者输入电压(例如,电压vin)下降到低于设置的阈值电平(例如,电压vth)时,比较器1212可向处理器1202断言扼制信号。到处理器1202的扼制信号可被用来确保核心电压(或者输入电压)vin不会下降到低于阈值电压vth。

102.浪涌保护器1210包括比较器1212和一些控制电路。浪涌保护器1210还可包括切换式电压调节器1220和/或连接到更高输入电压vcc(例如,1.8v、3.3v等等的供应电压)的至少一个晶体管(例如,场效应晶体管和/或开关)。浪涌保护器1210可包括比较器1212、晶体管1216、以及切换式电压调节器1220。在一些实施例中,系统1200与图3的系统300相似或相同,在系统1200中切换式电压调节器1220替换了晶体管314(开关s1)(或者是额外添加了切换式电压调节器1220)。在一些实施例中,切换式电压调节器1220可以是具有串联的已知和/或预定寄生电感的切换式电压调节器(例如,传统降压转换器的模拟版)。在一些实施例中,输入电压(vin)相对于阈值电压(vth)被维持。例如,在一些实施例中,输入电压(vin)被维持在等于阈值电压(vth)的电平、略高于阈值电压(vth)的电平、或者介于处理器最小电压vmin和阈值电压vth之间的电平。在一些实施例中,例如,输入电压(vin)也可以(或者改

为)被维持在最小工艺水平,或者被维持在介于阈值电压和最小处理器电压的电平之间。在一些实施例中,控制器可控制切换式电压调节器1220以相对于阈值电压vth来维持输入电压vin(例如,维持在阈值电压vth,维持在略高于阈值电压vth,维持在介于处理器最小电压vmin和阈值电压vth之间,或者维持在某个其他电压电平)。

103.第二晶体管1216(例如,场效应晶体管和/或开关s2)例如连接到地电压。当核心电压vin下降到低于设置的阈值电平(例如,电压vth)时,比较器1212向处理器1202断言扼制信号并且将开始操作切换式电压调节器1220,以便将电压vin调节到高于最小处理器电压(例如,vmin)。在一些实施例中,晶体管1216和切换式电压调节器1220可被操作以在滞后操作模式中控制电压vin。晶体管1216在一些实施例中可被用来防止vin过冲。在一些实施例中,晶体管1216不被切换。

104.在一些实施例中,浪涌保护器1210包括监视电压vin(例如,监视封装解耦电容器上的电压)的管芯上专用电路。根据一些实施例,当这个电压(或者其时间导数,或者其时间积分,或者该电压、其时间导数和其时间积分中的两个或更多个的组合)超过预定的阈值(例如,超过阈值电压vth)时,扼制信号被发送以请求对处理器1202进行扼制,以便扼制处理器1202来保护输入电压vin,并且将处理器1202连接到替代电源的路径(例如,包括切换式电压调节器1220和/或晶体管1216的路径)被切换到低阻抗,从而允许额外的电流流向处理器1202。

105.图13图示了根据一些实施例的示例系统1300的框图。系统1300包括处理器1302、电压调节器(vr)1304、电容器1306(例如,封装解耦电容器)、电容器1308(例如,封装解耦电容器)、以及浪涌保护器1310。在一些实施例中,处理器1302例如可以是中央处理单元(cpu)、片上系统(soc)、和/或处理器核心。在一些实施例中,电压调节器1304例如可以是主板电压调节器(mbvr)。

106.浪涌保护器1310包括比较器1312。当核心电压或者输入电压(例如,电压vin)下降到低于设置的阈值电平(例如,电压vth)时,比较器1312可向处理器1302断言扼制信号。到处理器1302的扼制信号可被用来确保核心电压(或者输入电压)vin不会下降到低于阈值电压vth。

107.浪涌保护器1310包括比较器1312和一些控制电路。浪涌保护器1310还可包括降压转换器(例如,替代图3的开关s1的降压转换器)。降压转换器可包括开关1314、开关1316、以及电感器1344。在一些实施例中,浪涌保护器1310可包括驱动器1342来驱动降压转换器。在一些实施例中,降压转换器可以是切换式电压调节器。在一些实施例中,降压转换器可以是具有串联的已知和/或预定寄生电感的切换式电压调节器。

108.在一些实施例中,开关1314(s1)可连接到更高输入电压vcc(例如,1.8v、3.3v等等的供应电压)。浪涌保护器1310可包括比较器1312、晶体管1314和1316、切换式电压调节器、和/或降压转换器。在一些实施例中,系统1300与图3的系统300相似或相同,在系统1300中降压转换器和/或切换式电压调节器替换了晶体管314(开关s1)(或者是额外添加了降压转换器和/或切换式电压调节器)。在一些实施例中,降压转换器和/或切换式电压调节器可以是具有串联的已知和/或预定寄生电感的切换式电压调节器(例如,传统降压转换器的模拟版)。在一些实施例中,输入电压(vin)相对于阈值电压(vth)被维持。例如,在一些实施例中,输入电压(vin)被维持在等于阈值电压(vth)的电平、略高于阈值电压(vth)的电平、或

者介于处理器最小电压vmin和阈值电压vth之间的电平。在一些实施例中,例如,输入电压(vin)也可以(或者改为)被维持在最小工艺水平,或者被维持在介于阈值电压和最小处理器电压的电平之间。在一些实施例中,控制器可控制降压转换器和/或切换式电压调节器以相对于阈值电压vth来维持输入电压vin(例如,维持在阈值电压vth,维持在略高于阈值电压vth,维持在介于处理器最小电压vmin和阈值电压vth之间,或者维持在某个其他电压电平)。

109.第二晶体管1316(例如,场效应晶体管和/或开关s2)例如连接到地电压。当核心电压vin下降到低于设置的阈值电平(例如,电压vth)时,比较器1312向处理器1302断言扼制信号并且将开始操作切换式电压调节器和/或降压转换器,以便将电压vin调节到高于最小处理器电压(例如,vmin)。在一些实施例中,晶体管1314和1316、切换式电压调节器、降压转换器和/或电感器可被操作以控制电压vin。

110.在一些实施例中,浪涌保护器1310包括监视电压vin(例如,监视封装解耦电容器上的电压)的管芯上专用电路。根据一些实施例,当这个电压(或者其时间导数,或者其时间积分,或者该电压、其时间导数和其时间积分中的两个或更多个的组合)超过预定的阈值(例如,超过阈值电压vth)时,扼制信号被发送以请求对处理器1302进行扼制,以便扼制处理器1302来保护输入电压vin,并且将处理器1302连接到替代电源的路径(例如,包括切换式电压调节器和/或降压转换器的路径)被切换到低阻抗,从而允许额外的电流流向处理器1302。

111.通常可基于以下公式来计算处理器vid(例如,cpu vid):

112.vid=vmin+tob+imax*ll3+cmv

113.其中vid是电压标识、核心电压、和/或功能电压,等等。

114.vmin是最小电压,例如最小核心电压。

115.tob是电压容差带,与例如由于纹波、dc电压偏移和负载线误差引起的主板电压调节器(vr)容差有关。

116.imax*ll3是由于英特尔移动电压定位(intel mobile voltage positioning,imvp)容差带引起的,与例如以下技术有关:由主板电压调节器(vr)基于处理器活动来动态地调整处理器电压,以降低处理器功率。

117.imax是峰值电流,例如峰值核心电流。

118.ll3是主板负载线。

119.cmv是电路边缘性验证(例如,制造保护带(包括用于第二下降ll2的保护带)和/或核心之间的封装/管芯电压的电位差)。

120.在一些实施例中,例如,保护带的一些部分被忽略,其中vid设置消除了大量的保护带,并且尝试更接近vmin。这可帮助降低功耗。

121.图14图示了根据一些实施例的pid(比例

‑

积分

‑

导数)控制器系统1400的框图。pid系统1400包括求和1402、求和1404、pid 1结果1406、pid 2结果1408、求和1410、以及pid 3结果1412。求和1402加上扼制计数并且减去扼制参考,以获得相应的pid 1结果1406。pid 1结果1406也可对应于vid(例如,电压标识、核心电压和/或功能电压等等)。求和1404加上温度参考并且减去核心温度,以获得相应的pid 2结果1408。求和1410加上pid 2结果1408并且减去pid 1结果1406(vid),以获得相应的pid 3结果1412,它可对应于频率f。

122.可根据一些实施例来实现系统1400以提供反馈机制。例如,如果vid被激进地降低,并且处理器正在运行消耗大量功率的应用,则根据一些实施例可能会发生大量的扼制。在这种情形中可以使用系统1400来监视有多少扼制正在发生。如果系统1400识别出正在发生大量的扼制(例如,使用求和1402),则系统1400随后也可确定vid可能需要被增大。虽然增大vid可能牺牲功率,但在某些情况下可能是有益的。例如,当vid被增大时,处理器频率可被系统1400增大。然而,在一些实施例中,当vid被增大时,降低频率(至少在某个时间段内)可能是有益的。此外,在一些实施例中,当vid被增大时,系统1400可将频率维持在相同水平。另外,在一些实施例中,求和1402和pid 1 1406可与系统1400的其余部分处于分开的环路中。也就是说,在一些实施例中,温度感测和频率调整可在一个环路中,而扼制计数和vid确定可在单独的环路中。

123.在一些实施例中,系统1400可确定处理器温度(和/或核心温度)正在变高(例如,使用求和1404)。在这种情形中,根据一些实施例,如果处理器(和/或处理器核心)变得太热,则系统1400可降低处理器频率。类似地,在一些实施例中,如果处理器(和/或处理器核心)是凉的(例如,低于某个温度),则处理器频率可被提高。

124.在一些实施例中,可使用人工智能(ai)和/或学习算法来实现系统1400,但是也可使用简单的pid来实现系统1400。系统1400说明了一种基本实现方式,而根据一些实施例,其他实现方式也是可能的。

125.在一些实施例中,如果cdyn(动态电容)在一些应用中较高,并且如果有大量的扼制事件,则处理器可随着时间的推移而学习缓解,例如,通过允许处理器在某个持续时间中耗散更多的功率来暂时增大主板vid,和/或如果在操作持续某段时间之后收益不存在,则通过降低处理器频率(例如,处理器频率f)来暂时增大主板vid。在任何情况下,根据一些实施例,处理器具有进一步优化性能的选项。在一些实施例中,如果扼制事件的数量太高,则闭环操作可依赖于增大vid,而如果扼制事件的数量太低,则闭环操作可依赖于减小vid。在一些实施例中,核心温度和vid也可影响核心频率。在一些实施例中,如果预期处理器的代码(例如,pcode)将要求足够高的负载,以便将有大量的扼制事件,那么该代码可直接修改vid。

126.在一些实施例中,处理器的电力轨(例如,用于小核心)可能更容易被合并,因为最高消费者所要求的vid电压可能会被减小。在一些实施例中,甚至可进一步降低电压,这对于某些应用存在扼制的风险,同时仍然支持所要求的性能裕度。在一些实施例中,电力轨的合并可大大减小平台电力输送(pd)面积和成本。在一些实施例中,可使用本文描述的技术来实现电力轨合并,而没有高功率损失。

127.在一些实施例中,本文所图示和描述的浪涌保护(和/或浪涌保护器)可被实现在系统中的各种位置。例如,在一些实施例中,如本文所图示和描述的浪涌保护和/或浪涌保护器可例如被实现在以下各项中的一项或多项中:处理器、cpu、处理器核心、cpu核心、soc、封装件、芯片组、平台控制器中枢(platform controller hub,pch)、控制器、功率控制器、和/或主板上。在一些实施例中,浪涌保护和/或浪涌保护器可被设计为处理高频率的电压下降(例如,在一些实施例中,在mhz范围内)。在一些实施例中,浪涌保护和/或浪涌保护器可被实现在低功率操作中(例如,使得能够降低功耗,例如处理器功耗,而不是提高性能)。在一些实施例中,处理器的扼制是以快速扼制方式来实现的(例如,快于1μs)。

128.图15图示了根据一些实施例的计算系统1500。图15是根据一些实施例的计算设备1500的示例的框图。在一些实施例中,计算设备1500可以是包括本文描述和/或图示的任何系统的一个或多个元件的计算设备。在一些实施例中,计算设备1500可实现本文描述的任何技术。例如,计算设备1500可实现扼制处理器以保护输入电压、阈值电压保护、浪涌保护,和/或可包括如本文图示和/或描述的浪涌保护器。在一些实施例中,计算设备1500的一个或多个元件可例如与系统100、200、300、500、800、900、1000、1100、1200、1300和/或1500的一些部分相同或者相似,或者可包括这些系统的一些部分。

129.在一些实施例中,在任何一个或多个附图中图示的流程、电路或者系统的任何部分,以及本文描述的任何实施例,都可被包括在计算设备1500中或者由计算设备1500实现。计算设备1500可以是例如计算设备、控制器、控制单元、专用控制器、和/或嵌入式控制器,等等。

130.计算设备1500可包括适合于执行所存储的指令(例如,指令1503)的处理器1502,以及存储可被处理器1502执行的指令1505的存储器设备1504(或者存储装置1504)。处理器1502可以是单核处理器、多核处理器、计算集群、或者任何数量的其他配置。例如,处理器1502可以是1502可以是处理器,例如赛扬、奔腾、酷睿、酷睿i3、酷睿i5或者酷睿i7处理器。在一些实施例中,处理器1502可以是基于x86的处理器。在一些实施例中,处理器1502可以是基于arm的处理器。存储器设备1504可以是存储器设备或者存储设备,并且可包括易失性存储装置、非易失性存储装置、随机存取存储器、只读存储器、闪存、或者任何其他适当的存储器或者存储系统。由处理器1502执行的指令也可用于实现本说明书中描述的和/或附图中图示的任何技术。在一些实施例中,处理器1502可包括与例如本公开中的各种控制器或代理相同或相似的特征或功能。

131.处理器1502还可通过系统互连1506(例如,pci

‑

nubus,等等)链接到适合于将计算设备1500连接到显示设备1510的显示接口1508。显示设备1510可包括显示控制器1530。显示设备1510还可包括作为计算设备1500的内置组件的显示屏幕。显示设备还可包括从外部连接到计算设备1500的计算机监视器、电视或者投影仪,等等。在一些实施例中,计算设备1500不包括显示接口或者显示设备。

132.在一些实施例中,显示接口1508可包括任何适当的图形处理单元、发送器、端口、物理互连,等等。在一些示例中,显示接口1508可实现任何适当的协议,用于将数据传输到显示设备1510。例如,显示接口1508可使用高清晰度多媒体接口(high

‑

definition multimedia interface,hdmi)协议、displayport协议、或者一些其他协议或者通信链路等等来传输数据。

133.此外,网络接口控制器(本文也被称为nic)1512可适合于通过系统互连1506将计算设备1500连接到网络(未描绘)。网络(未描绘)可以是蜂窝网络、无线电网络、广域网(wide area network,wan)、局域网(local area network,lan)、或者互联网,等等。

134.处理器1502可通过系统互连1506连接到输入/输出(i/o)设备接口1514,该接口适合于将计算主机设备1500连接到一个或多个i/o设备1516。i/o设备1516可包括例如键盘或者定点设备,其中定点设备可包括触摸板或者触摸屏,等等。i/o设备1516可以是计算设备1500的内置组件,或者可以是从外部连接到计算设备1500的设备。

135.在一些实施例中,处理器1502还可通过系统互连1506链接到存储设备1518,该存储设备可包括硬盘驱动器、固态驱动器(solid

‑

state drive,ssd)、磁性驱动器、光学驱动器、usb闪存驱动器、驱动器阵列、或者任何其他类型的存储装置,包括其组合。在一些实施例中,存储设备1518可包括可被处理器1502用于实现本文描述的任何技术的任何适当的应用。在一些实施例中,存储装置1518存储可由处理器1502执行的指令1519。在一些实施例中,存储设备1518可包括基本输入/输出系统(basic input/output system,bios)。

136.在一些实施例中,提供了电源设备1522。例如,在一些实施例中,电源设备1522可实现扼制处理器以保护输入电压、阈值电压保护、浪涌保护,和/或可包括如本文所图示和/或描述的浪涌保护器。在一些实施例中,电源1522可包括一个或多个电力供应源,例如一个或多个电力供应单元(power supply unit,psu)。在一些实施例中,电源1522可以是系统1500的一部分,而在一些实施例中,电源1522可以在系统1500的剩余部分的外部。在一些实施例中,电源1522可提供本文描述的任何技术。例如,在一些实施例中,电源1522可提供参考本文的任何附图描述的或者在本文的任何附图中图示的任何技术。

137.图15还图示了系统组件1524。在一些实施例中,系统组件1524可包括显示器、相机、音频、存储、调制解调器或者存储器组件中的任何一个,或者任何额外的系统组件。在一些实施例中,系统组件1524可包括任何系统组件,可根据如本文所述的一些实施例来为其实现电力、电压、功率管理,等等。

138.要理解,图15的框图并不旨在表示计算设备1500在所有实施例中都要包括图15中所示的所有组件。相反,计算设备1500可包括更少的组件或者图15中没有图示的额外组件(例如,额外的存储器组件、嵌入式控制器、额外的模块、额外的网络接口,等等)。此外,电源设备1522的任何功能可以部分或完全被实现在硬件中或者实现在诸如处理器1502之类的处理器中。例如,可以用专用集成电路、在嵌入式控制器中实现的逻辑、或者在处理器1502中实现的逻辑等等来实现该功能。在一些实施例中,可以用逻辑来实现电源设备1522的功能,其中,本文所提及的逻辑可包括任何适当的硬件(例如,处理器,等等),软件(例如,应用,等等),固件,或者硬件、软件或固件的任何适当组合。在一些实施例中,可以用集成电路来实现电源设备1522。

139.图16是一个或多个处理器1602和一个或多个有形非暂态计算机可读介质1600的示例的框图,用于如本文图示和/或描述的对处理器进行扼制以保护输入电压、阈值电压保护、浪涌保护,等等。一个或多个有形非暂态计算机可读介质1600可被(一个或多个)处理器1602通过计算机互连1604来访问。此外,一个或多个有形非暂态计算机可读介质1600可包括指令(或者代码)1606,以指导(一个或多个)处理器1602执行如本文所述的操作。在一些实施例中,处理器1602是一个或多个处理器。在一些实施例中,(一个或多个)处理器1602可执行可由本文描述的其他元件使用包括在介质1600上的指令(代码)1606执行的一些或者全部相同或相似的功能(例如,在图1

‑

图15中的任何一者中图示的或者参考其描述的一些或者全部功能或者技术)。在一些实施例中,一个或多个处理器1602可包括与例如本公开中描述的各种控制器、单元或代理等等相同或相似的特征或功能。在一些实施例中,一个或多个处理器1602、互连1604和/或介质1600可被包括在计算设备1500中。

140.可使用软件组件来实现本说明书中论述的各种组件。这些软件组件可被存储在一个或多个有形非暂态计算机可读介质1600上,如图16中所示。例如,指令1606可适合于指导

(一个或多个)处理器1602执行本说明书中描述的和/或参考附图描述的任何操作中的一个或多个。

141.要理解,任何适当数量的软件组件都可被包括在一个或多个有形非暂态计算机可读介质1600内。此外,取决于具体应用,在图16中示出或者未示出的任何数量的额外软件组件可被包括在一个或多个有形非暂态计算机可读介质1600内。

142.本文描述的(例如,参考图1

‑

图16中的任何一个或多个描述的)各种技术和/或操作可由一种控制单元执行,该控制单元包括一个或多个处理器、监视逻辑、控制逻辑、软件、固件、代理、控制器、逻辑软件代理、系统代理、和/或其他模块。例如,在一些实施例中,本文描述的一些或全部技术和/或操作可由系统代理实现。由于可用于执行这些功能的各种模块及其配置,以及它们在系统中和/或不同系统中的分布,它们没有被全部具体图示在其在图中的可能位置处。

143.本说明书中对所公开主题的“一个实施例”或“实施例”或“一些实施例”的引用意味着结合该实施例描述的特定特征、结构或特性被包括在所公开主题的至少一个实施例中。因此,短语“在一个实施例中”或者“在一些实施例中”可能出现在整个说明书的各个地方,但该短语可能不一定指的是同一个或多个实施例。

144.示例1在一些示例中,一种电压保护装置,包括:电路,用于将处理器的输入电压与阈值电压进行比较,并且如果所述处理器的输入电压下降到低于所述阈值电压,则向所述处理器提供扼制信号。

145.示例2包括如示例1所述的主题。所述电路用于提供电力以将所述处理器的输入电压维持在所述阈值电压或者略高于所述阈值电压。

146.示例3包括如示例1

‑

2中任一项所述的主题。所述电路用于将所述处理器的输入电压的电平设置为低于最大处理器电流和最小处理器电压所要求的电平,而没有违反所述最小处理器电压的风险。

147.示例4包括如示例1

‑

3中任一项所述的主题。所述电路用于在一时间延迟之后解除断言所述扼制信号。

148.示例5包括如示例1

‑

4中任一项所述的主题。所述电路用于响应于所述扼制信号而提供所述处理器的输入电压的替代电压。

149.示例6包括如示例1

‑

5中任一项所述的主题。所述电路用于克服过冲状况。

150.示例7包括如示例1

‑

6中任一项所述的主题。所述电路包括第一开关和第二开关,所述第一开关用于响应于所述扼制信号而提供所述处理器的输入电压的替代电压,所述第二开关用于克服所述过冲状况。

151.示例8包括如示例1

‑

7中任一项所述的主题。所述第一开关和所述第二开关在滞后操作模式中控制所述处理器的输入电压。

152.示例9包括如示例1

‑

8中任一项所述的主题。所述电路包括具有高电阻的开关的阵列,以及用于接通和关断所述开关中的至少一些以相对于所述阈值电压将所述处理器的输入电压维持在某个电压的控制器。

153.示例10包括如示例1

‑

9中任一项所述的主题。所述电路包括线性调节器,以及用于控制所述线性调节器的电阻以维持所述处理器的输入电压的控制器。

154.示例11包括如示例1

‑

10中任一项所述的主题。所述电路包括切换式电压调节器,

所述切换式电压调节器用于维持所述处理器的输入电压。

155.示例12包括如示例1

‑

11中任一项所述的主题。所述电路包括降压转换器,所述降压转换器用于维持所述处理器的输入电压。

156.示例13包括如示例1

‑

12中任一项所述的主题。所述电路用于响应于所述处理器的扼制的数量来调整所述阈值电压。

157.示例14包括如示例1

‑

13中任一项所述的主题。所述电路用于响应于所述处理器的扼制的数量来调整所述处理器的频率。

158.示例15包括如示例1

‑

14中任一项所述的主题。所述电路用于响应于所述处理器的温度来调整所述处理器的频率。

159.示例16包括如示例1

‑

15中任一项所述的主题。所述电路被包括在以下各项中的一项或多项之中或之上:处理器、cpu、处理器核心、cpu核心、soc、封装件、芯片组、平台控制器中枢(pch)、控制器、功率控制器,以及主板。

160.示例17在一些示例中,一种方法可以保护电压。该方法可包括将处理器的输入电压与阈值电压进行比较,并且可包括如果所述处理器的输入电压下降到低于所述阈值电压,则向所述处理器提供扼制信号。

161.示例18包括如示例17所述的主题。所述方法包括:提供电力以将所述处理器的输入电压维持在所述阈值电压或者略高于所述阈值电压。

162.示例19包括如示例17

‑

18中任一项所述的主题。所述方法包括:将所述处理器的输入电压的电平设置为低于最大处理器电流和最小处理器电压所要求的电平,而没有违反所述最小处理器电压的风险。

163.示例20包括如示例17

‑

19中任一项所述的主题。所述方法包括:在一时间延迟之后解除断言所述扼制信号。

164.示例21包括如示例17

‑

20中任一项所述的主题。所述方法包括:响应于所述扼制信号而提供所述处理器的输入电压的替代电压。

165.示例22包括如示例17

‑

21中任一项所述的主题。所述方法包括:克服过冲状况。

166.示例23包括如示例17

‑

22中任一项所述的主题。所述方法包括:响应于所述扼制信号而进行切换以提供所述处理器的输入电压的替代电压,以及进行切换以克服过冲状况。

167.示例24包括如示例17

‑

23中任一项所述的主题。所述方法:包括在滞后操作模式中控制所述处理器的输入电压。

168.示例25包括如示例17

‑

24中任一项所述的主题。所述方法包括:接通和关断开关的阵列中的至少一些开关以相对于所述阈值电压将所述处理器的输入电压维持在某个电压。

169.示例26包括如示例17

‑

25中任一项所述的主题。所述方法包括:进行线性调节并且控制电阻以维持所述处理器的输入电压。

170.示例27包括如示例17

‑

26中任一项所述的主题。所述方法包括:进行切换式电压调节以维持所述处理器的输入电压。

171.示例28包括如示例17

‑

27中任一项所述的主题。所述方法包括:进行降压转换以维持所述处理器的输入电压。

172.示例29包括如示例17

‑

28中任一项所述的主题。所述方法包括:响应于所述处理器的扼制的数量来调整所述阈值电压。

173.示例30包括如示例17

‑

29中任一项所述的主题。所述方法包括:响应于所述处理器的扼制的数量来调整所述处理器的频率。

174.示例31包括如示例17

‑

30中任一项所述的主题。所述方法包括:响应于所述处理器的温度来调整所述处理器的频率。

175.示例32在一些示例中,一种电压保护系统,包括:处理器,以及电路,所述电路用于将所述处理器的输入电压与阈值电压进行比较,并且如果所述处理器的输入电压下降到低于所述阈值电压,则向所述处理器提供扼制信号。

176.示例33包括如示例32所述的主题。所述电路用于提供电力以将所述处理器的输入电压维持在所述阈值电压或者略高于所述阈值电压。

177.示例34包括如示例32

‑

33中任一项所述的主题。所述电路用于将所述处理器的输入电压的电平设置为低于最大处理器电流和最小处理器电压所要求的电平,而没有违反所述最小处理器电压的风险。

178.示例35包括如示例32

‑

34中任一项所述的主题。所述电路用于在一时间延迟之后解除断言所述扼制信号。

179.示例36包括如示例32

‑

35中任一项所述的主题。所述电路用于响应于所述扼制信号而提供所述处理器的输入电压的替代电压。

180.示例37包括如示例32

‑

36中任一项所述的主题。所述电路用于克服过冲状况。

181.示例38包括如示例32

‑

37中任一项所述的主题。所述电路包括第一开关和第二开关,所述第一开关用于响应于所述扼制信号而提供所述处理器的输入电压的替代电压,所述第二开关用于克服所述过冲状况。

182.示例39包括如示例32

‑

38中任一项所述的主题。所述第一开关和所述第二开关在滞后操作模式中控制所述处理器的输入电压。

183.示例40包括如示例32

‑

39中任一项所述的主题。所述电路包括具有高电阻的开关的阵列,以及用于接通和关断所述开关中的至少一些以相对于所述阈值电压将所述处理器的输入电压维持在某个电压的控制器。

184.示例41包括如示例32

‑

40中任一项所述的主题。所述电路包括线性调节器,以及用于控制所述线性调节器的电阻以维持所述处理器的输入电压的控制器。

185.示例42包括如示例32

‑

41中任一项所述的主题。所述电路包括切换式电压调节器,所述切换式电压调节器用于维持所述处理器的输入电压。

186.示例43包括如示例32

‑

42中任一项所述的主题。所述电路包括降压转换器,所述降压转换器用于维持所述处理器的输入电压。

187.示例44包括如示例32

‑

43中任一项所述的主题。所述电路用于响应于所述处理器的扼制的数量来调整所述阈值电压。

188.示例45包括如示例32

‑

44中任一项所述的主题。所述电路用于响应于所述处理器的扼制的数量来调整所述处理器的频率。

189.示例46包括如示例32

‑

45中任一项所述的主题。所述电路用于响应于所述处理器的温度来调整所述处理器的频率。

190.示例47包括如示例32

‑

46中任一项所述的主题。所述电路被包括在以下各项中的一项或多项之中或之上:处理器、cpu、处理器核心、cpu核心、soc、封装件、芯片组、平台控制

器中枢(pch)、控制器、功率控制器,以及主板。

191.示例48在一些示例中,一种电压保护设备,包括:用于将处理器的输入电压与阈值电压进行比较的装置,以及用于如果所述处理器的输入电压下降到低于所述阈值电压则向所述处理器提供扼制信号的装置。

192.示例49包括如示例48所述的主题。所述电压保护设备包括:用于提供电力以将所述处理器的输入电压维持在所述阈值电压或者略高于所述阈值电压的装置。

193.示例50包括如示例48

‑

49中任一项所述的主题。所述电压保护设备包括:用于将所述处理器的输入电压的电平设置为低于最大处理器电流和最小处理器电压所要求的电平而没有违反所述最小处理器电压的风险的装置。

194.示例51包括如示例48

‑

50中任一项所述的主题。所述电压保护设备包括:用于在一时间延迟之后解除断言所述扼制信号的装置。

195.示例52包括如示例48

‑

51中任一项所述的主题。所述电压保护设备包括:用于响应于所述扼制信号而提供所述处理器的输入电压的替代电压的装置。

196.示例53包括如示例48

‑

52中任一项所述的主题。所述电压保护设备包括:用于克服过冲状况的装置。

197.示例54包括如示例48

‑

53中任一项所述的主题。所述电压保护设备包括:用于响应于所述扼制信号而提供所述处理器的输入电压的替代电压的装置,以及用于克服过冲状况的装置。

198.示例55包括如示例48

‑

54中任一项所述的主题。所述电压保护设备包括:用于响应于所述扼制信号而提供所述处理器的输入电压的替代电压的装置,用于克服过冲状况的装置,以及用于在滞后操作模式中控制所述处理器的输入电压的装置。

199.示例56包括如示例48

‑

55中任一项所述的主题。所述电压保护设备包括:具有高电阻的阵列切换装置,以及用于接通和关断所述阵列切换装置中的至少一些以相对于所述阈值电压将所述处理器的输入电压维持在某个电压的装置。

200.示例57包括如示例48

‑

56中任一项所述的主题。所述电压保护设备包括:线性调节器装置,以及用于控制所述线性调节器装置的电阻以维持所述处理器的输入电压的装置。

201.示例58包括如示例48

‑

57中任一项所述的主题。所述电压保护设备包括:用于维持所述处理器的输入电压的切换式电压调节器装置。

202.示例59包括如示例48

‑

58中任一项所述的主题。所述电压保护设备包括:用于维持所述处理器的输入电压的降压转换器装置。

203.示例60包括如示例48

‑

59中任一项所述的主题。所述电压保护设备包括:用于响应于所述处理器的扼制的数量来调整所述阈值电压的装置。

204.示例61包括如示例48

‑

60中任一项所述的主题。所述电压保护设备包括:用于响应于所述处理器的扼制的数量来调整所述处理器的频率的装置。

205.示例62包括如示例48

‑

61中任一项所述的主题。所述电压保护设备包括:用于响应于所述处理器的温度来调整所述处理器的频率的装置。

206.示例63包括如示例48

‑

62中任一项所述的主题。所述电压保护设备位于以下各项中的一项或多项之中或之上:处理器、cpu、处理器核心、cpu核心、soc、封装件、芯片组、平台控制器中枢(pch)、控制器、功率控制器,以及主板。

207.示例64在一些示例中,一种或多种有形非暂态机器可读介质,包括多个指令,所述指令响应于在至少一个处理器上被执行而使得所述至少一个处理器执行以下操作:将处理器(例如,同一处理器,或者另一处理器)的输入电压与阈值电压进行比较,以及如果所述处理器的输入电压(同一处理器的输入电压或者另一处理器的输入电压)下降到低于所述阈值电压,则向所述处理器(向同一处理器或者向另一处理器)提供扼制信号。

208.示例65包括如示例64所述的主题。所述一种或多种有形非暂态机器可读介质包括多个指令,所述指令响应于在至少一个处理器上被执行而使得所述至少一个处理器执行以下操作:提供电力以将所述处理器的输入电压维持在所述阈值电压或者略高于所述阈值电压。

209.示例66包括如示例64

‑

65中任一项所述的主题。所述一种或多种有形非暂态机器可读介质包括多个指令,所述指令响应于在至少一个处理器上被执行而使得所述至少一个处理器执行以下操作:将所述处理器的输入电压的电平设置为低于最大处理器电流和最小处理器电压所要求的电平,而没有违反所述最小处理器电压的风险。

210.示例67包括如示例64

‑

66中任一项所述的主题。所述一种或多种有形非暂态机器可读介质包括多个指令,所述指令响应于在至少一个处理器上被执行而使得所述至少一个处理器执行以下操作:在一时间延迟之后解除断言所述扼制信号。

211.示例68包括如示例64

‑

67中任一项所述的主题。所述一种或多种有形非暂态机器可读介质包括多个指令,所述指令响应于在至少一个处理器上被执行而使得所述至少一个处理器执行以下操作:响应于所述扼制信号而提供所述处理器的输入电压的替代电压。

212.示例69包括如示例64

‑

68中任一项所述的主题。所述一种或多种有形非暂态机器可读介质包括多个指令,所述指令响应于在至少一个处理器上被执行而使得所述至少一个处理器执行以下操作:克服过冲状况。示例70包括如示例64

‑

69中任一项所述的主题。所述一种或多种有形非暂态机器可读介质包括多个指令,所述指令响应于在至少一个处理器上被执行而使得所述至少一个处理器执行以下操作:响应于所述扼制信号而提供所述处理器的输入电压的替代电压,并且克服过冲状况。

213.示例71包括如示例64

‑

70中任一项所述的主题。所述一种或多种有形非暂态机器可读介质包括多个指令,所述指令响应于在至少一个处理器上被执行而使得所述至少一个处理器执行以下操作:在滞后操作模式中控制所述处理器的输入电压。

214.示例72包括如示例64

‑

71中任一项所述的主题。所述一种或多种有形非暂态机器可读介质包括多个指令,所述指令响应于在至少一个处理器上被执行而使得所述至少一个处理器执行以下操作:接通和关断开关的阵列中的至少一些开关以相对于所述阈值电压将所述处理器的输入电压维持在某个电压。

215.示例73包括如示例64

‑

72中任一项所述的主题。所述一种或多种有形非暂态机器可读介质包括多个指令,所述指令响应于在至少一个处理器上被执行而使得所述至少一个处理器执行以下操作:进行线性调节并且控制电阻以维持所述处理器的输入电压。

216.示例74包括如示例64

‑

73中任一项所述的主题。所述一种或多种有形非暂态机器可读介质包括多个指令,所述指令响应于在至少一个处理器上被执行而使得所述至少一个处理器执行以下操作:进行切换电压调节以维持所述处理器的输入电压。

217.示例75包括如示例64

‑

74中任一项所述的主题。所述一种或多种有形非暂态机器

可读介质包括多个指令,所述指令响应于在至少一个处理器上被执行而使得所述至少一个处理器执行以下操作:进行降压转换以维持所述处理器的输入电压。

218.示例76包括如示例64

‑

75中任一项所述的主题。所述一种或多种有形非暂态机器可读介质包括多个指令,所述指令响应于在至少一个处理器上被执行而使得所述至少一个处理器执行以下操作:响应于所述处理器的扼制的数量来调整所述阈值电压。

219.示例77包括如示例64

‑

76中任一项所述的主题。所述一种或多种有形非暂态机器可读介质包括多个指令,所述指令响应于在至少一个处理器上被执行而使得所述至少一个处理器执行以下操作:响应于所述处理器的扼制的数量来调整所述处理器的频率。

220.示例78包括如示例64

‑

77中任一项所述的主题。所述一种或多种有形非暂态机器可读介质包括多个指令,所述指令响应于在至少一个处理器上被执行而使得所述至少一个处理器执行以下操作:响应于所述处理器的温度来调整所述处理器的频率。

221.示例79在一些示例中,一种设备,包括用于执行如任何其他示例中所述的方法的装置。

222.示例80在一些示例中,一种系统,包括用于执行如任何其他示例中所述的方法的装置。

223.示例81在一些示例中,一种机器可读存储装置,包括机器可读指令,所述指令在被执行时,实现如任何其他示例中所述的方法或者实现如任何其他示例中所述的装置。

224.示例82在一些示例中,一种或多种机器可读介质,包括代码,所述代码在被执行时,使得机器执行如任何其他示例所述的方法。

225.虽然参考附图中的电路图、流程图、框图等等描述了所公开主题的示例实施例和示例,但本领域的普通技术人员将容易理解,可以替代地使用实现所公开主题的许多其他方式。例如,可以改变附图中的元素的布置或者附图中的块的执行顺序,或者可以改变、消除或组合电路图中的一些电路元素,以及描述的框图/流程图中的块。可以改变、消除或组合图示或描述的任何元素。

226.在前面的描述中,描述了所公开主题的各个方面。为了说明,阐述了具体数字、系统和配置以便提供对该主题的透彻理解。然而,受益于本公开的本领域技术人员很清楚,没有这些具体细节也可实现该主题。在其他情况下,公知的特征、组件或模块被省略、简化、组合或分割,以免模糊所公开主题。

227.所公开主题的各种实施例可以用硬件、固件、软件或者其组合来实现,并且可通过参考或结合程序代码来描述,程序代码例如是指令、函数、过程、数据结构、逻辑、应用程序、设计表示或格式,用于设计的仿真、模拟和制造,该程序代码在被机器访问时使得机器执行任务、定义抽象数据类型或低级别硬件上下文,或者产生结果。

228.程序代码可使用硬件描述语言或另一种功能描述语言来表示硬件,这种语言本质上提供了关于设计的硬件被预期如何表现的模型。程序代码可以是汇编或机器语言或硬件定义语言,或者可被编译或解释的数据。此外,以一种或另一种形式将软件称为采取动作或产生结果,是本领域中常见的。这种表述只是陈述处理系统执行使得处理器执行动作或产生结果的程序代码的一种简略方式。

229.程序代码可被存储在例如一个或多个易失性或非易失性存储器设备中,例如存储设备或者关联的机器可读或机器可访问介质,包括固态存储器、硬盘驱动器、软盘、光学存

储装置、磁带、闪存、记忆棒、数字视频盘、数字多功能盘(digital versatile disc,dvd)等等,以及更特殊的介质,例如机器可访问生物状态保留存储装置。机器可读介质可包括用于以机器可读的形式存储、发送或接收信息的任何有形机制,例如天线、光纤、通信接口,等等。程序代码可被以分组、串行数据、并行数据等等的形式来传输,并且可被以压缩的和/或加密的格式来使用。

230.程序代码可被实现于在可编程机器上执行的程序中,可编程机器例如是移动或固定计算机、个人数字助理、机顶盒、蜂窝电话和寻呼机以及其他电子设备,其中每一者包括处理器、处理器可读的易失性或者非易失性存储器、至少一个输入设备或者一个或多个输出设备。程序代码可被应用到使用输入设备输入的数据以执行描述的实施例和生成输出信息。输出信息可被应用到一个或多个输出设备。本领域普通技术人员可理解,可利用各种计算机系统配置来实现所公开主题的实施例,包括多处理器或多核处理器系统、微型计算机、大型计算机、以及可被嵌入到几乎任何设备中的普及的或微型计算机或处理器。所公开主题的实施例也可被实现在分布式计算环境中,其中任务可被通过通信网络链接的远程处理设备执行。

231.虽然操作可被描述为顺序过程,但操作中的一些实际上可被并行执行、同时执行、或者在分布式环境中执行,以及利用存储在本地或者远程供单处理器或多处理器机器访问的程序代码执行。此外,在一些实施例中,操作的顺序可被重排列,而不脱离所公开主题的精神。程序代码可被嵌入式控制器使用或者结合嵌入式控制器使用。

232.虽然已参考说明性实施例描述了所公开主题,但该描述不旨在被解释为限制性含义。对所公开主题所属领域的技术人员显而易见的说明性实施例以及本主题的其他实施例的各种修改被视为落在所公开主题的范围内。例如,在每个图示的实施例和每个描述的实施例中,要理解,本文的附图和描述并不旨在表明所图示或描述的设备包括特定图中所示出的或者参考特定图所描述的所有组件。此外,可以用逻辑来实现每个元素,其中,本文所提及的逻辑例如可包括任何适当的硬件(例如,处理器,等等),软件(例如,应用,等等),固件,或者硬件、软件和固件的任何适当组合。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1