芯片片上系统异构多处理器间的通信装置及方法与流程

[0001]

本公开涉及通信技术领域,尤其涉及芯片片上系统异构多处理器间的通信装置及方法。

背景技术:

[0002]

在汽车网联化、智能化的发展趋势下,芯片系统需要兼顾运算能力和功能安全性,芯片设计更为复杂且需应对多种场景要求而进行设计,主要体现在:芯片非对称多处理器个数的增加,且处理器互相功能隔离、保留必要的相互通信、保证各自的功能独立运行。但是作为一个系统的整体设计,处理器间的通信,比如对某些特定硬件的状态查询,车辆状态信息以及车联网数据传递,又必不可少,既要保持处理器各自功能的独立性和安全性,又要体现片上系统的整体性和系统性。

[0003]

处理器间通信,又叫核间通信,是多核片上系统中常见的通信形式,分为同构多核和异构多核。为满足汽车电子架构对安全性要求,片上系统设计时除了考虑高性能计算单元,也考虑了独立的安全单元,甚至一些独立任务运算单元,通常将这些运算单元称为域,这些异质的处理单元组成了异构多核系统。另外随着虚拟化技术的不断发展和汽车行业的融合,在高性能计算域内又分化出不同的虚拟机域,这些域为了满足不同的功能和安全性需求,运行了不同的操作系统和算法。为此,核间通信需要同时支持这些复杂的消息传输场景。

[0004]

应对大数据和算力不断增长的需求,汽车产业电子架构逐渐从传统的分布式ecu(electronic control unit,电子控制单元)朝集中化的域控制器、网关和中央控制器等方向发展,一个片上系统会集成更多的微控制器,外围设备和高性能处理器,组成一个多处理器的复杂集合,一方面能够满足不断增长的算力需求,同时尽可能复用硬件投资成本,另一方面,又要保证汽车领域对安全性的监管需求。这种具有多处理器的片上系统会变得更加主流,多处理器间的信息交换必然要求高速率、高可靠性和低延迟,才能发挥片上系统整体的强大功能。

[0005]

传统的ipi(inter-processor interrupt,处理器间中断)可以满足通知的需求,缺点是携带信息太少。当ipi结合使用ddr内存或片上缓冲区传输数据时,可以满足传输的带宽和时延的需求,缺点是仅能寻址到处理器。如果两端处理器是单任务收发时,这种方式是可以满足需求的。但是,当处理器上运行多任务时,多路传输寻址就无法用上面的方法实现。更加复杂的情形是,当引入虚拟化技术后,虚拟主机和其上的多任务也需要进行跨域的传输,现有技术就无法满足需求。

技术实现要素:

[0006]

本公开提供了一种芯片片上系统异构多处理器间的通信装置及方法,其技术目的是在多个处理器之间,通过灵活的发送和接收控制器通道组合,以较少的开销支持高达255多任务分时复用物理通道,同时能够支持多种上层传输协议,便于在此基础上虚拟出各种

网卡设备。本公开可以应用于虚拟化技术,通过给处理器绑定独立的发送和接收控制器,分配给多个虚拟机,可以实现通信装置虚拟化,和物理处理器之间进行数据传输。

[0007]

本公开的上述技术目的是通过以下技术方案得以实现的:一种芯片片上系统异构多处理器间的通信装置,包括:至少一个第一处理器,每个所述第一处理器包括至少一个第一发送控制器和至少一个第一接收控制器;至少一个第二处理器,每个所述第二处理器包括至少一个第二发送控制器和至少一个第二接收控制器;第一缓存区,用于所述第一发送控制器写入第一传输协议,所述第一传输协议包括第一处理器编号和对应的第二处理器编号、第一发送控制器编号和对应的至少一个第二接收控制器编号;第一查询单元,通过所述第二处理器编号和所述第二接收控制器编号查询到第二处理器的第二接收控制器;第一读取单元,用于所述第二接收控制器从所述第一缓存区中读取所述第一传输协议。

[0008]

进一步地,包括:第二缓存区,用于所述第二发送控制器写入第二传输协议,所述第二传输协议包括所述第二处理器编号和对应的第一处理器编号、第二发送控制器编号和对应的第一接收控制器编号;第二查询单元,通过所述第一处理器编号和所述第一接收控制器编号查询第一处理器的第一接收控制器;第二读取单元,用于所述第一接收控制器从所述第二缓存区中读取所述第二传输协议。

[0009]

进一步地,所述第一传输协议还包括第二应用程序编号和对应的第一应用程序数据,所述第二应用程序编号和至少一个所述第二接收控制器相对应;所述第二传输协议还包括第一应用程序编号和对应的第二应用程序数据,所述第一应用程序编号和至少一个所述第一接收控制器相对应;所述第一查询单元还用于:通过所述第二处理器编号、所述第二接收控制器编号和所述第二应用程序编号查询所述第二处理器的第二接收控制器的第二应用程序;所述第一读取单元还用于:所述第二应用程序从所述第一缓冲区中读取所述第一应用程序数据;所述第二查询单元还用于:通过所述第一处理器编号、所述第一接收控制器编号和所述第一应用程序编号查询所述第一处理器的第一接收控制器的第一应用程序;所述第二读取单元还用于:所述第一应用程序从所述第二缓冲区中读取所述第二应用程序数据。

[0010]

进一步地,每个所述第一发送控制器和至少一个第二接收控制器相对应,每个所述第二发送控制器和至少一个第一接收控制器相对应,所述第一发送控制器和对应的所述第二接收控制器共享一个缓存区,所述第二发送控制器和对应的所述第一接收控制器共享一个缓存区。

[0011]

进一步地,所述第一传输协议和所述第二传输协议还包括:标志控制位、校验位和载荷长度。

[0012]

一种芯片片上系统异构多处理器间的通信方法,包括:第一处理器的第一发送控制器将第一传输协议写入第一缓存区,所述第一传输协议包括第一处理器编号和对应的第二处理器编号、第一发送控制器编号和对应的至少一个第二接收控制器编号;通过所述第二处理器编号和所述第二接收控制器编号查询到第二处理器的第二接收控制器;所述第二接收控制器从所述第一缓存区中读取所述第一传输协议。

[0013]

进一步地,包括:所述第二处理器的第二发送控制器将第二传输协议写入第二缓存区,所述第二传输协议包括所述第二处理器编号和对应的第一处理器编号、第二发送控制器编号和对应的第一接收控制器编号;通过所述第一处理器编号和所述第一接收控制器编号查询所述第一处理器的第一接收控制器;所述第一接收控制器从所述第二缓存区中读取所述第二传输协议。

[0014]

进一步地,所述第一传输协议还包括第二应用程序编号和对应的第一应用程序数据,所述第二应用程序编号和至少一个所述第二接收控制器相对应;所述第二传输协议还包括第一应用程序编号和对应的第二应用程序数据,所述第一应用程序编号和至少一个所述第一接收控制器相对应;通过所述第二处理器编号、所述第二接收控制器编号和所述第二应用程序编号查询所述第二处理器的第二接收控制器的第二应用程序,所述第二应用程序从所述第一缓冲区中读取所述第一应用程序数据;通过所述第一处理器编号、所述第一接收控制器编号和所述第一应用程序编号查询所述第一处理器的第一接收控制器的第一应用程序,所述第一应用程序从所述第二缓冲区中读取所述第二应用程序数据。

[0015]

本公开的有益效果在于:本公开所述的芯片片上系统异构多处理器间的通信装置及方法,通过处理器的发送控制器将传输协议写入与接收控制器共用的缓存区,该传输协议包括与发送控制器对应的另一处理器的接收控制器,通过传输协议查询到接收控制器后,接收控制器再从缓存区中读取传输协议中的数据,实现异构处理器间的通信。通过三级编码的混合使用实现多路复用,可以在最多8个处理器之间,4个发送和接收组合通道上,255个任务之间实现数据传输。同时能够支持扩展多种传输协议,灵活性高。

附图说明

[0016]

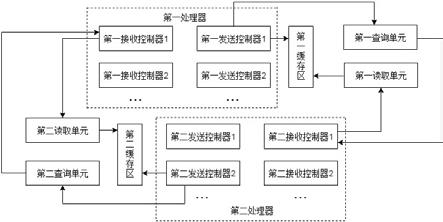

图1为本公开所述的芯片片上系统异构多处理器间的通信装置示意图;图2为本公开所述的芯片片上系统异构多处理器间的通信方法流程图;图3为本公开实施例一的流程图;图4为本公开实施例二的流程图;图5为本公开实施例三的流程图。

具体实施方式

[0017]

下面将结合附图对本公开技术方案进行详细说明。在本申请的描述中,需要理解地是,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括至少一个该特征,或仅用来区分不同的组成部分。

[0018]

本发明用于芯片片上系统,共享内存可以使用芯片内部的sram,也可以是外部的ddr dram。

[0019]

图1为本公开所述的芯片片上系统异构多处理器间的通信装置示意图,如图1所示,该通信装置包括至少一个第一处理器和至少一个第二处理器,第一处理器包括至少一个第一发送控制器和至少一个第一接收控制器,第二处理器包括至少一个第二发送控制器和至少一个第二接收控制器。此外,该通信装置还包括第一缓存区、第二缓存区、第一查询单元、第二查询单元、第一读取单元和第二读取单元。

[0020]

第一处理器作为发送方、第二处理器作为接收方时,第一发送控制器在第一缓存区内写入第一传输协议,该第一传输协议包括第一处理器编号和对应的第二处理器编号、第一发送控制器编号和对应的至少一个第二接收控制器编号。第一查询单元通过第二处理器编号和第二接收控制器编号查询到第二处理器的第二接收控制器,第二接收控制器通过第一读取单元从第一缓存区中读取第一传输协议,获取第一传输协议中的数据内容。

[0021]

同样,第二处理器作为发送方,第一处理器作为接收方时,第二发送控制器在第二缓存区内写入第二传输协议,该第二传输协议包括第二处理器编号和对应的第一处理器编号、第二发送控制器编号和对应的至少一个第一接收控制器编号。第二查询单元通过第一处理器编号和第一接收控制器编号查询到第一处理器的第一接收控制器,第一接收控制器通过第二读取单元从第二缓存区中读取第二传输协议,获取第二传输协议中的数据内容。

[0022]

作为具体实施例地,处理器a和处理b均有多个数据发送控制器和接收控制器,假设分组控制器共有4组,编号分别为0、1、2、3。处理器a的发送控制器和处理器b的接收控制器(或处理器a的接收控制器和处理器b的发送控制器)通过固定编码方式进行配对,在发送控制器、接收控制器的初始化时完成配置,例如以以下组合方式进行配对:发送控制器[0]

ꢀ-

> 接收控制器[0];发送控制器[1]

ꢀ-

> 接收控制器[1];发送控制器[2]

ꢀ-

> 接收控制器[2];发送控制器[3]

ꢀ-

> 接收控制器[3];也可以是,发送控制器[0]

ꢀ-

> 接收控制器[3];发送控制器[1]

ꢀ-

> 接收控制器[1];发送控制器[3]

ꢀ-

> 接收控制器[0];发送控制器[2]

ꢀ-

> 接收控制器[2]。

[0023]

每个发送控制器和至少一个接收控制器相对应,发送控制器和对应的接收控制器共享一个缓存区。即可以实施一对多的发送,即一个发送控制器向多个接收控制器进行发送,根据数据业务内容调整,每一个发送控制器和相应接收控制器的配对共享一个缓存区域。

[0024]

处理器a作为发送端进行发送业务时,发送流程包括:(1)根据业务逻辑和接收端的处理器b,确定选择一个发送控制器和接收控制器进行配对,例如处理器a选择发送控制器[1];(2)设置接收端处理器的编号,这里为b;(3)设置接收控制器编号,假设是接收控制器[1];(4)填写待发送数据到缓存区;(5)处理器a发送触发处理器间中断,设置发送标志位;(6)处理器a等待发送标志位清零;(7)完成发送。

[0025]

处理器b作为接收端接收业务时,接收流程包括:(1)接收处理器间中断;(2)确定发送端处理器编号,是来自处理器a;(3)确定接收控制器编号,来自接收控制器[1];(4)读取接收控制器[1]对应的共享内存区域(缓存区);(5)对发送标志位清零。

[0026]

以上是两个处理器的情况,若是两个以上的处理器,每增加一个处理器,每个处理器的发送控制器和接收控制器都要增加至少1组,用于同步接收来自不同处理器的数据。具体实践时,收发控制器的数量主要考虑实现成本,当处理器上任务较多时,可以适当增加收发控制器数量。

[0027]

另外,第一传输协议还包括第二应用程序编号和对应的第一应用程序数据,第二应用程序编号和至少一个第二接收控制器相对应(即第一应用程序数据可以发送给第二处理器的多个第二应用程序)。第二传输协议还包括第一应用程序编号和对应的第二应用程序数据,第一应用程序编号和至少一个第一接收控制器相对应(即第二应用程序数据可以发送给第一处理器的多个第一应用程序)。

[0028]

第一查询单元通过第二处理器编号、第二接收控制器编号和第二应用程序编号查询第二处理器的第二接收控制器的第二应用程序,第二应用程序通过第一读取单元从第一缓冲区中读取第一应用程序数据。

[0029]

第二查询单元通过第一处理器编号、第一接收控制器编号和第一应用程序编号查询第一处理器的第一接收控制器的第一应用程序,第一应用程序通过第二读取单元从第二缓冲区中读取第二应用程序数据。

[0030]

作为具体实施例地,例如,处理器a上运行的某一个应用程序1想发送给处理器b上的另一个应用程序2,主要通信过程如下:(1)应用程序1准备传输的数据;(2)填充传输协议的头部信息;(3)将数据写入处理器a和处理器b共同可见的缓存区;(4)发送核间中断,通知处理器b;(5)处理器b处理中断,读取数据,根据接收地址(即应用程序编号)选择分发应用程序;(6)处理器b再通过中断回复确认信息给处理器a;(7)处理器a收到确认回应,并通知应用程序2发送完成。

[0031]

另外,传输协议的头部信息主要包括:(1)处理器编号,包含处理器a和处理器b的编号,该编号使用4位比特位表示,最多可支持16个处理器同时进行,特别用于单个soc片上系统内部多个异构处理器的情况;(2)填入的数据内容可以支持其他上层协议报文,既能够支持主流的比如以太网帧,udp(user datagram protocol,用户数据报协议)报文,can(controller area network,控制器局域网络)报文,rpmsg(remote processor messaging,远程处理器消息传递)报文,又支持自定义短数据通知报文,方便在多个处理器之间作各种方式信息中继;特别针对,片上系统多异构处理器处理能力有不同,外设资源可客制化的情况下,数据在系统内、外部的中继,过滤和转发;(3)多路复用地址,支持在2个处理器上同时运行的多个应用程序间并发地接收或发送

数据,充分利用硬件的高速传输性能,每个处理器上最多支持255个应用程序,适合片上系统内多个操作系统间多任务并发环境;(4)标志控制位,可以根据数据类型,设置qos(quality of service,服务质量),比如是否错误重传、是否需要数据校验等,保证数据完整性,和平衡传输延迟,实现:实时性优先,追求低延迟,无缓冲队列,发送不等待完成,适用于短消息通知,模拟中断情况;高可靠性优先,保证数据完整准确,有握手回包,丢失会重发;高吞吐率优先,追求低延迟,有缓冲队列,流量控制,适用于载荷较多情况;(5)校验位,预留16位,crc16(cyclic redundancy check,循环冗余校验)或者校验和等,由标志控制位可选配;(6)载荷长度,单次传输的最大数据量mtu(maximum transmission unit,最大传输单元)是4096字节。

[0032]

图2为本公开所述的芯片片上系统异构多处理器间的通信方法流程图,如图2所示,100:第一处理器的第一发送控制器将第一传输协议写入第一缓存区,所述第一传输协议包括第一处理器编号和对应的第二处理器编号、第一发送控制器编号和对应的至少一个第二接收控制器编号。101:通过所述第二处理器编号和所述第二接收控制器编号查询到第二处理器的第二接收控制器。102:所述第二接收控制器从所述第一缓存区中读取所述第一传输协议。

[0033]

图3为本公开实施例一流程图,200:所述第二处理器的第二发送控制器将第二传输协议写入第二缓存区,所述第二传输协议包括所述第二处理器编号和对应的第一处理器编号、第二发送控制器编号和对应的第一接收控制器编号。201:通过所述第一处理器编号和所述第一接收控制器编号查询所述第一处理器的第一接收控制器。202:所述第一接收控制器从所述第二缓存区中读取所述第二传输协议。

[0034]

若需要将第一处理器上运行的第一应用程序发送给第二处理器上的第二应用程序,那么第一传输协议还包括第二应用程序编号和对应的第一应用程序数据,第二应用程序编号和至少一个第二接收控制器相对应。然后300:通过第二处理器编号、第二接收控制器编号和第二应用程序编号查询第二处理器的第二接收控制器的第二应用程序;301:该第二应用程序从第一缓冲区中读取第一应用程序数据,如图4所示。

[0035]

同理,若需要将第二处理器上运行的第二应用程序发送给第一处理器上的第一应用程序,那么第二传输协议还包括第一应用程序编号和对应的第二应用程序数据,第一应用程序编号和至少一个第一接收控制器相对应。然后400:通过第一处理器编号、第一接收控制器编号和第一应用程序编号查询第一处理器的第一接收控制器的第一应用程序;401:该第一应用程序从第二缓冲区中读取第二应用程序数据,如图5所示。

[0036]

以上为本公开示范性实施例,本公开的保护范围由权利要求书及其等效物限定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1