RISC-V指令集移位指令实现电路的制作方法

risc

‑

v指令集移位指令实现电路

技术领域

1.本发明涉及集成电路技术领域,具体涉及一种risc

‑

v指令集移位指令实现电路。

背景技术:

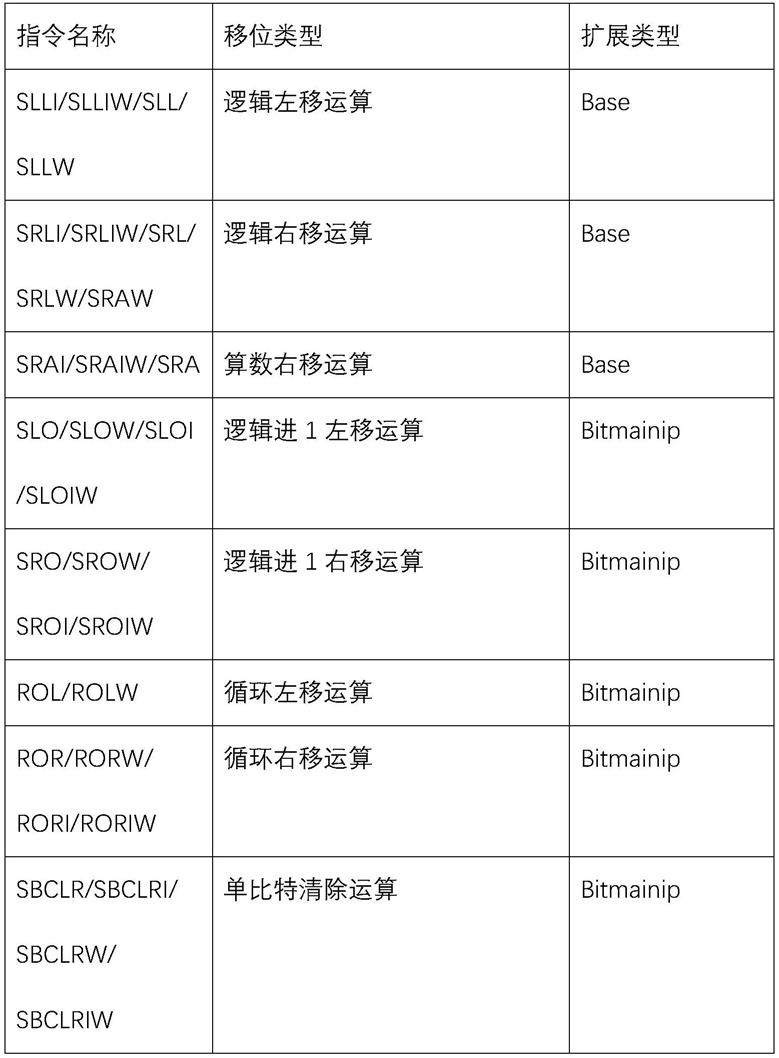

2.处理器自诞生至今已有50多年,在发展中为了满足处理器多样化的处理场景,追求更高的处理器性能,各个处理器架构不断扩充自身指令集,例如ricsv指令集除了base指令集中基本移位指令,在bitmainip扩展指令中增加了循环移位,进1移位,漏斗移位,单比特操作等移位类型指令。经过编译后,可以极大的减小程序执行的指令数量,因此处理器可以进一步获得更高的运算性能。

3.risc

‑

v64指令集包含众多移位指令,其中rv baseinteger和rv btmainip指令集均涉及移位指令,当前设计产品中并没有合适逻辑电路单元支持上述所有的移位指令。

4.现有产品中对于高性能设计cpu,现有的桶形移位器模块容易造成时序紧张,核心频率受到限制,且无法支持所有riscv架构的所有移位指令。

技术实现要素:

5.针对现有技术的不足,本发明公开了一种risc

‑

v指令集移位指令实现电路,用于解决现有产品中对于高性能设计cpu,现有的桶形移位器模块容易造成时序紧张,核心频率受到限制,且无法支持所有riscv架构的所有移位指令的问题。

6.本发明通过以下技术方案予以实现:

7.本发明公开了一种risc

‑

v指令集移位指令实现电路,所述电路集成有移位模块,所述移位模块由左向移位器、右向移位器和减法器组成,当指令从指令缓存区发射出来后,进入译码模块完成指令译码,此时译码信息以及操作数进入移位模块,利用左向移位器完成左移指令,右向移位器完成右移指令,并借助减法器负责为左向移位器和右向移位器提供移位距离操作数运算完成后,输出结果提交指令,本条指令执行完成。

8.更进一步的,确定操作数后,移位距离操作数包括shift_amt和xlen

‑

shift_amt,当指令为单一移位操作时,移位器选择初始移位距离数据,当指令为循环移位或漏斗移位时,移位运算可以分解为左移和右移操作,并对左向移位器和右向移位器结果进行逻辑或操作。

9.更进一步的,所述左向移位器采用逻辑展开选通电路对被移位数据a进行整形,生成64个数据向量tb[i]组成的数据阵列tb,其中每个向量tb[i]的数据长度为i,生成过程如下:

[0010]

s11设定变量i,初始值为0;

[0011]

s12取被移位数据a[i:0]比特赋值为tb[i];

[0012]

s13对数据tb[i]进行取反操作;

[0013]

s14变量i加1,如果变量i小于64,则重新执行步骤2,反之则执行s15;

[0014]

s15输出数据阵列tb[i]。

[0015]

更进一步的,所述左向移位器使用逻辑展开的方法对被移位数据shift_decode_amt进行切割,生成一个由64个向量sh[i]组成的数据阵列sh,其中向量sh[i]的数据宽度为i,具体步骤如下:

[0016]

s21设定变量j,j的初始值位0;

[0017]

s22取被以为数据[j:0]比特为sh[j];

[0018]

s23变量j加1,如果变量j小于64,则重新执行步骤2,反之执行步骤5;

[0019]

s24输出结果sh[j]

[0020]

s25生成一个由64个向量sh[j]组成的数据阵列sh。

[0021]

更进一步的,所述左向移位器分别对tb数据矩阵与sh数据矩阵的第n个行向量进行按位与操作,其中n为tb[i]和sh[j]数据阵列的行索引,此时索引i与索引j相同,对按位与的结果逐位逻辑或处理,得到1bit的结果tmp[n],由于数据矩阵tb和sh均有64个行向量,最终得到向量tmp的宽度也为64,过程如下:

[0022]

s31设定变量n,n的初始值为0;

[0023]

s32取tb[n]和sh[n],并对tb[n]和sh[n]进行按位与操作,得到向量tb_sh;

[0024]

s33对向量tb_sh进行逐位或处理,得到单比特结果tmp[n];

[0025]

s34变量n加1,如果变量n小于64,则重新执行步骤2,反之执行s35;

[0026]

s35输出结果tmp[n];

[0027]

其中将sh数据阵列中第n个行向量进行逐位逻辑或运算,得到sin_select[n]向量,根据sin_select[n]比特值选择对应tmp[n]值或sin值作为最终移位结果out[n],输出数据out同样为64比特宽度。

[0028]

更进一步的,所述右向移位器完成右移指令与所述左向移位器完成左移指令的方法相同,同样使用逻辑展开选通电路实现移位功能,且与左向移位器的移位处理单元相同,只增加对输入输出数据进行反转操作,当逻辑左移左进1移位,单比特操作指令结果由左向移位器运算并输出结果,逻辑右移位右移进1移位指令结果由右向移位器运算并输出结果,最终移位模块的结果根据移位控制信号选择对应移位器数据结果。

[0029]

更进一步的,当移位指令为bfp指令时,使用操作数b的一段数据替换操作数a的某个比特区域,从指令码中提取出off字段和len字段后,同时对掩码和替换数据进行左向移位,最后对掩码和替换数据的移位结果进行逻辑与或操作,具体过程如下:

[0030]

s41根据sel字段,选择off和len数据;

[0031]

s42根据len数据计算掩码

[0032]

s43使用左向移位器对掩码移位,移位距离为off数据。使用右向移位器对数据inb_a移位,移位距离位off数据,不过这里的右向移位器需要当作左向移位器使用,对移位数据inb_a和输出结果rishift_outb分别进行反转操作;

[0033]

s44对结果进行逻辑与或操作;

[0034]

其中,bfp指令使用对对掩码mask数据和数据b[31:0]进行逻辑左移,将右向移位器当作左向移位器使用,在移位数据b在进入右向移位数据前和结果输出后,均进行反转操作,左向移位器和右向移位器移位距离数据相同,均为off数据,左向移位器数据输入为mask数据,右向移位器数据输入为inb_a[31:0],对结果进行或与操作,得到bfp指令运算结果。

[0035]

更进一步的,当移位指令为循环移位和漏斗移位时,同时调用左向移位器和右向移位器的输出结果,并将两个移位器的结果进行或处理;

[0036]

当移位类型为循环左移时,被移位数据在左向模块移向左移位n位,且移入值为零,得到结果l_res,被移数据在右向移位模块中向右移位64

‑

n位,且移入值为零,得到移位结果r_res,将l_res与r_res进行按位或处理,即得到循环左移移位结果,循环右移反之亦然,左向移位模块向左移位64

‑

n位,右向移位模块向右移位n位,对两个移位器移位结果按位或运算,得到循环右移移位结果。

[0037]

更进一步的,当移位类型为漏斗移位时,其操作与循环移位操作相同,循环移位数据左向移位和右向移位的被移位数据为同一个数据,而漏斗移位操作中,左向移位数据和右向移位数据为不同数据,数据选择器负责进行数据选择;

[0038]

当移位类型为单比特操作时,被移位数为64’b1,使用左向移位器生成mask掩码,待运算数据与掩码进行对应的逻辑运算完成单比特操作,单比特操作包含了逻辑或操作,其循环移位和漏斗移位复用单比特操作中的运算逻辑。

[0039]

更进一步的,包括处理器以及存储有执行指令的存储器,在risc

‑

v指令集移位指令实现电路工作时,所述处理器执行所述存储器存储的所述执行指令。

[0040]

本发明的有益效果为:

[0041]

本发明支持riscv架构指令集包含的所有移位操作指令,且时序容易收敛,可以得到更高的主频。尤其适合追求高性能cpu的架构设计。

附图说明

[0042]

为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

[0043]

图1是本发明实施例的指令执行完成原理框图;

[0044]

图2是本发明实施例的移位模块原理框图;

[0045]

图3是本发明实施例输出数据out同样为64比特宽度的具体流程图;

[0046]

图4是本发明实施例输出移位结果值out原理图;

[0047]

图5是本发明实施例反转操作原理框图;

[0048]

图6是本发明实施例bfp指令格式图;

[0049]

图7是本发明实施例当移位指令为循环移位和漏斗移位时的原理图;

[0050]

图8是本发明实施例运算结果输出选择原理图。

具体实施方式

[0051]

为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

[0052]

实施例1

[0053]

本实施例公开一种ricsv指令集除了base指令集中基本移位指令,在bitmainip扩展指令中增加了循环移位,进1移位,漏斗移位,单比特操作等移位类型指令。经过编译后,可以极大的减小程序执行的指令数量,因此处理器可以进一步获得更高的运算性能。

[0054]

riscv架构支持移位指令如下:

[0055]

[0056][0057]

移位指令的操作需要译码单元提供指令执行所必须的控制信号,如图1所示,指令从指令缓存区去发射出来,进入译码模块完成指令译码,随后译码信息以及操作数进入移位模块,运算完成后,输出结果提交指令,本条指令执行完成。

[0058]

本实施例中移位模块所需要的移位控制信号见下表,

[0059]

控制信号高电平有效

[0060]

[0061][0062]

如果使用传统的桶形移位器,为满足risc64指令集移位需求,则移位宽度为128bit,这就需要通过7级选择器进行级联实现,容易造成时序紧张。

[0063]

本实施例区别于传统的桶形移位器,移位器采用逻辑循环展开方式实现,整个移位模块实现主要由一个左向移位器,一个右向移位器和一个6bit减法器组成,如图2所示。其中左向移位器负责完成左移指令,右向移位器负责完成右移指令,左向移位器和右向移位器分别完成该指令所需的移位操作,减法器负责为左向移位器和右向移位器提供移位距离操作数。

[0064]

在操作数确定的情况下,移位距离操作数仅有两种可能,即shift_amt和xlen

‑

shift_amt(方法以rv64指令集为例,所以xlen为64)。不同的移位操作,移位器的移位距离操作数选择会不同,左向移位器和右向移位器对应输入的移位距离操作数关系见下述代码:

[0065]

assignshift_amt_sub=(is_funnel_32|is_rolw|is_rwshift|is_bfp)?xlen/2:xlen)

–

shift_amt;

[0066]

assign lshift_sel_amt=is_setbit|~is_rshift;

[0067]

assign rshift_sel_amt=is_rshift;

[0068]

assign lshift_amt=(lshift_sel_amt|is_bfp)?shift_amt:shift_amt_sub;

[0069]

assign rshift_amt=(rshift_sel_amt|is_bfp)?shift_amt:shift_amt_sub;

[0070]

当指令为单一移位操作时,移位器选择初始移位距离数据,即shift_amt,当指令为循环移位或漏斗移位时,移位运算可以分解为左移和右移操作,并对左向移位器和右向移位器结果进行逻辑或操作,注意的是,左向移位器和右向移位器的移位距离数据选择不同,规则入下表:

[0071][0072]

实施例2

[0073]

本实施例公开一种左向移位单元实现方法,其为逻辑展开选通电路,逻辑展开是对被移位数据a进行整形,生成64个数据向量tb[i]组成的数据阵列tb,其中每个向量tb[i]的数据长度为i,生成过程如下:

[0074]

设定变量i,初始值为0;

[0075]

取被移位数据a[i:0]比特赋值为tb[i];

[0076]

对数据tb[i]进行取反操作;

[0077]

变量i加1,如果变量i小于64,则重新执行步骤2,反之则执行步骤5;

[0078]

输出数据阵列tb[i]

[0079]

代码如下:

[0080][0081][0082]

然后将shift_amt数据译码变为hotcode编码,即若lshift_amt=i,则lshift_decode_amt[i+1]=1,其余bit位均为0,随后使用lshift_decode_amt信号作为逻辑展开电路选通信号。对shift_amt按照以下代码进行hotcode编码。

[0083]

[0084]

使用逻辑展开的方法对移位数据shift_decode_amt进行切割,生成一个由64个向量sh[i]组成的数据阵列sh,其中向量sh[i]的数据宽度为i,具体步骤如下:

[0085]

设定变量j,j的初始值位0;

[0086]

取被以为数据[j:0]比特为sh[j];

[0087]

变量j加1,如果变量j小于64,则重新执行步骤2,反之执行步骤5;

[0088]

输出结果sh[j]

[0089]

生成一个由64个向量sh[j]组成的数据阵列sh,然后分别对tb数据矩阵与sh数据矩阵的第n个行向量进行按位与操作,其中n为tb[i]和sh[j]数据阵列的行索引,此时索引i与索引j相同,对按位与的结果逐位逻辑或处理,得到1bit的结果tmp[n],由于数据矩阵tb和sh均有64个行向量,所以最终得到向量tmp的宽度也为64。过程如下:

[0090]

设定变量n,n的初始值为0;

[0091]

取tb[n]和sh[n],并对tb[n]和sh[n]进行按位与操作,得到向量tb_sh;

[0092]

对向量tb_sh进行逐位或处理,得到单比特结果tmp[n];

[0093]

变量n加1,如果变量n小于64,则重新执行步骤2,反之执行步骤5;

[0094]

输出结果tmp[n];

[0095]

将sh数据阵列中第n个行向量进行逐位逻辑或运算,得到sin_select[n]向量,根据sin_select[n]比特值选择对应tmp[n]值或sin值作为最终移位结果out[n],输出数据out同样为64比特宽度,具体流程如图3所示。本方法适用于任意宽度的数据移位。为方便举例,使用16bit数据为例,假设被移位数0x8fe8,移位距离0x4,对数据和因为距离值进行切割,生成16个向量组成的数据矩阵,如图4所示,最终输出移位结果值out。其中sin为移位操作需要移入的值,sin值是由移位单元外部输入信号,在riscv指令集中,移位操作中的移入值分为zero,one,signedbit,针对不同指令移入值不同,使用选择器进行选择,选择规则如下表。

[0096][0097]

实施例3

[0098]

本实施例论述右向移位器,其同样使用逻辑展开选通电路实现移位功能,且与左向移位器的移位处理单元相同,只是额外增加对输入输出数据进行反转操作,如图5所示。在硬件电路中,反转操作不会消耗任何逻辑资源。

[0099]

逻辑移位指令,算数移位指令,移位进1指令,单比特操作指令均使用一个移位器即可得到移位结果,上述类型中逻辑左移位,左移位进1移位,单比特操作指令结果由左向移位器运算并输出结果,逻辑右移位,算数移位,右移进1移位指令结果由右向移位器运算并输出结果。最终移位模块的结果根据移位控制信号选择对应移位器数据结果即可。

[0100]

当移位指令为bfp指令时,即使用操作数b的一段数据替换操作数a的某个比特区域。bfp指令格式如图6所示。从指令码中提取出off字段和len字段后,需要同时对掩码和替

换数据进行左向移位,最后对掩码和替换数据的移位结果进行逻辑与或操作。具体过程如下:

[0101]

1.根据sel字段,选择off和len数据;

[0102]

2.根据len数据计算掩码,计算代码如下:

[0103][0104]

3.使用左向移位器对掩码移位,移位距离为off数据。使用右向移位器对数据inb_a移位,移位距离为off数据,不过这里的右向移位器需要当作左向移位器使用,对移位数据inb_a和输出结果rishift_outb分别进行反转操作;

[0105]

4.对结果进行逻辑与或操作,入下代码:

[0106]

assign bfp_res=(rshift_outb_rev&lshift_outb)|(inb_b&~lshift_outb);

[0107]

bfp指令需要使用对对掩码mask数据和数据b[31:0]进行逻辑左移,为满足两个左移需要,需将右向移位器当作左向移位器使用,方法为移位数据b在进入右向移位数据前和结果输出后,均进行反转操作即可,左向移位器和右向移位器移位距离数据相同,均为off数据,左向移位器数据输入为mask数据,右向移位器数据输入为inb_a[31:0],对结果进行或与操作,得到bfp指令运算结果。

[0108]

当移位指令为循环移位和漏斗移位时,需要同时调用左向移位器和右向移位器的输出结果,并将两个移位器的结果进行或处理,如图7所示。当移位类型为循环左移时,被移位数据在左向模块移向左移位n位,且移入值为零,得到结果l_res。被移数据在右向移位模块中向右移位64

‑

n位,且移入值为零,得到移位结果r_res,将l_res与r_res进行按位或处理,即得到循环左移移位结果。循环右移反之亦然,左向移位模块向左移位64

‑

n位,右向移位模块向右移位n位,对两个移位器移位结果按位或运算,得到循环右移移位结果。

[0109]

实施例4

[0110]

本实施例公开一种risc

‑

v指令集移位指令实现电路,移位类型为漏斗移位,其操作与循环移位操作相同,差别在于被移位数据不同,循环移位数据左向移位和右向移位的被移位数据为同一个数据,而漏斗移位操作中,左向移位数据和右向移位数据为不同数据。

数据选择器负责进行数据选择。

[0111][0112]

实施例5

[0113]

本实施例公开一种risc

‑

v指令集移位指令实现电路,移位指令为循环移位和漏斗移位,需要同时调用左向移位器和右向移位器的输出结果,并将两个移位器的结果进行或处理,如图7所示。当移位类型为循环左移时,被移位数据在左向模块移向左移位n位,且移入值为零,得到结果l_res。

[0114]

被移数据在右向移位模块中向右移位64

‑

n位,且移入值为零,得到移位结果r_res,将l_res与r_res进行按位或处理,即得到循环左移移位结果。

[0115]

循环右移反之亦然,左向移位模块向左移位64

‑

n位,右向移位模块向右移位n位,对两个移位器移位结果按位或运算,得到循环右移移位结果。

[0116]

实施例6

[0117]

本实施例公开一种risc

‑

v指令集移位指令实现电路,移位类型为单比特操作时,被移位数为64’b1,使用左向移位器生成mask掩码,待运算数据与掩码进行对应的逻辑运算完成单比特操作。单比特操作包含了逻辑或操作,所以循环移位和漏斗移位复用单比特操作中的运算逻辑,单比特操作的逻辑运算见下表。运算结果需进行输出选择,如图8所示。

[0118]

指令类型逻辑运算类型sbset/sbseti/sbsetw/sbsetiw或运算sbclr/sbclri/sbclrw/sbclriw与运算,非运算sbinv/sbinvi/sbinvwsbinviw异或运算sbext/sbexti/sbextw与运算

[0119]

实施例7

[0120]

本实施例公开一种risc

‑

v指令集移位指令实现电路,因不同的移位指令最终结果输出位置并不相同,所以需要将各移位结果最终进行选择输出,移位运算有三处输出,分别为左向移位单元,右向移位单元,逻辑运算单元,其中结果输出选择与指令关系如下表:

[0121][0122]

代码如下:

[0123]

assign shift_out=is_logic_sel?shift_outb:is_rshift?rshift_outb:lshift_outb。

[0124]

综上,本发明使用两个移位单元支持所有的riscv架构的所有移位指令,提出逻辑循环展开选通的方法完成移位单元,本发明同样可应用于其他指令集机构。使用左向移位

器和右向移位器完成循环移位指令的运算。使用左向移位器和右向移位器完成漏斗位移指令运算。使用逻辑循环展开,实现左向移位器功能。右向移位器嵌套左向移位器,实现右向移位器功能。适用于其他指令集移位指令运算。

[0125]

支持riscv架构指令集包含的所有移位操作指令,且时序容易收敛,可以得到更高的主频。尤其适合追求高性能cpu的架构设计。

[0126]

以上实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的精神和范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1