在执行用于半导体设计仿真的指令的计算机系统上实现的方法与流程

在执行用于半导体设计仿真的指令的计算机系统上实现的方法

1.相关申请的交叉引用

2.本技术要求2020年2月25日提交到韩国知识产权局的韩国专利申请no.10

‑

2020

‑

0023061的优先权,其公开内容整体以引用方式并入本文中。

技术领域

3.本文所描述的发明构思的实施例涉及半导体设计,更具体地,涉及一种利用执行用于半导体设计仿真的指令的计算机系统实现的方法,在所述方法中,用户便利和电力特性被改进。

背景技术:

4.设计半导体装置的过程包括:决定指示电路块如何放置的布图规划;决定凸块和焊球的位置;基于凸块和焊球位置提取电力模型;以及测试电力模型以分析电力模型是否满足系统要求。

5.当分析的结果指示电力模型不满足系统要求时,可再次决定凸块和焊球位置,可再次提取电力模型,并且可再次测试电力模型。

6.在设计半导体装置的过程中,可能基于经验决定布图规划。因此,半导体装置的布图规划可能不是最优的,并且基于布图规划的半导体装置的特性可能不是最优的。

技术实现要素:

7.本发明构思的实施例提供一种利用执行用于半导体设计仿真的指令的计算机系统实现的方法,其生成各种布图规划,基于布图规划生成电力模型,并且选择电力模型之一。

8.根据示例性实施例,一种利用执行用于半导体设计仿真的指令的计算机系统实现的方法包括:生成多个布图规划,所述多个布图规划中的每一个布图规划包括不同地放置的多个电路块;从所述多个布图规划生成多个电力模型;以及通过选择所述多个电力模型当中满足系统要求的至少一个电力模型来选择与所述多个布图规划之一对应的布局。

9.根据示例性实施例,一种利用执行用于半导体设计仿真的指令的计算机系统实现的方法包括:生成多个布图规划,所述多个布图规划中的每一个包括不同地放置的多个电路块;从所述多个布图规划生成多个电力凸块和焊球模型;以及从所述多个电力凸块和焊球模型生成多个板电力模型。

10.根据示例性实施例,一种利用执行用于半导体设计仿真的指令的计算机系统实现的方法包括:生成多个布图规划,所述多个布图规划中的每一个包括不同地放置的多个电路块;以及从所述多个电路块生成多个电力凸块模型。

附图说明

11.通过参照附图详细描述本发明构思的示例性实施例,本发明构思的以上和其它目的和特征将变得显而易见。

12.图1示出根据本发明构思的示例实施例的半导体设计系统。

13.图2示出图1的用于利用计算机系统实现的半导体设计系统的示例方法。

14.图3示出生成多个电力凸块和焊球模型的步骤的示例。

15.图4示出生成多个布图规划的步骤的示例。

16.图5示出基于图4的方法生成多个布图规划的示例。

17.图6示出生成多个电力凸块图的步骤的示例。

18.图7示出基于图6的方法生成示例性电力凸块图的示例。

19.图8示出图3的生成多个电力连接图的步骤的示例。

20.图9示出基于图8的方法生成示例性水平电力模型的示例。

21.图10示出电力连接图的示例,其中,存在连接的网格和不存在连接的网格由不同的颜色标记。

22.图11示出图3的生成多个电力焊球图的步骤的示例。

23.图12示出基于图11的方法生成示例性电力凸块图的示例。

24.图13示出图3的生成多个水平电力模型的步骤的示例。

25.图14示出基于图13的方法生成示例性水平电力模型的示例。

26.图15示出图3的生成多个垂直电力模型的步骤的示例。

27.图16示出基于图15的方法生成示例性垂直电力模型的示例。

28.图17示出通过图3的生成电力凸块和焊球模型的步骤生成的示例性电力凸块和焊球模型。

29.图18示出生成多个芯片上电力模型的步骤的示例。

30.图19示出生成多个板电力模型的步骤的示例。

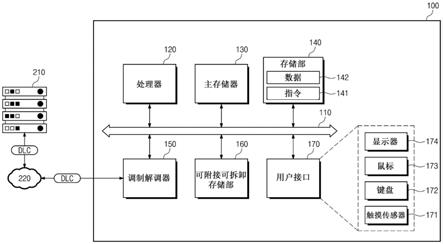

31.图20示出安装有半导体封装件的板的示例。

32.图21示出板的有效电感的示例。

33.图22示出图2的生成系统电力分析的步骤的示例。

34.图23示出图22的生成电力场景的步骤的示例。

35.图24示出通过图23的方法生成的电力场景的示例。

36.图25示出图22的生成假设(what

‑

if)条件的步骤的示例。

37.图26示出图2的生成系统电力分析的步骤的示例。

38.图27示出由半导体设计系统生成的系统电力模型的示例。

具体实施方式

39.下面,可参照附图详细描述本发明构思的实施例。相同的标号始终表示相同的元件。

40.图1示出根据本发明构思的实施例的半导体设计系统100。参照图1,半导体设计系统100包括总线110、处理器120、主存储器130、存储部140、调制解调器150、可附接可拆卸存储部160以及用户接口170。

41.总线110在半导体设计系统100的组件之间提供通道,从而允许组件向彼此发送/从彼此接收数据和指令。处理器120可控制半导体设计系统100并且可对半导体设计执行仿真。例如,处理器120可通过执行存储在存储部140中的指令141来执行用于仿真的工具(参见例如图5的工具300)。

42.指令141的至少一部分可包括基于用于半导体设计的机器学习而学习到的算法。半导体设计系统100可通过执行与算法对应的至少一些指令来执行用于半导体设计仿真的至少一部分步骤。

43.处理器120可参考存储在存储部140中的数据142来执行用于半导体设计的仿真。数据142可包括库,这些库包括半导体设计所需的各种信息、用户通过用户接口170输入的半导体设计的信息等。

44.主存储器130可以是处理器120的工作存储器。主存储器130可暂时地存储存储部140中存储的指令141和/或数据142当中处理器120所需的指令和/或数据。主存储器130可包括诸如例如dram、pram、mram或rram的高速随机存取存储器或者存储类存储器(scm)。

45.存储部140可用作半导体设计系统100的辅存储器。存储部140可存储构成半导体设计仿真工具的指令141以及用于仿真的半导体模型的数据142。存储部140可包括例如硬盘驱动器(hdd)、固态驱动器(ssd)、光盘驱动器(odd)等。

46.调制解调器150可经由网络220与外部装置210有线地或无线地通信。例如,指令141和/或数据142可作为通过调制解调器150从外部装置210下载的内容dlc(可下载内容)被存储在存储部140中。存储在存储部140中的指令141和/或数据142可通过调制解调器150被传送至外部装置210。调制解调器150可基于以太网协议和技术来操作。

47.可附接可拆卸存储部160可包括便携式存储部。例如,指令141和/或数据142可从可附接可拆卸存储部160被移至存储部140。存储在存储部140中的指令141和/或数据142可被移至可附接可拆卸存储部160。可附接可拆卸存储部160可基于诸如通用串行总线(usb)和串行高级技术附件(sata)的各种标准之一。

48.用户接口170可包括诸如例如触摸传感器171、键盘172和鼠标173的各种用户输入接口装置。用户接口170可接收用于仿真的工具的执行指令、用于工具的仿真功能的各种指令以及执行工具的仿真所需的各种信息。

49.用户接口170可包括诸如例如显示装置174的各种用户输出接口装置。用户接口170可在显示装置174上显示要仿真的半导体模型以及对半导体模型的仿真的过程和结果。

50.在示例实施例中,半导体设计系统100可利用用于半导体仿真的通用计算机或专用计算机来实现。半导体仿真工具(参见例如图5的工具300)可通过调制解调器150以指令141的形式被传送,或者可通过可附接可拆卸存储部160被安装在半导体设计系统100上。数据142可通过调制解调器150被传送,可通过可附接可拆卸存储部160被传送,或者可通过用户接口170被输入。

51.下面,将针对各个步骤描述可由半导体设计系统100执行的各种方法。可省略至少一个步骤。因此省略的至少一个步骤可由任何其它外部装置执行,或者可由用户执行。在示例实施例中,可使用通过机器学习学习到的算法来执行可由半导体设计系统100执行的各种方法的至少一个步骤。

52.下面,使用术语“凸块”和“焊球”。“凸块”可在在晶圆上形成半导体管芯时被制造,

并且可用于将半导体管芯安装在半导体封装件的板(或基板)中。“焊球”可在制造半导体封装件的过程中被制造,并且可用于将半导体封装件安装在任何其它外部装置中。“焊球”的尺寸可大于“凸块”的尺寸。

53.下面,使用术语“库”。“库”可以是可用于对半导体装置的设计进行仿真的信息集合。“库”可包括在数据142中,或者可通过网络220和调制解调器150从外部装置210传送至半导体设计系统100。

54.下面,除非明确地提及,否则半导体设计系统100可使用(或参考)的信息可通过用户接口170从用户被输入,可通过可附接可拆卸存储部160被传送,和/或可通过网络220和调制解调器150从外部装置210被传送。

55.图2示出图1的用于利用计算机系统实现的半导体设计系统100的方法。参照图1和图2,在步骤s110中,半导体设计系统100可生成多个布图规划的多个电力凸块和焊球模型。例如,电力凸块和焊球模型可以是与被测半导体封装件的电力凸块和焊球对应的布局。

56.在步骤s120中,半导体设计系统100可针对每个电力凸块和焊球模型生成多个芯片上电力模型。在步骤s130中,半导体设计系统100可生成多个板电力模型。

57.在步骤s140中,半导体设计系统100可根据多个电力凸块和焊球模型、多个芯片上电力模型和多个板电力模型生成系统电力模型,并且可对系统电力模型执行系统电力分析。

58.在步骤s150中,半导体设计系统100可提供(例如,显示)满足系统要求的至少一个电力模型。例如,半导体设计系统100可在显示装置174上显示至少一个电力模型。

59.根据本发明构思的示例实施例,可通过一个工具执行布图规划的生成、电力凸块和焊球模型的生成、芯片上电力模型的生成、板电力模型的生成、系统电力模型的生成以及系统电力分析。因此,可改进用户便利。

60.另外,根据本发明构思的示例实施例,根据各种布图规划生成系统电力模型,并且针对各种布图规划中的每一个布图规划执行系统电力分析。由于考虑各种布图规划,所以在步骤s 150中提供的至少一个系统电力模型可具有进一步改进的电力特性。

61.图3示出生成多个电力凸块和焊球模型的步骤(图2的步骤s110)的示例。参照图1和图3,在步骤s210中,半导体设计系统100可生成多个布图规划。多个布图规划可被配置为将电路块放置在不同的部分或位置。电路块可包括用于执行给定功能的给定设计。电路块可被称为“知识产权(intel lectual property,ip)”。如本文所使用的,知识产权(ip)也可被称为知识产权核(intellectual property cores),并且可用于表示向系统提供宏功能的自包含分立单元。本领域技术人员将理解,所公开的知识产权或知识产权核由诸如逻辑电路、分立组件、微处理器、硬连线电路、存储器元件、布线连接、总线、通信链路等的电子(或光学)电路物理实现,其可使用基于半导体的制造技术或其它制造技术形成。

62.在步骤s220中,半导体设计系统100可针对每个布图规划生成电力凸块图。例如,在步骤s220中,可生成分别与多个布图规划对应的多个电力凸块图。多个电力凸块图可在多个布图规划上被生成,并且可被视为分别包括多个布图规划。

63.在步骤s230中,半导体设计系统100可生成电力凸块图的电力凸块的电力连接图。例如,在步骤s230中,可生成分别与多个布图规划对应的多个电力连接图。多个电力连接图可在多个电力凸块图上被生成,并且可被视为分别包括多个电力凸块图(或多个布图规

划)。

64.在步骤s240中,半导体设计系统100可针对每个布图规划生成多个电力焊球图。例如,在步骤s240中,可根据多个电力连接图生成数量比多个电力连接图的数量更多的电力焊球图。可通过改变每个电力连接图处的电力焊球的数量和电力焊球的位置来生成多个电力焊球图。

65.可在多个电力连接图上生成多个电力焊球图,并且多个电力焊球图中的每一个电力焊球图可被视为包括对应的布图规划、对应的电力凸块图和对应的电力连接图。

66.在步骤s250中,半导体设计系统100可生成多个水平电力模型。水平电力模型中的每一个水平电力模型可包括在多个电力焊球图中的对应的电力焊球图处连接电力凸块和电力焊球的水平连接的电阻和电感(或电容)组件的模型。

67.在步骤s260中,半导体设计系统100可生成多个垂直电力模型。垂直电力模型中的每一个垂直电力模型可包括在多个电力焊球图中的对应的电力焊球图处连接电力凸块和电力焊球的垂直连接的电阻和电感(或电容)组件的模型。

68.在步骤s270中,半导体设计系统100可基于多个电力焊球图、多个水平电力模型和多个垂直电力模型生成多个凸块和焊球模型。多个凸块和焊球模型中的每一个凸块和焊球模型可以是基于多个布图规划中的对应的布图规划的。

69.多个凸块和焊球模型中的每一个凸块和焊球模型可以是基于多个水平电力模型中的对应的水平电力模型和多个垂直电力模型中的对应的垂直电力模型的。例如,当多个布图规划中的对应布图规划被选择时,多个凸块和焊球模型中的每一个凸块和焊球模型可包括电力凸块和电力焊球之间的电力模型(例如,由电阻、电感或电容组件表示)。

70.图4示出生成多个布图规划的步骤(图3的步骤s210)的示例。图5示出基于图4的方法生成多个布图规划的示例。参照图1、图4和图5,在步骤s211中,半导体设计系统100可接收电路块的信息in和关联的电力凸块图。

71.例如,用户可通过用户接口170将信息in输入到半导体设计系统100。可替代地,信息in可通过调制解调器150从外部装置210被传送至半导体设计系统100,或者可由可附接可拆卸存储部160被传送至半导体设计系统100。

72.在示例实施例中,为了对半导体设计进行仿真,可输入第一电路块cb1至第七电路块cb7作为信息in。例如,第一电路块cb1至第七电路块cb7中的第五电路块cb5可具有关联的凸块图,其余的电路块可不具有关联的凸块图。信息in还可包括关于第一电路块cb1至第七电路块cb7的各种信息(诸如功耗信息和功能信息)。

73.在实施例中,信息in可包括关于第一电路块cb1至第七电路块cb7的识别信息。半导体设计系统100可从包括电路块的各种信息(诸如功率信息和功能信息)的库获得关联的信息。

74.在步骤s212中,半导体设计系统100可接收多个电路块在多个布图规划中的放置的约束。约束可通过用户接口170被输入到半导体设计系统100。可替代地,约束可通过调制解调器150从外部装置210被传送至半导体设计系统100,或者可由可附接可拆卸存储部160传送至半导体设计系统100。

75.在示例实施例中,约束可包括根据多个布图规划的区域的放置次序。约束可在多个布图规划中按从最大至最小的次序限定第一电路块cb1至第七电路块cb7的放置。可替代

地,约束可限定第一电路块cb1至第七电路块cb7的放置,使得在多个布图规划中第一电路块cb1至第七电路块cb7当中尺寸大于阈值的电路块在尺寸等于或小于阈值的电路块之前被放置。

76.约束可限定被配置为与外部装置210通信的接口放置在外侧部分。例如,第二电路块cb2可以是被配置为与外部装置210连接的接口。可替代地,约束可限定串行器和解串器的电路块放置在多个布图规划的外侧部分。

77.约束可限定第一电路块cb1至第七电路块cb7当中消耗高功率的电路块放置在多个布图规划的中心。约束可限定将由约束限定的特定电路块放置为彼此间隔开比由约束限定的特定距离短的距离。例如,约束可限定将特定电路块放置为间隔开小于最大特定距离的距离。

78.在步骤s213中,半导体设计系统100可生成电路块的多个布图规划。半导体设计系统100可通过用户接口170显示因此生成的多个布图规划。例如,半导体设计系统100可将多个布图规划显示在显示装置174上。

79.约束还可限定显示优先级。例如,约束可向多个布图规划分配优先级。详细地,约束可限定优先级的分配,使得随着多个布图规划中的每一个的总尺寸减小,优先级变高。另外,约束可限定基于分配的优先级通过用户接口170的显示装置174显示多个布图规划。

80.例如,半导体设计系统100可在显示装置174上将多个布图规划当中具有较高优先级的布图规划显示在具有较低优先级的布图规划之前,或者可将较高优先级布图规划显示在显示装置174的屏幕的左侧或顶部。半导体设计系统100可将多个布图规划当中具有较低优先级的布图规划显示在具有较高优先级的布图规划之后,或者可将较低优先级布图规划显示在显示装置174的屏幕的右侧或底部。

81.约束可限定丢弃布图规划的方式。约束可限定丢弃总尺寸各自大于阈值的布图规划,并且生成和显示总尺寸各自等于或小于阈值的布图规划,作为多个布图规划。

82.在图5中,可由工具300根据信息in生成第一布图规划fp1至第n布图规划fpn(n是正整数)。在图5的示例中,可基于约束将消耗高功率的第五电路块cb5放置在中心,并且可将执行接口的功能的第二电路块cb2放置在第一布图规划fp1至第n布图规划fpn的外侧部分。

83.在步骤s214中,半导体设计系统100可确定修改是否被请求。例如,当用户通过用户接口170输入至少一个布图规划的修改时,可确定修改被请求(步骤s214,是)。修改可包括与第一电路块cb1至第七电路块cb7中的至少一个的位置或取向关联的修改或者与至少一个约束关联的修改(例如,添加、删除或改变至少一个约束)。

84.在步骤s215中,半导体设计系统100可对至少一个布图规划应用用户请求的修改。

85.图6示出生成多个电力凸块图的步骤(图3的步骤s220)的示例。图7示出基于图6的方法生成示例性电力凸块图bmpk1的示例。

86.参照图1、图6和图7,在步骤s221中,半导体设计系统100可通过与信息in关联描述的各种方法之一接收电力凸块间距的信息。

87.在步骤s222中,半导体设计系统100可基于电力凸块间距来放置多个电力凸块bump。例如,半导体设计系统100可将电力凸块bump放置在指定用于电力以外的信号的空间以外的空间中以及具有类似第五电路块cb5的凸块图的电路块的空间以外的空间中。

88.可接收关于禁止放置电力凸块的空间的信息作为信息in的一部分。可替代地,可基于信息in从库获得关于禁止放置电力凸块的空间的信息。

89.在步骤s223中,半导体设计系统100可确定是否存在指派库。当存在指派库时(步骤s223,是),在步骤s224中,半导体设计系统100可基于指派库来放置多个接地凸块。当不存在指派库时(步骤s223,否),在步骤s225中,半导体设计系统100可将至少一个接地凸块放置在每个电力凸块“bump”处。半导体设计系统100可通过用户接口170显示电力凸块图。例如,半导体设计系统100可将电力凸块图显示在显示装置174上。

90.在步骤s226中,半导体设计系统100可确定修改是否被请求。例如,当用户通过用户接口170输入至少一个电力凸块图的修改时,可确定修改被请求(步骤s226,是)。

91.在步骤s227中,半导体设计系统100可对至少一个电力凸块图应用用户请求的修改。当对至少一个电力凸块图应用修改时,半导体设计系统100可将至少一个修改的电力凸块图显示在显示装置174上。

92.图8示出图3的生成多个电力连接图的步骤(图3的步骤s230)的示例。图9示出基于图8的方法生成与一个凸块图bmpk1对应的连接图bmpk2的示例。

93.参照图1、图8和图9,在步骤s231中,半导体设计系统100可接收对电力连接图的约束。可通过参考信息in提及的各种方法之一接收约束。约束可包括关于网格的大小和单位距离的信息。

94.在步骤s232中,半导体设计系统100可基于约束生成网格。半导体设计系统100可将间隔等于或小于由约束限定的单位距离的所有电力凸块连接。另外,如约束所限定的,半导体设计系统100可将在单位距离或更小的间隔内不存在相邻电力凸块的孤立的电力凸块与最近的电力凸块连接。

95.在示例实施例中,如图9所示,网格的大小可被设定为等于凸块间距,但是网格大小不限于此。另外,单位距离可被设定为一个网格,但是单位距离不限于此。本文中,术语“网格”可指形成网格结构的单独的单元,网格的大小可指单独的单元的平行边之间的距离。在图9中,网格结构由虚线示出。

96.在步骤s233中,半导体设计系统100可基于约束添加连接cnt以生成电力连接图。连接cnt可将每个电力凸块bump连接到一个或多个其它电力凸块bump。在步骤s234中,半导体设计系统100可基于网格结构显示电力连接图。例如,如图9所示,半导体设计系统100可通过用户接口170在网格上显示连接cnt。例如,半导体设计系统100可将显示连接cnt显示在显示装置174上。

97.又如,如图10所示,半导体设计系统100可由“1”显示网格当中存在连接cnt的网格,并且可由“0”显示不存在连接cnt的网格。半导体设计系统100可在网格上显示以不同的颜色标记“1”和“0”的电力连接图bmpk3。

98.在步骤s235中,半导体设计系统100可确定修改是否被请求。例如,当用户通过用户接口170输入至少一个电力连接图的修改时,可确定修改被请求(步骤s235,是)。

99.在步骤s236中,半导体设计系统100可对至少一个电力连接图应用用户请求的修改。当对至少一个电力连接图应用修改时,半导体设计系统100可将至少一个修改的电力连接图显示在显示装置174上。

100.图11示出图3的生成多个电力焊球图的步骤(图3的步骤s240)的示例。图12示出基

于图11的方法生成示例性电力焊球图bmk的示例。

101.参照图1、图11和图12,在步骤s241中,半导体设计系统100可通过与信息in关联描述的各种方法之一接收约束。约束可包括诸如电力焊球间距、电力焊球的最小值和最大值(例如,电力焊球的最小数量和电力焊球的最大数量)以及关于无法放置电力焊球的区域的信息的各种信息。

102.在步骤s242中,半导体设计系统100可基于电力焊球间距检测能够放置多个电力焊球的位置。在图12中,电力焊球间距与两个网格对应,并且以粗圆圈的形式标记能够放置电力焊球的位置(类似第一焊球ball1)。

103.在步骤s243中,半导体设计系统100可指派各种电力焊球图以生成多个电力焊球图。例如,半导体设计系统100可通过(在从最大值至最小值的范围内)改变电力焊球的数量或者改变电力焊球的位置来根据一个电力连接图生成多个电力焊球图。

104.通过改变电力焊球的数量和电力焊球的位置,可以在电力焊球图中包括各种电力特性。在图12中,第一焊球ball1当中实际放置电力焊球的焊球由填充有斜线的第二焊球ball2标记。

105.在步骤s244中,半导体设计系统100可确定修改是否被请求。例如,当用户通过用户接口170输入至少一个电力焊球图的修改时,可确定修改被请求(步骤s244,是)。

106.在步骤s245中,半导体设计系统100可对至少一个电力焊球图应用用户请求的修改。

107.在示例实施例中,可基于电力凸块的凸块间距和电力焊球的焊球间距确定网格的大小。网格的大小可与电力凸块的凸块间距和电力焊球的焊球间距的最大共同因素对应。

108.图13示出图3的生成多个水平电力模型的步骤(图3的步骤s250)的示例。图14示出基于图13的方法生成示例性水平电力模型的示例。在实施例中,图13和图14中示出生成与一个电力焊球图对应的水平电力模型的示例。

109.参照图1、图13和图14,在步骤s251中,半导体设计系统100可选择水平层。例如,水平层可包括连接电力凸块和电力焊球的至少一个水平连接。水平连接可以是在与布图规划的平面平行的方向上延伸的连接。

110.例如,水平层可包括图9的电力连接图bmpk2。半导体设计系统100可基于图10的网格以矩阵的形式管理图9的电力连接图bmpk2的信息。

111.如图10所示,半导体设计系统100可针对各个水平层生成基于网格的矩阵。半导体设计系统100可针对每个水平层区分存在连接的网格与不存在连接的网格。

112.在步骤s252中,半导体设计系统100可在所选水平层上选择水平连接。例如,可从图10的矩阵的信息选择与“1”对应的网格。

113.在步骤s253中,半导体设计系统100可将电力模型指派给所检测到的水平连接。在步骤s254中,半导体设计系统100可确定是否已向所选层的每个网格指派电力模型。如果还未向所选层的每一个网格指派电力模型(步骤s254,否),则可重复步骤s252和步骤s253,直至向所选层的最后网格被指派电力模型(步骤s254,是)。

114.在步骤s255中,半导体设计系统100可确定是否已针对水平层中的每一个水平层指派电力模型。如果还未向水平层中的每一个水平层指派电力模型(步骤s255,否),则针对其余的水平层,可重复步骤s251、步骤s252和步骤s253,直至向最后的水平层指派电力模型

(步骤s255,是)。例如,其余的水平层可以是包括水平连接的重分布层(rdl)。

115.在实施例中,如图14所示,由于存在于连接电力凸块bump的各个网格中的连接具有相同的长度,所以连接可被相同地建模为第一电阻r1和第一电感l1。在其余的水平层处,存在于一个网格中的连接也可被相同地建模为第一电阻r1和第一电感l1。

116.在实施例中,第一电阻r1和第一电感l1可参考由封装件类型确定的库来获得,或者可使用已知方程来获得。

117.图15示出图3的生成多个垂直电力模型的步骤(图3的步骤s260)的示例。图16示出基于图15的方法生成示例性垂直电力模型的示例。在实施例中,图15和图16中示出生成与一个电力焊球图对应的垂直电力模型的示例。

118.参照图1、图15和图16,在步骤s261中,半导体设计系统100可选择垂直层。例如,垂直层可包括连接电力凸块bump和电力焊球ball的至少一个垂直连接(例如,通孔via1、via2和via3中的至少一个)。垂直连接可以是在与布图规划的平面垂直的方向上延伸的连接。

119.半导体设计系统100可针对各个垂直层生成基于网格的矩阵,如图10所示。半导体设计系统100可针对每个垂直层区分存在连接的网格与不存在连接的网格。

120.在步骤s262中,半导体设计系统100可在所选垂直层上选择垂直连接。例如,可从类似图10所示的基于网格的信息选择与“1”对应的网格。

121.在步骤s263中,半导体设计系统100可将电力模型指派给检测到的垂直连接。在步骤s264中,半导体设计系统100可确定是否已向所选垂直层的每个网格指派电力模型。如果还未向所选垂直层的每一个网格指派电力模型(步骤s264,否),则可重复步骤s262和步骤s263,直至向所选层的最后网格指派电力模型(步骤s264,是)。

122.在步骤s265中,半导体设计系统100可确定是否已向垂直层中的每一个垂直层指派电力模型。如果还未向垂直层中的每一个垂直层指派电力模型(步骤s265,否),则针对其余的垂直层,可重复步骤s262和步骤s263,直至向最后的垂直层指派电力模型(步骤s265,是)。

123.在实施例中,如图16所示,存在于连接电力凸块bump的各个网格中的连接可被相同地建模为第二电阻r2和第二电感l2。第二电阻r2和第二电感l2可根据垂直连接中的每一个垂直连接(例如,通孔via1、via2和via3中的至少一个)的高度和厚度(或横截面积)被不同地建模。

124.在示例实施例中,第二电阻r2和第二电感l2可参考由封装件类型确定的库来获得,或者可使用已知方程来获得。

125.图17示出通过图3的生成电力凸块和焊球模型的步骤(图3的步骤s270)生成的示例性电力凸块和焊球模型。参照图1和图17,通过参照图13和图14描述的处理,通过使用基于网格的矩阵将电力凸块与电力焊球之间的水平层建模为水平电力模型。

126.另外,通过参照图15和图16描述的处理,通过使用基于网格的矩阵将电力凸块与电力焊球之间的垂直层建模为垂直电力模型。垂直电力模型和水平电力模型是基于相同大小的矩阵的。

127.因此,可根据垂直电力模型和水平电力模型生成连接电力凸块和电力焊球的多个电力凸块和焊球模型。在实施例中,如图17所示,可使用spice以网表nl的形式对多个电力凸块和焊球模型进行建模。

128.图18示出生成多个芯片上电力模型的步骤(图2的步骤s120)的示例。参照图1和图18,在步骤s121中,半导体设计系统100可选择包括在布图规划中的多个电路块中的一个电路块cb。

129.在步骤s122中,半导体设计系统100可接收所选电路块的芯片上电容和芯片上电阻。例如,半导体设计系统100可从库或用户接收芯片上电容和芯片上电阻。例如,当从电力凸块看时,芯片上电容和芯片上电阻可包括每个电路块处所示的电容和电阻。

130.在步骤s123中,半导体设计系统100可将芯片上电容和芯片上电阻指派给所选电路块cb。在步骤s124中,半导体设计系统100可确定是否已针对电路块中的每一个电路块指派了芯片上电容和芯片上电阻。如果还未向电路块中的每一个电路块指派芯片上电容和芯片上电阻(步骤s124,否),则半导体设计系统100可重复步骤s121至步骤s123,直至向最后的电路块指派芯片上电容和芯片上电阻(步骤s 124,是)。

131.当执行图3至图18的方法时,可获得半导体装置的封装件级别电力模型。在示例实施例中,根据半导体设计的目的,半导体设计系统100可仅执行图3至图17的电力凸块和焊球模型的生成,或者还可执行图18的封装件级别电力模型的生成以及图3至图17的电力凸块和焊球模型的生成。

132.图19示出生成多个板电力模型的步骤(图2的步骤s130)的示例。图20示出半导体封装件410被安装在板400上的示例。参照图1、图19和图20,半导体封装件410的电力焊球pb和接地焊球gb可与板400的电力通孔pv和接地通孔gv连接。

133.半导体封装件410可安装在板400的上表面上。电力通孔pv和接地通孔gv可与板400的下表面上的解耦电容器dec连接。电力通孔pv可通过电力线pl(在图20中由实线示出)和第六电感器l6从电源管理集成电路(pmic)420接收电力。电力通孔pv的特定位置的电压可通过反馈线fl传送至pmic 420。

134.电力通孔pv可被建模为第三电阻r3和第三电感l3。接地通孔gv可被建模为第四电阻r4和第四电感l4。解耦电容器dec可被建模为电容器“c”、第五电阻r5和第五电感l5。第三电阻r3和第三电感l3可根据电力通孔pv的高度和厚度(或横截面积)来建模。

135.接地通孔gv可通过由虚线标记的接地线gl从pmic 420接收接地电压。第四电阻r4和第四电感l4可根据接地通孔gv的高度和厚度(或横截面积)来建模。通孔pv和gv以及解耦电容器dec的电力模型可例如参考库来建模。

136.图21示出板400的有效电感的示例。参照图1、图19、图20和图21,板400的电感可被建模为:电容器电感lc,是与解耦电容器dec关联的电感的总和;通孔电感lv,是与电力通孔pv关联的电感的总和,并与半导体封装件410的电力焊球pb连接;以及线电感ll,是电力通孔pv与pmic 420之间的电感的总和,并与pmic 420连接。

137.在示例实施例中,线电感ll可小于电容器电感lc和通孔电感lv,因此可被忽略。例如,板400的电感可被建模为电容器电感lc和通孔电感lv之和。

138.在示例实施例中,板电力模型可为第三电阻r3、第三电感l3、电容c、第五电阻r5和第五电感l5串联连接的形式。通孔电感lv可对应于第三电感l3,电容器电感lc可对应于第五电感l5。

139.如上所述,基于通孔形成板400的电力模型。因此,半导体设计系统100可针对板400的电力通孔中的每一个电力通孔生成电力模型。

140.在步骤s131中,半导体设计系统100可选择板400的通孔中的一个电力通孔。在步骤s132中,半导体设计系统100可基于与所选通孔关联的解耦电容器dec的信息和板400的信息(或板400的通孔的信息)来生成所选通孔的电力模型。例如,可从库获得解耦电容器dec的信息和板400的信息。

141.在步骤s133中,半导体设计系统100可确定是否已针对所有电力通孔生成了电力模型。如果还未针对电力通孔中的每一个电力通孔生成电力模型(步骤s 133,否),则半导体设计系统100可重复步骤s 131和步骤s132,直至生成所有电力通孔的电力模型(步骤s 133,是)。可针对每个半导体封装件的电力模型执行步骤s131和步骤s133。通过将与半导体封装件的电力模型对应的板电力模型组合,可在板级别获得安装有半导体封装件的板的电力模型(即,系统电力模型)。

142.图22示出图2的生成系统电力分析的步骤(图2的步骤s140)的示例。参照图1和图22,在步骤s310中,半导体设计系统100可生成半导体封装件操作的电力场景。

143.在步骤s320中,半导体设计系统100可针对每个板模型设定假设(what

‑

if)条件。在步骤s330中,半导体设计系统100可基于电力场景和what

‑

if条件执行系统电力分析。例如,步骤s330可对应于图2的步骤s140(或者可包括在其中或者可与其相同)。

144.图23示出图22的生成电力场景的步骤(图22的步骤s310)的示例。参照图1和图23,在步骤s311中,半导体设计系统100可选择多个电路块中的一个电路块cb。在步骤s312中,半导体设计系统100可接收所选电路块cb的最大功率和空闲功率。

145.在步骤s313中,半导体设计系统100可生成活动状态与空闲状态之间的转变场景作为电力场景。在步骤s314中,半导体设计系统100可确定是否已针对所有电路块生成了转变场景。如果还未针对电路块中的每一个电路块生成转变场景(步骤s314,否),则半导体设计系统100可重复步骤s311至步骤s313,直至生成所有电路块的转变场景(步骤s314,是)。

146.在实施例中,图23中描述了针对每个电路块生成电力场景时的示例,但是可针对半导体封装件的整个系统电力模型生成一个相同的电力场景。

147.图24示出通过图23的方法生成的电力场景的示例。在图24中,水平轴表示时间“t”,垂直轴表示电流“i”。参照图1和图24,半导体设计系统100可生成半导体封装件(或电路块)从电流不流动的截止状态off进入第一电流i1流动的空闲状态idle的电力场景。

148.另外,在进入空闲状态idle之后,半导体设计系统100可生成半导体封装件具有“m”个转变循环的电力场景,每个转变循环包括从空闲状态到第二电流i2流动的活动状态active的转变以及从活动状态active到空闲状态idle的转变。另外,半导体设计系统100可生成半导体封装件在“m”个转变循环之后转变为截止状态off的电力场景。

149.在示例实施例中,半导体设计系统100可针对每个系统电力模型或者针对每个电路块生成两个或多个不同的电力场景。这两个或多个不同的电力场景可连续地被执行,并且这可被视为一个电力场景被执行一样。例如,电力场景可被解释为包括以不同的模式进行转变的两个或更多个周期。

150.图25示出图22的生成what

‑

if条件的步骤(图22的步骤s320)的示例。参照图1和图25,在步骤s321中,半导体设计系统100可设定转变的时钟循环数。例如,半导体设计系统100可设定从空闲状态idle进入活动状态active所需的时钟循环数。

151.随着时钟循环数增加,系统电力模型的电力完整性可增加,并且系统性能可变好。

随着时钟循环数减少,系统电力模型的电力完整性可降低,并且系统性能可变差。

152.在步骤s322中,半导体设计系统100可设定解耦电容器的数量。在步骤s323中,半导体设计系统100可设定解耦电容器的电容。通过步骤s322和步骤s323,可调节与系统电力模型的电力板模型的解耦电容器关联的参数。

153.图26示出图2的生成系统电力分析的步骤(图2的步骤s140)的示例。参照图2和图26,在步骤s141中,半导体设计系统100可生成多个系统电力模型。例如,半导体设计系统100可使用spice程序模拟平台(spice deck)生成系统电力模型。

154.半导体设计系统100可包括模板形式的用于各种封装件(诸如层叠封装件(pop)、包括中介层的2.5d封装以及3d封装)的参考spice程序模拟平台。半导体设计系统100可通过选择封装件类型并修改一些参数容易地生成系统电力模型。

155.图27示出由半导体设计系统100生成的系统电力模型500的示例。参照图1、图20和图27,系统电力模型500可包括电压源510、板阻抗520、凸块和焊球阻抗530、芯片上阻抗540和电流宿(current sink)550。

156.电压源510可以是与pmic 420所供应的供电电压相同的供电电压。板阻抗520可以是板电力模型的阻抗。凸块和焊球阻抗530可以是电力凸块和焊球模型的阻抗。芯片上阻抗540可包括电路块的芯片上电容和芯片上电阻。电流宿550可根据电力场景消耗电流。凸块节点bn可对应于电力凸块。凸块节点bn的电压可以是电力凸块的电压。

157.参照图1、图26和图27,在步骤s142中,半导体设计系统100可选择多个系统电力模型500中的一个系统电力模型500。在步骤s143中,半导体设计系统100可基于电力场景执行噪声分析。例如,在电流宿550根据电力场景消耗电流的同时,半导体设计系统100可监测凸块节点bn的电压改变。

158.在步骤s144中,半导体设计系统100可确定噪声是否小于阈值。当噪声小于阈值时(步骤s144,是),在步骤s145中,半导体设计系统100可确定所选系统电力模型500满足系统要求。当噪声不小于阈值时(步骤s144,否),在步骤s146中,半导体设计系统100可确定所选系统电力模型500不满足系统要求。

159.半导体设计系统100可存储确定结果。在步骤s147中,半导体设计系统100可确定针对所有系统电力模型的噪声分析是否均完成。如果还未针对所有系统电力模型完成噪声分析(步骤s147,否),则半导体设计系统100可重复步骤s142至步骤s146,直至针对所有系统电力模型的噪声分析均完成(步骤s147,是)。

160.之后,如参照图2的步骤s150描述的,半导体设计系统100可在显示装置174上向用户显示满足系统要求的至少一个系统电力模型。用户可选择满足系统要求的适当一个系统电力模型,并且可选择与所选系统电力模型对应的半导体布局。

161.如上所述,根据本发明构思的示例实施例,生成应用了布图规划的改变的系统电力模型,并且执行噪声分析。因此,可考虑布图规划对系统电力模型的影响来确定系统电力模型和半导体布局。

162.根据本发明构思的示例实施例,可通过一个工具执行布图规划的生成、电力凸块图的生成、电力连接图的生成、电力焊球图的生成、水平电力模型的生成、垂直电力模型的生成、包括芯片上电阻和芯片上电容的芯片上电力模型的生成、板电力模型的生成、系统电力模型的生成以及系统电力模型的分析。因此,可提高半导体设计的用户便利。

163.在示例实施例中,半导体设计系统100还可执行频域的分析以及时域的分析。半导体设计系统100可与另一仿真工具(例如,hspice)一起执行噪声分析,并且半导体设计系统100本身也可执行噪声分析。

164.在示例实施例中,半导体设计系统100可使用fft(快速傅里叶变换)和ifft(逆fft)执行噪声分析。通过使用fft,半导体设计系统100可生成系统电力模型500的阻抗的频率响应z(f),并且可生成电力场景的频率响应i(f)。

165.半导体设计系统100可通过将阻抗的频率响应z(f)与电力场景的频率响应i(f)相乘来生成凸块节点bn的电压的频率响应v(f)((v(f)=z(f)*i(f))。半导体设计系统100可基于ifft来获得凸块节点bn的电压的时间响应。

166.在示例实施例中,半导体设计系统100可重复以下操作:改变what

‑

if条件,生成多个系统电力模型,并针对多个系统电力模型中的每一个系统电力模型执行噪声分析。

167.在上述示例实施例中,术语“约束”和术语“信息”用于可区分彼此。然而,术语“约束”和术语“信息”可能无法彼此清楚地区分,并且可根据上下文来解释。例如,“约束”可包括关于要约束的身份必须遵循的规则的信息。“信息”可包括特定身份必须遵循的“约束”。术语“信息”和“约束”可以是相对的,并且可根据上下文互换使用。

168.在上述示例实施例中,通过使用术语“第一”、“第二”、“第三”等来描述根据本发明构思的组件。然而,术语“第一”、“第二”、“第三”等可用于将组件彼此区分,而非限制本发明构思。例如,术语“第一”、“第二”、“第三”等不涉及任何形式的次序或数字含义。

169.根据本发明构思,通过利用计算机系统实现的工具自动地或半自动地生成布图规划。因此,可改进用户便利。另外,由于基于各种布图规划从电力模型中选择至少一个,所以可改进电力特性。

170.尽管已参照本发明构思的示例性实施例描述了本发明构思,但是对于本领域普通技术人员而言将显而易见的是,在不脱离所附权利要求中阐述的本发明构思的精神和范围的情况下,可对其进行各种改变和修改。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1