门级网表的处理方法、计算机存储介质与流程

1.本发明涉及门电路仿真技术领域,尤其涉及在对门级网表文件进行仿真前,对门级网表的处理方法。

背景技术:

2.在对门级数字集成电路(以下简称为门电路)进行仿真之前,需要对门电路的门级网表文件进行处理,例如非常大型的门电路在仿真时,为了提高效率,需要对门电路进行分割、分组,使得门电路可以分割为多个子块,然后再对多个子块进行并行处理,以此来提高仿真效率。

3.而门级网表文件不能直接被用来对门电路进行运算(如分割、分组),因而需要用适当的数学形式来表征数字集成电路的门级网表。门级网表中包含门电路的实例化和基于端口映射的连接关系,根据门级网表可以画出一张门电路的连接图。而现有技术中通常采用邻接矩阵来表示门电路,使得门电路可以进行分割或分组,之后再基于分割后的门电路所对应的邻接矩阵来生成新的门级网表,以进行仿真处理。

4.但是邻接矩阵会丢失掉门电路的一些信息,如门的类型、门的输入端口与驱动端(也称之为电路输入端口)的连接关系、门的输出端口与负载输入端(也称之为电路输出端口)的连接关系等。门的类型直接决定了门的逻辑功能和延时大小;不同输入端口的负载电容不同,连接在此端口上的驱动门的延时和功耗也不同;不同输出端口的驱动能力不同,此端口的延时与功耗也不同。对于组合逻辑门,不同的输入模式带来的延时不同;对于时序逻辑门,数据输入(d)端与时钟输入(ck)端的时序分析方式不同。

5.而数字集成电路的分析与处理除了关注连接关系,还要关注门的功能,计算延时、功耗、尺寸等信息,在对表征门级网表的矩阵进行计算的过程中,需要这些除了连接关系之外的信息。对矩阵计算完成后,根据矩阵的计算结果重新输出处理(如分割、分组等)后的电路网表时,也需要门的类型、输入输出端口信息(如名称)、连接关系等信息,但是目前的邻接矩阵以及通过分割后的邻接矩阵转换的新的门级网表要么丢失了这些信息,要么需要非常繁杂的流程去重新获得这些信息,导致仿真进展不顺利。

6.因此,如何提供一种门级网表的处理方法是业界亟待解决的技术问题。

技术实现要素:

7.为了解决现有技术中邻接矩阵表示的门电路信息量较少的技术问题,本发明提出一种门级网表的处理方法、计算机存储介质。

8.本发明提出门级网表的处理方法,包括:步骤1,将原始网表文件对应的门电路的电路连接关系采用驱动矩阵进行表示,所述驱动矩阵的行向量和列向量分别从以下两者任选一种:门,所述门所对应的同一类型的连接端口的信息,当某一个连接端口与一个门相连接时,所述驱动矩阵中该门与该连接端口所指向的矩阵元素的取值为该门与该连接端口相连接的端口的信息的集合;

步骤2,基于用来表征原始网表文件对应的门电路的驱动矩阵对该门电路进行运算,得到用来表征运算后的门电路的驱动矩阵;步骤3,基于每一个运算后的门电路所对应的驱动矩阵,重建每一个运算后的门电路的新网表文件。

9.进一步,可表征任意门电路的电路连接关系的驱动矩阵包括:表征对应门电路的所有门与所有门的所有输出端口之间连接关系的内部驱动矩阵,表征对应门电路的所有门与所有电路输出端口之间连接关系的输出驱动矩阵,以及表征对应门电路的所有门与所有电路输入端口之间连接关系的输入驱动矩阵。

10.进一步,所述运算包括对原始网表文件对应的门电路进行分割或分组。

11.进一步,重建运算后的门电路的新网表文件包括:步骤3.1,将输出驱动矩阵转化为用于表征对应门电路的所有门的输出端口与所有电路输出端口之间连接关系的新输出驱动矩阵,且以内部驱动矩阵的行向量和列向量为基准,使得所述新输出驱动矩阵与所述内部驱动矩阵用来表征所有门的输出端口的向量均为行向量,或者均为列向量;步骤3.2,基于相同的行向量或者相同的列向量,将所述内部驱动矩阵与所述新输出驱动矩阵拼接成用来表征所有门的输出端口与所有门及电路输出端口之间连接关系的总输出驱动矩阵;步骤3.3,根据所述总输出驱动矩阵的矩阵元素的取值得到每一个门的输出端口的连线信息;步骤3.4,创建待连线的门列表;步骤3.5,将内部驱动矩阵用来表征所有门的输出端口的向量的元素采用该输出端口对应的连线信息进行替换,得到新内部驱动矩阵;步骤3.6,基于相同的行向量或者相同的列向量,将所述新内部驱动矩阵与输入驱动矩阵拼接成输入输出驱动矩阵;步骤3.7,基于所述输入输出驱动矩阵生成每一个门及其对应的输入端口连线、输出端口连线的信息;步骤3.8,为每一个门添加类型信息及格式化信息;步骤3.9,将所有门及其对应的信息输出到新网表文件。

12.进一步,生成所述新输出驱动矩阵包括:步骤3.1.1,判断所述输出驱动矩阵用来表征门的行或列是否与所述内部驱动矩阵用来表征门的输出端口的行或列均为行向量,或者是否均为列向量,若否,则将所述输出驱动矩阵进行转置,再继续下一步骤;若是,则直接继续下一步骤;步骤3.1.2,根据用来表征所有门的所有输出端口的向量判断一个门是否具有多个输出端口,若一个门具有多个输出端口,则将所述输出驱动矩阵中该门所对应的行或列进行复制,使得该门所对应的行或列的数量与其输出端口数量一致;步骤3.1.3,将复制后的所述输出驱动矩阵中的行向量或列向量中的门分别采用该门的各个输出端口进行替换;步骤3.1.4,将替换后的所述输出驱动矩阵中每一个门的输出端口所对应的行元素或者列元素中与该输出端口信息不一致的元素替换为0,形成所述新输出驱动矩阵。

13.进一步,所述将原始网表文件对应的门电路的电路连接关系采用驱动矩阵进行表示包括步骤:步骤1.1,读取原始网表文件;步骤1.2,基于所述原始网表文件创建第一数据结构来存储各个门的各连接端口及其连线,并根据所属于的门在第一数据结构中将所述连接端口及其连线分类成行或列;步骤1.3,分别创建第二数据结构来存储门、电路输入端口以及电路输出端口;步骤1.4,基于第二数据结构的元素遍历第一数据结构的元素,从中找到对应驱动矩阵的元素,生成所述驱动矩阵。

14.进一步,生成所述内部驱动矩阵包括:步骤1.1.1:创建内部驱动矩阵;步骤1.1.2:读取第一数据结构中一个门的所有端口及其连线,并查找该门的一个输出端口及其连线作为当前门的输出端口及其连线;步骤1.1.3:遍历第一数据结构中当前门以外的其他门的所有端口及其连线,找到与当前门的输出端口及其连线为相同连线的其他门的输入端口及其连线,将该其他门的输入端口的信息加入至所述内部驱动矩阵中由当前门的输出端口与该其他门所指向的矩阵元素的取值;步骤1.1.4:继续查找当前门的输出端口及其连线,直至当前门的输出端口匹配完毕,若找到当前门的输出端口及其连线,则返回步骤1.1.3;若当前门的输出端口匹配完毕,则返回步骤1.1.2,直至所有门的输出端口匹配完毕。

15.进一步,生成所述输入驱动矩阵包括:步骤1.2.1:创建所述输入驱动矩阵;步骤1.2.2:读取第二数据结构中的一个电路输入端口作为当前电路输入端口;步骤1.2.3:遍历第一数据结构中所有门的所有端口及其连线,找到与当前电路输入端口信息相同的门的输入端口的连线信息,将所述输入驱动矩阵中由当前电路输入端口与该门所指向的矩阵元素的取值置为该门的输入端口的信息;步骤1.2.4:返回步骤1.2.2读取下一个电路输入端口作为当前电路输入端口,直至所有的电路输入端口读取完毕。

16.进一步,生成所述输出驱动矩阵包括:步骤1.3.1:创建所述输出驱动矩阵;步骤1.3.2:读取第二数据结构中的一个电路输出端口作为当前电路输出端口;步骤1.3.3:遍历第一数据结构中所有门的所有端口及其连线,找到与当前电路输出端口信息相同的门的输出端口的连线信息,将所述输出驱动矩阵中由当前电路输出端口与该门所指向的矩阵元素的取值置为该门的输出端口的信息;步骤1.3.4:返回步骤1.3.2读取下一个电路输出端口作为当前电路输出端口,直至所有的电路输出端口读取完毕。

17.本发明提出的计算机存储介质,用来存储计算机程序,所述计算机程序运行时执行上述技术方案所述的门级网表的处理方法。

18.本发明与现有技术相比,具有以下有益效果:1、驱动矩阵和向量可以完整地表述门电路,无歧义性地表示门内部之间以及与外

部之间的连接关系,且保留所有门电路类型、门电路输入输出端口信息和连接信息、电路模块输入输出端口信息和连接信息。

19.2、电路模块的输入输出端口信息和连接信息用单独的矩阵和向量表述,不影响对内部门电路之间连接复杂度的判断。电路模块的输入、输出端口与内部门电路的连接一般较为简单,如果把这些连接放入内部驱动矩阵中表述,在进行电路的分割等运算时,有可能会影响对内部门电路连接复杂度的判断。

20.3、在进行数学运算的时候,只需把矩阵中的非0元素替换为1即可进行矩阵运算。传统邻接矩阵中可能出现除0、1之外的其他值。

21.4、由于本发明采用了驱动矩阵来表示门电路,使得原始网表文件的运算的效率可以得以提供,并且经由运算后的门电路对应的驱动矩阵,也可以非常便捷方便地得到新的门级网表文件,且该新的门级网表文件的信息非常全面,为之后的仿真提供了详尽的信息。

附图说明

22.下面结合实施例和附图对本发明进行详细说明,其中:图1是一个门电路的示例及对应的有向图及邻接矩阵。

23.图2是图1的门电路对应的内部驱动矩阵的一个实施例。

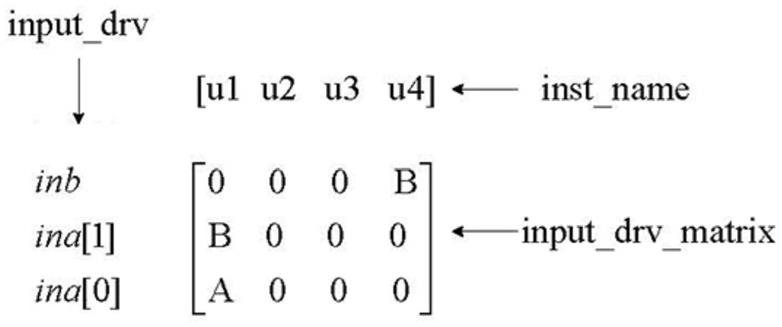

24.图3是图1的门电路对应的输入驱动矩阵的一个实施例。

25.图4是图1的门电路对应的输出驱动矩阵的一个实施例。

26.图5是图1的门电路对应的门与其器件类型的两个向量的实施例。

27.图6是本发明基于驱动生成新网表文件的流程图。

28.图7是本发明生成新输出驱动矩阵的流程图。

29.图8是本发明一实施例的转置输出驱动矩阵。

30.图9是本发明另一实施例中对输出驱动矩阵进行转置、单一化的过程。

31.图10是本发明一实施例的新输出驱动矩阵。

32.图11是本发明一实施例的总输出驱动矩阵。

33.图12是本发明一实施例的内部驱动矩阵与输入驱动矩阵拼接后的结构。

34.图13是本发明的门的输入端口的连线流程图。

35.图14是本发明的门的输出端口的从属关系及对应的连线信息。

36.图15是本发明的门的输出端口的连线流程图。

具体实施方式

37.为了使本发明所要解决的技术问题、技术方案及有益效果更加清楚明白,以下结合附图及实施例,对本发明进行进一步详细说明。应当理解,此处所描述的具体实施例仅用以解释本发明,并不用于限定本发明。

38.由此,本说明书中所指出的一个特征将用于说明本发明的一个实施方式的其中一个特征,而不是暗示本发明的每个实施方式必须具有所说明的特征。此外,应当注意的是本说明书描述了许多特征。尽管某些特征可以组合在一起以示出可能的系统设计,但是这些特征也可用于其他的未明确说明的组合。由此,除非另有说明,所说明的组合并非旨在限制。

39.下面结合附图以及实施例对本发明的原理进行详细说明。

40.如图1所示,本发明给出了一个具体的门电路的示例,下面将基于该示例的电路对本发明进行讲解,由于本发明的门电路分为由原始网表代表的运算之前的门电路,以及经过运算后的门电路,为了便于理解,该示例的电路将会既作为运算之前的门电路,也作为运算后的门电路来讲解本发明的详细技术思路。

41.图1(a)示出了组成门电路的具体器件,每一个器件的输入端口和输出端口以及与外部连接端口(包括电路输入端口、电路输出端口)的连接关系。

42.图1(b)给出了图1(a)所示的门电路的有向图以及对应的邻接矩阵,从该邻接矩阵可以看出,邻接矩阵中不包含输入、输出信息,虽然能够得知顶点u1(门u1,代表类型为haox1的器件)与顶点u2(门u2,代表类型为xxor2x1的器件)之间虽然有两个端口连接,但是具体的连接信息未知,其他顶点之间的关联也是如此,难以看出具体的信息,通过该邻接矩阵所映射得到的有向图也是如此。

43.图1(c)给出了用来表示图1(a)所示的门电路的有向驱动图。在该有向驱动图中,本发明进行了如下定义:顶点,定义每一个顶点代表一个门,即一个顶点就是一个门,顶点u1

‑

顶点u4同时也称为门u1

‑

u4;输入边界顶点,定义每一个所述输入边界顶点代表一个电路输入端口,即一个输入边界顶点就是当前门电路的一个电路输入端口,如当前门电路需要从别的门电路的输出端口输入等;输出边界顶点,定义每一个所述输出边界顶点代表一个电路输出端口,即一个输出边界顶点就是当前门电路的一个电路输出端口,电路输出端口可以是其他门电路的输入端口,也可以是负载端;节点,隶属于对应的顶点,定义每一个节点代表一个门的一个输出端口,即一个节点就是一个门的输出端口;连线,连接输入边界顶点至顶点,以及连接顶点至输出边界顶点,当所述连线的末端连接所述顶点时,所述连线的末端设有用于标注所述顶点的输入端口的信息,如名称。

44.有向驱动图将现有技术中的有向图的顶点进行进一步的细化,使得现有技术当中的顶点在具体展现时,以其输出端口的数量来展现相应的节点,以顶点u1为例,将会展现为两个节点,这两个节点z、o分别是顶点u1的两个输出端口,同时顶点u1的两个输出端口在图中相应的位置绘制其信息(例如名称),如在输入端口连接的连线上绘制对应输入端口的名称a、b。这样使得顶点u1的信息更加丰富。同样的方式去绘制顶点u2

‑

u4,并将它们的输入、输出端口也分别通过节点标注或者是连线标注的方式在图中展示出来。这些顶点的具体类型就是相应门在标准单元库中的器件类型。

45.在该图中与电路输入端口ina[0]、ina[1]连接的顶点u1是一个边界顶点。与电路输入端口inb连接,同时又与电路输出端口outb连接的顶点u4也是一个边界顶点。同样的,与电路输出端口outa连接的顶点u3也是一个边界顶点。定义有向驱动图的输入边界顶点为电路模块网表的输入信号,向量(vector)类型的输入信号中的每一个元素作为一个输入边界顶点,输入边界顶点对于内部电路而言,是输出顶点。也就是说,电路输入端口ina[0]、ina[1]、inb具象化成一个输入边界顶点。

[0046]

定义有向驱动图的输出边界顶点为电路模块网表的输出信号,向量(vector)类型的输出信号中的每一个元素作为一个输出边界顶点。输出边界顶点对于内部电路而言,是其他电路部分的输入点解顶点。也就是说,电路输出端口outa、outb具象化成一个输出边界顶点。

[0047]

通过图1当中的对比,可以看出,有向驱动图很好地对门u1—>门u2、门u2—>门u3的连接进行了区分,并保留了每个门的输入、输出端口的连接信息,以及网表的输入、输出端口的连接信息。

[0048]

上述有向驱动图是基于本发明的一部分生成的,下面详细介绍本发明的门级网表的处理方法。

[0049]

本发明的门级网表的处理方法主要是应用在门级网表所表征的门电路在仿真之前的处理方法,具体包括如下步骤:步骤1,将原始网表文件对应的门电路的电路连接关系采用驱动矩阵进行表示,其中驱动矩阵的行向量和列向量分别从以下两者任选一种:门,所述门所对应的同一类型的连接端口的信息,如名称,当某一个连接端口与一个门相连接时,则驱动矩阵中该门与该连接端口所指向的矩阵元素的取值为该门与该连接端口相连接的端口的信息的集合。由于矩阵的行列即便互换,也并不会影响矩阵所表征的含义,因而本发明对具体是采用门作为驱动矩阵的行向量,采用门所对应的同一类型的连接端口作为驱动矩阵的列向量,还是采用门作为驱动矩阵的列向量,采用门所对应的同一类型的连接端口作为驱动矩阵的行向量,都不会影响驱动矩阵的矩阵元素所表达的含义,因此都包含在本发明的保护范围内。

[0050]

步骤2,基于上述用来表征原始网表文件对应的门电路的三个驱动矩阵对该门电路进行运算,如对门电路进行分割或者分组等,可以得到用来表征运算后的门电路的驱动矩阵,具体的运算过程不是本发明的重点,当需要运算时,将驱动矩阵不为0的元素置1即可进行运算,可以采用现有技术中已有的算法来对门电路进行分割或分组。

[0051]

步骤3,基于每一个运算后的门电路所对应的驱动矩阵,再重建每一个运算后的门电路的新网表文件,每一个运算后的门电路也可以采用上述三个驱动矩阵来表示,当图1所示例的门电路具体为分割后的门电路时,运算后得到的驱动矩阵就如图2至图4所示。

[0052]

在一个具体实施例中,驱动矩阵包括三种驱动矩阵,分别是内部驱动矩阵,输入驱动矩阵和外部驱动矩阵。

[0053]

如图2所示,内部驱动矩阵表征对应门电路的所有门与所有门的所有输出端口之间连接关系,内部驱动矩阵的行、列分别从以下两者任选其一:所有门的所有输出端口,所有门。在一个实施例中,内部驱动矩阵的每一行代表一个门一个输出端口,每一列代表一个门。当一个门的一个输出端口与另一个门的一个或多个输入端口连接,则在内部驱动矩阵中该门的输出端口与另一个门所指向的矩阵元素的取值为另一个顶点的输入端口的名称。例如图2示出的内部驱动矩阵inst_drv_matrix中,向量inst_name为行向量,向量inst_name的每个元素的值为“网表中每一个门被实例化的名称”,行向量的长度为网表中门的个数。向量inst_drv为列向量,其中的元素为网表中每一个门的输出端口,此列向量的长度为网表中所有门的输出端口个数之和,列向量的元素的值为“网表中每一个门被实例化的名称_此门的输出端口名称”,门u1的输出端口z与门u2的输入端口a连接,那么在代表u1_z的行与代表u2的列相交的矩阵元素的取值就是门u2的输入端口名称a。门u2的输出端口z既连

接了门u3的输入端口a,又连接了门u3的输入端口b,则代表u2_z行与代表u3的列相交的矩阵元素的取值就是门u3的两个输入端口名称ab。

[0054]

如图3所示,输入驱动矩阵用来表征对应门电路的所有门与所有电路输入端口之间连接关系,输入驱动矩阵的行列分别为以下两者之一:所有电路输入端口,所有与电路输入端口有连接关系的门,当一个电路输入端口与一个门的输入端口连接,则在该输入驱动矩阵中该电路输入端口与该门所指向的矩阵元素的取值为该门的输入端口的信息。在图2的具体实施例中,定义列向量input_drv,其中的元素为每一个电路输入端口,即每一个输入边界顶点。定义输入驱动矩阵input_drv_matrix的一行表示某一个电路输入端口与所有门的输入端口的连接关系。为了清晰表明所连接的输入端口,定义此行中的每一个元素为每一个连接在此输入边界顶点上的门的输入端口的名称。若此电路输入端口与某一个门没有连接,与此门相交位置的矩阵元素值为0。特别的,若此输入边界顶点与某一个门的两个或者以上的端口相连接,与此门相交位置的矩阵元素值为此门与这一行输入边界顶点所连接的所有输入端口名称的集合。例如电路输入端口inb与门u4的输入端口b连接,那么输入驱动矩阵input_drv_matrix中电路输入端口inb代表的行与门u4代表的列交叉位置的元素的取值为顶点u4的输入端口名称b。

[0055]

如图4所示,输出驱动矩阵用来表征对应门电路的所有门与所有电路输出端口之间连接关系,输出驱动矩阵的行列分别为以下两者之一:所有电路输出接口,所有与电路输出接口有连接关系的门。当一个门的输出端口与一个电路输出端口连接,则该输出驱动矩阵中该门与该电路输出端口所指向的矩阵元素的取值为该门的输出端口的信息。在一个实施例中,定义列向量drv_output,其中的元素为每一个电路输出端口,即每一个输出边界顶点。定义输出驱动矩阵drv_output_matrix的一行表示某一个输出边界顶点与所有门的输出端口的连接关系。为了清晰表明所连接的输出端口,定义此行中的每一个元素为每一个连接在此输出边界顶点上的门的输出端口的名称;若此输出边界顶点与某一个门没有连接,对应此门位置的矩阵元素值为0。例如电路输出端口outa连接门u3的输出端口z,那么输出驱动矩阵outa与门u3所指向的矩阵元素的取值为z。

[0056]

本发明还给出了上述三种驱动矩阵具体生成的方法步骤。

[0057]

步骤1.1,读取原始网表文件;步骤1.2,基于原始网表文件创建第一数据结构来存储各个门的各连接端口及其连线,并根据所属于的门在第一数据结构中将连接端口及其连线分类成行或列;步骤1.3,分别创建第二数据结构来存储门、电路输入端口以及电路输出端口;步骤1.4,基于第二数据结构的元素遍历第一数据结构的元素,从中找到对应驱动矩阵的元素,生成所述驱动矩阵。

[0058]

以python的数据结构为例,在生成任意一个驱动矩阵之前,需要先进行相应的准备工作,即读取原始门级网表的数据。具体的,先读入原始门级网表,再读入门级网表中每一个有效的实例化电路。接着创建列表name_list,元素为每一个门的实例化名称,即门u1至门u4。创建列表ref_list,元素为每一个门在标准单元库中的器件类型。创建二维字典结构sckt_list,此字典中的每一行对应name_list与ref_list中的一个门或者器件类型,此行中的每一个“键——值对”表征了此门的每一个端口的“名称——连线”的连接关系,以门u1的输入端口为例,在该二维字典结构中的键——值对包括z——连线1,该连线1就是顶点

u1的输出端口z与顶点u2的输入端口a之间的连线。还包括a——连线2,连线2就是顶点u1的输入端口a与电路输入端口的连线,该连线2由于是输入边界顶点与边界顶点之间的连线,因而连线2在本实施例中的具体名称为ina[0]。顶点u1相关的键——值对还包括b——连线3、o——连线4,其中b——连线3其实就是b_inb,为顶点u1的输入端口与电路输入端口inb之间的连线。o——连线4就是顶点u1的输出端口o与顶点u2的输入端口b之间的连线。这里所指的列表name_list即向量inst_name,列表ref_list即向量inst_ref。

[0059]

接着介绍各驱动矩阵的详细生成步骤。

[0060]

生成内部驱动矩阵具体过程如下:步骤1.1.1:创建内部驱动矩阵;步骤1.1.2:读取第一数据结构中一个门的所有端口及其连线,并查找该门的一个输出端口及其连线作为当前门的输出端口及其连线;步骤1.1.3:遍历第一数据结构中当前门以外的其他门的所有端口及其连线,找到与当前门的输出端口及其连线为相同连线的其他门的输入端口及其连线,将该其他门的输入端口的信息加入至所述内部驱动矩阵中由当前门的输出端口与该其他门所指向的矩阵元素的取值;步骤1.1.4:继续查找当前门的输出端口及其连线,直至当前门的输出端口匹配完毕,若找到当前门的输出端口及其连线,则返回步骤1.1.3;若当前门的输出端口匹配完毕,则返回步骤1.1.2,直至所有门的输出端口匹配完毕。

[0061]

生成输入驱动矩阵的过程如下:步骤1.2.1:创建所述输入驱动矩阵;步骤1.2.2:读取第二数据结构中的一个电路输入端口作为当前电路输入端口;步骤1.2.3:遍历第一数据结构中所有门的所有端口及其连线,找到与当前电路输入端口名称相同的门的输入端口的连线信息,将输入驱动矩阵中由当前电路输入端口与该门所指向的矩阵元素的取值置为该门的输入端口的信息;步骤1.2.4:返回步骤1.2.2读取下一个电路输入端口作为当前电路输入端口,直至所有的电路输入端口读取完毕。

[0062]

生成输出驱动矩阵的过程如下:步骤1.3.1:创建所述输出驱动矩阵;步骤1.3.2:读取第二数据结构中的一个电路输出端口作为当前电路输出端口;步骤1.3.3:遍历第一数据结构中所有门的所有端口及其连线,找到与当前电路输出端口名称相同的门的输出端口的连线信息,将输出驱动矩阵中由当前电路输出端口与该门所指向的矩阵元素的取值置为该门的输出端口的信息;步骤1.3.4:返回步骤1.3.2读取下一个电路输出端口作为当前电路输出端口,直至所有的电路输出端口读取完毕。

[0063]

接着以图1中示例的门电路作为运算得到的门电路,来介绍重建运算后的门电路的新网表文件的过程,具体流程图请参照图6。

[0064]

步骤3.1,将输出驱动矩阵转化为用于表征对应门电路的所有门的输出端口与所有电路输出端口之间连接关系的新输出驱动矩阵,且以内部驱动矩阵的行向量和列向量为基准,使得所述新输出驱动矩阵与所述内部驱动矩阵用来表征所有门的输出端口的向量均

为行向量,或者均为列向量。

[0065]

如图7所示,生成新输出驱动矩阵具体的包含如下步骤:步骤3.1.1,判断输出驱动矩阵用来表征门的行或列是否与内部驱动矩阵用来表征门的输出端口的行或列均为行向量,或者是否均为列向量,若否,则将输出驱动矩阵进行转置,再继续下一步骤;若是,则直接继续下一步骤。以图2、图3中所示的内部驱动矩阵以及输出驱动矩阵为例,当前输出驱动矩阵drv_output_matrix的行向量是电路输出端口,行向量是所有门,而为了把所有门进一步转化为所有门的输出端口与电路输出端口的关系,就需要对输出驱动矩阵进行转置,形成如图8所示的转置输出驱动矩阵drv_output_transpose_matrix。如果输出驱动矩阵本身就是图8所示的结构,那么就不需要转置,直接继续下一个步骤。

[0066]

步骤3.1.2,根据用来表征所有门的所有输出端口的向量判断一个门是否具有多个输出端口,若一个门具有多个输出端口,则将输出驱动矩阵中该门所对应的行或列进行复制,使得该门所对应的行或列的数量与其输出端口数量一致。

[0067]

在该步骤中,进一步,将转置输出驱动矩阵drv_output_transpose_matrix的行由门向量inst_name索引,改为由门的输出端口向量inst_drv索引。如果门的输出端口向量inst_drv中有多个输出端口从属于同一个门(在本实施例中即最后一个“_”前的字段相同),则把转置输出驱动矩阵drv_output_transpose_matrix矩阵中对应于这个门的行复制为n行,以对应这个门的n个输出端口。

[0068]

如果被复制的这一行有2个或者2个以上的元素非零,说明这一行所对应的门有两个或者两个以上的输出端口连接到了电路输出端口上,在改为由门的输出端口向量inst_drv索引后,需要把转置输出驱动矩阵drv_output_transpose_matrix矩阵的内容单一化。在复制后的行中,仅保留与门的输出端口向量inst_drv所在的当前行的输出端口名称(最后一个“_”后的字段)一致的元素,其他元素改为0。例如,设某电路u1的输出z1、z2连接到模块的输出端口,则图9中的转置输出驱动矩阵drv_output_transpose_matrix的复制和单一化过程如图中所示。

[0069]

步骤3.1.3,将复制后的输出驱动矩阵中的行向量或列向量中的门分别采用该门的各个输出端口进行替换。

[0070]

步骤3.1.4,将替换后的所述输出驱动矩阵中每一个门的输出端口所对应的行元素或者列元素中与该输出端口名称不一致的元素替换为0,形成所述新输出驱动矩阵。按照图9所示的方法,将图8的转置输出驱动矩阵drv_output_transpose_matrix的行由门向量inst_name索引改为由门的输出端口向量inst_drv索引,并根据门的输出端口向量inst_drv对相应的行进行复制、单一化以后,得到最终的新输出驱动矩阵inst_drv_output_matrix矩阵,如图10所示。

[0071]

步骤3.2,基于相同的行向量或者相同的列向量,将所述内部驱动矩阵与所述新输出驱动矩阵拼接成用来表征所有门的输出端口与所有门及电路输出端口之间连接关系的总输出驱动矩阵。

[0072]

按照verilog hdl结构化描述的规则,对于门的输出端口到其他门的输入端口的连线信息,可以任意命名,没有限制;而对于门的输出端口到模块输出端口的连线信息,则必须是模块输出端口的名称,才能表征其连接关系。输出驱动矩阵drv_out_matrix经过转

置、复制与单一化之后,生成的新输出驱动矩阵inst_drv_output_matrix的行数与内部驱动矩阵inst_drv_matrix的行数一致。将内部驱动矩阵inst_drv_matrix与新输出驱动矩阵inst_drv_output_matrix矩阵按照一行两列的方式拼接为一个大矩阵,即可以得到总输出驱动矩阵inst_drv_concat,如图11所示。

[0073]

步骤3.3,根据总输出驱动矩阵的矩阵元素的取值得到每一个门的输出端口的连线信息。

[0074]

拼接后总输出驱动矩阵inst_drv_concat的一行,表示一个门的一个输出端口在其他门的输入、电路输出端口上的所有连接关系。当此行中新输出驱动矩阵inst_drv_output_matrix的部分为全零(元素取值全为零)时,表示门的输出端口没有连接到电路输出端口,此时连接门的输出端口的连线信息可以采用任意命名。设可以命名为“net_”+ inst_drv当前行元素,例如,对于图11中门的输出端口向量inst_drv中的u1_z,连线信息可以为“net_u1_z”。

[0075]

当此行中新输出驱动矩阵inst_drv_output_matrix的部分有非零元素时(由于经过单一化操作,此处有且仅有一个非零元素),必须以电路输出端口向量drv_output中此元素所在列对应的元素给连线命名,即以连接在此门的此输出端口上的、模块的输出端口名称作为连线信息。对于图11中的门的输出端口u3_z,则连线信息必须为“outa”;对于门的输出端口u4_z,连线信息必须为“outb”。

[0076]

每一行生成一个连线的信息,所有行生成连线信息向量inst_drv_wire。确定门的输出端口的连线信息。

[0077]

步骤3.4,创建待连线的门列表,本实施例中,按照门向量inst_name的长度,创建待连线门列表,即门u1

‑

门u4。

[0078]

步骤3.5,将内部驱动矩阵用来表征所有门的输出端口的向量的元素采用该输出端口对应的连线名称进行替换,得到新内部驱动矩阵;根据生成连线信息向量inst_drv_wire的生成方法,可以使用生成连线信息向量inst_drv_wire替代电路输出端口向量inst_drv对内部驱动矩阵inst_drv_matrix的行进行索引。门向量inst_name、电路输入端口向量input_drv、输入驱动矩阵input_drv_matrix表征了门电路模块的输入端口与内部电路的连接关系。如图3所示。

[0079]

步骤3.6,基于相同的行向量或者相同的列向量,将所述新内部驱动矩阵与输入驱动矩阵拼接成输入输出驱动矩阵;在本实施例中,内部驱动矩阵inst_drv_matrix与输入驱动矩阵input_drv_matrix的行列对应关系一致,即矩阵中的每一列表征的都是属于同一个门的连接关系,矩阵的每一行表征的都是同一个驱动端与所有门的连接关系。使用连线信息向量inst_drv_wire替代门向量inst_drv后,两个矩阵的每一行表征的都是同一个名称的连线(电路输入端口的信息也作为连线名称)与所有门的连接关系。两个矩阵可以按照两行一列的方式拼接在一起,形成一个大矩阵,如图12所示。

[0080]

步骤3.7,基于输入输出驱动矩阵生成每一个门及其对应的输入端口连线、输出端口连线的信息。

[0081]

拼接后矩阵的每一行,表明了图12中左侧已被命名的连线连接在每一个门的哪个输入端上。依次读入拼接后大矩阵的每一行,按照列的顺序,给待连线门列表中的每一个门

添加输入端口和连线。如果某列的元素是“0”,表明当前门没有连线,不用添加;如果某列元素非零,则添加“.端口信心(连线信息)”,“端口信息”是此列的非0元素值(即元素的取值),“连线信息”是连线信息向量inst_drv_wire或者电路输入端口向量input_drv中当前行的元素值。如果某列元素的取值包含两个或者两个以上的端口信息,如多个端口名称,则把端口名称拆分为单个端口名称,分别添加在这个门上。本实施例中最终得到的连线结果如表1所示。上述给门的输入端口连线的过程如图13所示。

[0082]

表1 图12中矩阵的连线结果门的输出端口向量inst_drv中每一个元素最后一个“_”前的字段表明所属门的信息,本实施例中为门的名称,“_”后的字段表明此门的当前输出端口的名称。连线信息向量inst_drv_wire中对应位置的元素表明连接在此输出端口上连线的信息,如图14所示。

[0083]

把从属于同一个门的输出端口以及连线以“.端口信息(连线名称)”的方式依次添加到待连线门列表的同一个门中。图14所示向量的连线结果如表2所示。给门的输出端口连线的过程如图15所示。

[0084]

表2 图14所示向量的连线结果步骤3.8,为每一个门添加类型信息及格式化信息。根据图5所示的向量排列规则,读入门向量inst_name和类型向量inst_ref,在待连线门列表中的每一个门的连线前面插入门的名称、门的类型。读入电路输入端口向量input_drv、电路输出端口向量drv_output、连线信息向量inst_drv_wire,添加门电路模块所需的电路输入、输出端口名称、类型声明以及内部连线的声明。添加module、endmodule等关键字。

[0085]

步骤3.9,最后将所有门及其对应的信息输出到新网表文件。

[0086]

本发明还保护一种计算机存储介质,用来存储计算机程序,该计算机程序运行时执行上述技术方案中的网表的处理方法。

[0087]

在上面驱动矩阵的生成过程中,所有驱动矩阵的元素的取值在创建时均为空,当两个顶点的对应连接端口之间无连接关系时,将对应的元素取值置为0,如果有连接关系,则将相应的连接端口的名称加入到对应的元素的取值中。

[0088]

以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1