用于片上系统的功耗控制系统、片上系统和计算装置的制作方法

1.本公开涉及芯片领域,具体而言,涉及用于片上系统的功耗控制系统、片上系统和计算装置。

背景技术:

2.随着集成电路工艺不断缩小,控制芯片成本和功耗成为各大芯片厂商的重要目标,avfs(adaptive voltage frequency scaling,自适应电压与频率调节)是业界高端cpu,gpu,手机处理器等芯片的常规配置。avfs是一种降低功耗的技术,它通过传感器实时获取检测数据,然后根据检测数据确定芯片系统的时钟频率和供电电压。工艺偏差是一种采用工艺传感器获得的检测数据,用于表征当前工艺、当前温度和当前电压下的芯片性能偏差。

3.为了表征芯片性能偏差,片上系统内部通常在多个不同位置设置多个工艺传感器,然后采集多个工艺偏差数据,并综合多个工艺偏差数据得到最终结果。然而发明人发现,这样得到的工艺偏差数据受到例如传感器的排布位置和采集顺序等多种因素的影响,因此并不能准确反映系统的当前状况。

技术实现要素:

4.有鉴于此,本公开的目的是提供用于片上系统的功耗控制系统、片上系统和计算装置,以解决现有技术中存在的技术问题。

5.第一方面,本公开实施例提供一种用于片上系统的功耗控制系统,包括:

6.多个工艺传感器;

7.功耗控制器,包括:

8.链控制器,用于从所述多个工艺传感器分别收集至少一个计数值,并针对所述多个工艺传感器的计数值进行加权计算以确定所述片上系统在第一工作条件下的工艺偏差;

9.电压和频率计算单元,用于根据所述工艺偏差确定所述片上系统要调节到的目标频率和/或目标电压;

10.调压信号生成单元,用于根据所述目标电压生成用于调节所述片上系统的供电电压的调压信号,

11.变频控制单元,用于根据所述目标频率生成用于调节所述片上系统的时钟频率的调频信号。

12.可选地,所述多个工艺传感器首尾相连,并与所述链控制器组成单向数据传输路径。

13.可选地,所述链控制器根据每个工艺传感器的排布位置和采集顺序配置其对应的权重,以进行所述加权计算。

14.可选地,所述工艺传感器包括:

15.至少一个震荡环,每个震荡环由同一种类型的多个反相器首尾连接成环形并与一

计数单元耦接,所述计数单元用于统计所述多个反相器在固定时间内的反转次数,并将其对应的震荡环在单位时间内的反转次数作为一个计数值输出,

16.所述链控制器为所述至少一个震荡环分别配置一权重,将每个工艺传感器包含的所述至少一个震荡环输出的至少一个计数值进行加权计算,以得到该工艺传感器的计数值。

17.可选地,所述工艺传感器还包括:网环,包括唯一的反相器和长度大于设定阈值的连线,用于输出一计数值,则所述链控制器将每个工艺传感器包含的至少一个震荡环和所述网环输出的计数值进行加权计算,以得到该工艺传感器的计数值。

18.可选地,所述链控制器为不同类型的震荡环配置不同的权重,所述震荡环的类型由组成该震荡环的反相器的类型决定。

19.第二方面,本公开实施例提供一种调节电压和频率的方法,包括:

20.从每个工艺传感器收集至少一个计数值;

21.对多个所述工艺传感器的计数值进行加权计算,以得到系统在第一工作条件下的工艺偏差;

22.基于所述工艺偏差确定系统要调节到的目标频率和/或目标电压;以及

23.将系统的时钟频率和/或供电电压分别调节到所述目标频率和/或所述目标电压。

24.可选地,所述根据多个工艺传感器的计数值确定系统在当前条件下的工艺偏差包括:

25.为每个工艺传感器配置一权重;以及

26.对多个所述工艺传感器的计数值进行加权计算,以得到系统在当前条件下的工艺偏差。

27.第三方面,本公开实施例提供一种片上系统,包括:

28.处理单元;

29.调频调压控制器,包括上述任一项所述的功耗控制系统;

30.片上总线,用于耦接所述处理单元、所述双轨存储器和所述功耗控制系统。

31.第四方面,本公开实施例提供一种计算装置,包括:

32.上述的片上系统;

33.片外总线;

34.通过所述片外总线与所述片上系统耦接的存储设备;

35.与所述功耗控制器耦接的电源管理电路。

36.根据本公开实施例,通过链控制器从每个工艺传感器收集至少一个计数值,并根据多个工艺传感器的计数值进行加权计算以确定系统在当前工作条件下的工艺偏差,这样确定的工艺偏差更加准确,从而基于该工艺偏差计算出的目标频率和目标电压也更适应当前工作条件。

附图说明

37.通过参考以下附图对本公开实施例的描述,本公开的上述以及其它目的、特征和优点将更为清楚,在附图中:

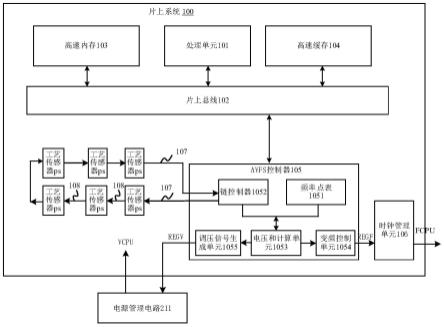

38.图1是本公开一实施例所应用的片上系统的结构示意图;

39.图2是本公开另一实施例所应用的片上系统的结构示意图;

40.图3是本公开一实施例构建的工艺传感器的结构图;

41.图4是本公开另一实施例提供的工艺传感器的结构图;

42.图5是本公开一实施例提供的一种调节电压和频率的方法的流程图;

43.图6是本公开实施例所应用的通用计算机系统的结构示意图;

44.图7是本公开实施例所应用的嵌入式系统的结构示意图。

具体实施方式

45.以下基于实施例对本公开进行描述,但是本公开并不仅仅限于这些实施例。在下文对本公开的细节描述中,详尽描述了一些特定的细节部分。对本领域技术人员来说没有这些细节部分的描述也可以完全理解本公开。为了避免混淆本公开的实质,公知的方法、过程、流程没有详细叙述。另外附图不一定是按比例绘制的。

46.片上系统

47.图1是本公开一实施例所应用的片上系统100的结构示意图。

48.参考图上所示,处理单元101和高速内存103、高速缓存104耦接到片上总线102。片上总线102例如为axi总线。axi总线是arm公司提出的amba(advanced microcontroller bus architecture)3.0及以上协议中最重要的部分,它是面向于高性能、高带宽、低延迟的片内总线。aix总线将地址/控制和数据相位分离,支持不对齐的数据传输,同时支持突发传输和乱序传输,因此满足了超高性能和复杂的片上系统设计的需求。处理单元101可以为任意具有不同电路结构的处理单元,例如为微处理器、微控制器、数字处理单元(dsp)、处理器核、图形处理单元(gpu)、神经网络处理单元,等等。不同于设置在片上系统中的高速内存103,位于片外的存储器可以容量更大但速度较慢、成本较低。在一些实现中,高速内存103和104可以为静态随机存取存储器(sram),而片外的存储器为dram(动态随机存取存储器)和闪存(flash)存储器。

49.如图上所示,avfs控制器105耦接到片上总线102上。avfs控制器105还分别与时钟管理单元106、位于片外的电源管理电路211耦接。

50.片上总线102还包括未被示出的接口电路,通过接口电路与片外的外部设备耦接。外部设备例如可以为文字、音频和视频的输入/输出设备和各种存储器。处理单元101可通过接口电路访问片外的外部设备。

51.片上系统100还可内嵌基本软件和应用程序(未示出),基本软件例如为片上系统的操作系统,应用程序是一些专有目的的程序。另有其他的应用程序可以存储在片上系统100之外的存储器中,这些应用程序可以通过接口电路拷贝到片上系统100中的高速内存104中,或者通过接口电路访问片上系统100中的资源。

52.处理单元101负责读取各种指令,并对指令进行译码和执行。在本实施例中,处理单元101经由片上总线102向avfs控制器105发送调频调压指令。

53.avfs控制器105执行调频调压操作。在执行调频调压操作时,avfs控制器105生成调频信号regf和调压信号regv,将调频信号regf发送给时钟管理单元106,将调压信号regv发送给电源管理电路211,由时钟管理单元106调节时钟频率fcpu,由电源管理电路211调节向片上系统100提供的供电电压vcpu。

54.如图上所示,avfs控制器105包括用于存储频率点表1051的寄存器组、链控制器1052、电压和频率计算单元1053、变频控制单元1054和调压信号生成单元1055。

55.频率点表1051包括多个频率,该多个频率通常经过验证,能够使系统正常工作。频率点表1051通常在系统上电启动后被加载到寄存器组中,在系统上电启动时,处理单元101或其他部件发送频率配置指令,avfs控制器105根据频率配置指令将频率点表1051加载到寄存器组中。

56.链控制器1052与多个工艺传感器ps耦接,用于从多个工艺传感器ps实时采集多个计数值并根据多个计数值进行加权计算以确定工艺偏差。

57.电压和频率计算单元1053根据从链控制器1052接收到的工艺偏差数据计算系统要调节到的目标频率和目标电压,并将目标频率和目标电压分别提供给变频控制单元1054和调压信号生成单元1055。调压信号生成单元1055根据目标电压生成调压信号regv,变频控制单元1054根据目标频率生成调频信号regf。可选地,avfs控制器105还可以包括告警单元(未示出),用于对异常情况进行告警。

58.可选地,电压和频率计算单元1053还利用频率点表1051调整目标频率,例如,当目标频率超过频率点表内的最大频率或者最小频率,则认为该目标频率不合适,或者,当目标频率不与频率点表内的任意一个频率相符时,则认为该目标频率不合适,在认定目标频率不合适的情况下,可从频率点表中得到与目标频率最接近的一个频率,将目标频率赋值给目标频率。

59.如图上所示,六个工艺传感器ps与链控制器1052首尾相连,组成单向的数据传输路径。数据传输路径的起点和终点都是链控制器1052。图上使用箭头表示工艺传感器的物理链路。这种串行物理链路有利于节约系统100上的布线空间。需要说明的是,通常符合边界扫描协议(例如ieee 1149.1)的芯片中都包含扫描链(scan chains),它主要用于帮助测试人员从集成电路的外部控制和观测集成电路内部的信号变化。在本实施例中,则可以利用工艺传感器ps内部的扫描链串连多个工艺传感器ps。

60.链控制器1052按照数据传输路径向多个工艺传感器ps发送数据请求并从多个工艺传感器ps接收计数值,并根据多个工艺传感器ps得到各个工艺传感器ps的计数值。

61.图2是另一个实施例的片上系统的结构示意图。在本实施例中,电源管理电路212设置在片上系统200的内部。

62.图3是一示例性的工艺传感器ps的结构图。如图上所示,该工艺传感器ps包括lvt震荡环301、rvt震荡环302、hvt震荡环303、与lvt震荡环301耦接的计算单元305、与rvt震荡环302耦接的计数单元306、与hvt震荡环303耦接的计数单元307。

63.lvt震荡环301是由奇数个lvt反相器连成的环路。rvt震荡环302是奇数个rvt反相器连成的环路。hvt震荡器303是由奇数个hvt反相器连成的环路。可通过开关控制信号将多个同一种类型的反相器连接成环路。奇数个反相器能够保证一个信号经过震荡环能够以相反的信号返回来,例如,lvt震荡环301的起始值为0,然后经过5个lvt反相器后,以1返回来,信号回来的时间是奇数个反相器的延迟时间之和,由此产生周期性信号振荡。

64.计数单元305-307各自计算出当前条件下与其耦接的震荡环在单位时间内的计数值。具体地,lvt反相器、rvt反相器和hvt反相器分别由lvt、rvt和hvt标准单元库中的反相器单元构成。根据标准单元库的设计,不同类型的反相器均具有一个时间(timing)参数,该

参数包括不同温度、不同工艺偏差、不同电压下的反相器延迟时间,根据该参数确定在当前条件下三种类型的反相器各自的延迟时间,然后将反相器延迟时间乘以反相器个数所得的乘积就是该振荡环的振荡周期时间,再用在固定时间内的计数值除以震荡环的震荡周期,从而得到每个震荡环在当前条件下单位时间内的计数值。

65.图4是一示例性的工艺传感器ps的结构图。如图上所示,该工艺传感器ps包括lvt震荡环311、rvt震荡环312、hvt震荡环313、网环314、与lvt震荡环311耦接的计算单元315、与rvt震荡环312耦接的计数单元316、与hvt震荡环313耦接的计数单元317。

66.与图3的不同之处在于,工艺传感器ps增加了网环314和与网环314耦接的计数单元318。从图上可以看出,网环314只包含一个反相器,该反相器为lvt反相器、rvt反相器、hvt反相器中的一种,网环的连线很长,由于连线的网络延迟远远大于反相器的网络延迟,因此网环反映的网络延时基本上是连线的网络延迟。这里网环314还包括3个反相器,也能够满足要求。

67.将图3-4与图2结合能够理解,由于多个工艺传感器ps组成了单向数据传输路径,因此链控制器1052可串行定期地向每个工艺传感器ps发送数据读取请求,每个工艺传感器ps收到请求之后,获取其内部的每个震荡环上产生的计数值,并将每个震荡环上的计数值经由数据传输路径传送给链控制器1052。

68.链控制器1052获得计数值之后,作为一种实施方式,在未包含网环的情况下,链控制器1052通过以下步骤计算得到系统在当前条件下的工艺偏差:首先将每个工艺传感器ps的各个震荡环的计数值进行加权求和再平均,得到每个工艺传感器ps的加权平均计数值,然后将多个传感器的加权平均计数值再进行一次加权求和再平均,得到系统在当前条件下的工艺偏差。作为另一种实施方式,链控制器1052还可以通过以下步骤得到系统在当前条件下的工艺偏差:首先将每个工艺传感器ps的各个震荡环的计数值进行求和再平均,得到每个工艺传感器ps的平均计数值,然后将多个传感器的平均计数值再进行一次加权求和再平均,得到系统在当前条件下的工艺偏差。

69.应理解,当对某个工艺传感器中的各个震荡环的计数值进行加权计算时,首先要为各个震荡环分别配置一权重,可选地,每个震荡环的权重由组成该震荡环的反相器的类型决定。同理,当对多个工艺传感器的计数值进行加权计算时,首先要为每个工艺传感器分别配置一权重。可选地,每个工艺传感器的权重可根据它在单向数据传输路径的位置(或者序号)确定。

70.加权计算的公式如下所示:假设工艺传感器1的权重为w0,其计数值为count0,工艺传感器2的权重为w1,其计数值为count1,工艺传感器3的权重为w2,其计数值为count2。则综合三个工艺传感器的计数值得到的工艺偏差为:

71.counter=(counter0*w0+counter1*w1+counter2*w2)/3公式(1)

72.同理,当对多个震荡环输出的计数值进行加权计算时,其公式与公式(1)类似。

73.在包含网环的情况下,链控制器1052可基于网环得到计数值对各个震荡环进行处理,例如计数单元315、计数单元316、计数单元317和计数单元318分别加上计数单元318的计数值,作为每个震荡环重新计算的计数值,然后再采用以下步骤得到系统在当前条件下的工艺偏差:首先将每个工艺传感器ps每个震荡环重新计算的计数值进行加权求和再平均,得到每个工艺传感器ps的加权平均计数值,然后将多个传感器的加权平均计数值再进

行一次加权求和再平均,得到系统在当前条件下的工艺偏差。上文的另一个实施例(不包含网环的工艺传感器中使用的另一实施例)也可以用在这里,这里不再重复。

74.应理解,本公开可根据具体情况调整工艺传感器内部的震荡环,例如,在每个工艺传感器中只设置lvt震荡环301和rvt震荡环302,或者只设置lvt震荡环301和网环304。此外,反相器不仅有lvt反相器、rvt反相器、hvt反相器,还有其他类型的反相器,例如ulvt。

75.由于比较而言,hvt反相器的速度最高,延迟最小,但同时功耗最大。lvt反相器的速度最小,延迟最大,但同时功耗最小。rvt的速度、延迟和功耗都居于两者之间。因此也可以根据速度、延迟和功耗构建工艺传感器。

76.根据上述实施例中,通过链控制器从每个工艺传感器收集至少一个计数值,并对多个工艺传感器的计数值进行加权计算,以确定系统在当前条件下的工艺偏差,这样表征的工艺偏差更加合理,从而基于工艺偏差确定的目标频率和目标电压也更适应当前状况。

77.此外,权重配置具有灵活性,例如权重可基于每个片上系统当前的工作条件(例如不同电压、不同温度、工艺传感器的不同排布方式和采集顺序)确定。

78.作为一个实施例,当多个工艺传感器与链控制器组成单向数据传输路径时,由于位置信息影响到输出的计数值,因此可根据每个工艺传感器在单向数据传输路径中的位置(或者序号)配置其权重。此外,每个工艺传感器或每个振荡器的权重还可通过多次实验得到。

79.本公开实施例的用于片上系统的功耗控制系统

80.基于上述的实施例,本公开提供一种用于片上系统的功耗控制系统。参考图1或2所示,该功耗控制系统包括:多个工艺传感器ps,功耗控制器,该功耗控制器包括:链控制器1052、电压和频率计算单元1053、调压信号生成单元1055和变频控制单元1054。

81.链控制器1052与多个工艺传感器ps耦接,用于从多个工艺传感器ps分别收集至少一个计数值,并针对多个工艺传感器的计数值进行加权计算以确定片上系统在当前工作条件下的工艺偏差。

82.电压和频率计算单元1053用于根据工艺偏差确定片上系统要调节到的目标频率和/或目标电压。

83.调压信号生成单元1055用于根据目标电压生成用于调节片上系统1的供电电压的调压信号。

84.变频控制单元1054用于根据目标频率生成用于调节片上系统的时钟频率的调频信号。

85.本实施例提供的功耗控制器可用于片上系统,也可用于其他计算机环境。该功耗控制器通过加权计算更加准确的工艺偏差,从而基于该工艺偏差计算出的目标频率和目标电压也更适应当前工作条件。关于该功耗控制器的各个部件的更详细的描述,可参考上文中的实施例,这里不在重复描述。

86.本公开实施例的调节频率和电压的方法

87.图5示出了本公开实施例的一种调节频率和电压的方法的流程图,包括以下步骤。

88.在步骤s01中,从每个工艺传感器采集至少一个计数值。

89.在步骤s02中,对多个工艺传感器的计数值进行加权计算,以确定系统在当前条件下的工艺偏差。每个工艺传感器输出至少一个用于表征当前处理器性能偏差的计数值。综

合多个这样的计数值,从而确定系统在当前条件下的工艺偏差。例如,首先将每个工艺传感器中的各个震荡环的计数值进行加权求和再平均,得到每个工艺传感器的加权平均计数值,然后将多个传感器的加权平均计数值再进行一次加权求和再平均,得到系统在当前条件下的工艺偏差。

90.在步骤s03中,基于工艺偏差确定系统要调节到的目标频率和目标电压。虽然工艺偏差只是影响系统要调节到的目标频率和目标电压的一个因素,但是将工艺偏差与其他因素(例如温度)结合可计算出目标频率和目标电压。此外,计算出初步的目标频率和目标电压之后,还可以基于图1或图2中的频率点表1051的各个频率对其进行调整,同时如果从处理单元101接收到的调频调压指令中指定了希望系统调节到的目标频率,可结合该指定,确定最终系统要调节到的目标频率,并根据最终系统要调节到的目标频率,确定最终系统要调节到的目标电压。

91.在步骤s04中,将系统的处理频率和供电电压分别调节到目标频率和目标电压。

92.在一些实施例中,根据多个工艺传感器的计数值确定系统在当前条件下的工艺偏差包括以下步骤:首先为每个工艺传感器配置一权重,然后对多个工艺传感器的计数值进行加权计算,以得到系统在当前条件下的工艺偏差。

93.在一些实施例中,通过以下步骤获得每个工艺传感器的计数值:首先为每个工艺传感器中的每个震荡环配置一权重,然后对每个工艺传感器中的至少一个震荡环的计数值进行加权计算,以得到每个工艺传感器在当前条件下的计数值。

94.在一些实施例中,根据每个工艺传感器在单向数据传输路径中的位置配置该工艺传感器的权重。

95.在一些实施例中,根据不同类型的震荡环配置不同的权重,震荡环的类型由组成该震荡环的反相器的类型决定。

96.片上系统的具体应用

97.图6是本公开实施例所应用的通用计算机系统的结构示意图。如图上所示,计算机系统600可以包括一个或多个处理器12,以及存储器14。其中,上述实施例提供的片上系统可用作处理器12。

98.计算机系统600中的存储器14可以主存储器(简称为主存或内存)。用于存储由数据信号表示的指令信息和/或数据信息,例如存放处理器12提供的数据(例如为运算结果),也可以用于实现处理器12与外部存储设备16(或称为辅助存储器或外部存储器)之间的数据交换。

99.在一些情形下,处理器12可能需要访问存储器14,以获取存储器14中的数据或对存储器14中的数据进行修改。由于存储器14的访问速度较慢,为了缓解处理器12与存储器14之间的速度差距,计算机系统600还包括与总线11耦合的高速缓冲存储器18,高速缓冲存储器18用于对存储器14中的一些可能会被反复调用的程序数据或者报文数据等数据进行缓存。高速缓冲存储器18例如由静态随机存储器(static random access memory,简称为sram)等类型的存储装置实现。高速缓冲存储器18可以为多级结构,例如具有一级缓存(l1 cache)、二级缓存(l2 cache)和三级缓存(l3 cache)的三级缓存结构,也可以是三级以上的缓存结构或其他类型缓存结构。在一些实施例中,高速缓冲存储器18的一部分(例如一级缓存,或一级缓存和二级缓存)可以集成在处理器12内部或与处理器12集成于同一片上系

统中。

100.基于此,处理器12可以包括指令执行单元121、内存管理单元122等部分。指令执行单元121在执行一些需要修改内存的指令时发起写访问请求,该写访问请求指定了需要写入内存中的写入数据和相应的物理地址;内存管理单元122用于将这些指令指定的虚拟地址转译为该虚拟地址映射的物理地址,写访问请求指定的物理地址与相应指令指定的物理地址可以一致。

101.存储器14和高速缓冲存储器18之间的信息交互通常按块来组织。在一些实施例中,高速缓冲存储器18和存储器14可以按照相同的空间尺寸被划分成数据块,数据块可以作为高速缓冲存储器18和存储器14之间的数据交换的最小单位(包括预设长度的一个或多个数据)。为了表述简洁清晰,下面将高速缓冲存储器18中的各个数据块简称为缓存块(可以称为cacheline或高速缓存线),且不同的缓存块具有不同的缓存块地址;将存储器14中的各个数据块简称为内存块,且不同的内存块具有不同的内存块地址。缓存块地址例如包括用于定位数据块的物理地址标签。

102.由于受到空间和资源的限制,高速缓冲存储器18无法对存储器14中的全部内容都进行缓存,即高速缓冲存储器18的存储容量通常小于存储器14,高速缓冲存储器18提供的各个缓存块地址无法对应存储器14提供的全部内存块地址。处理器12在需要访问内存时,首先经总线11访问高速缓冲存储器18,以判断所要访问的内容是否已被存储于高速缓冲存储器18中,如果是,则高速缓冲存储器18命中,此时处理器12直接从高速缓冲存储器18中调用所要访问的内容;如果处理器12需要访问的内容不在高速缓冲存储器18中,则高速缓冲存储器18,处理器12需要经总线11访问存储器14,以在存储器14中查找相应的信息。因为高速缓冲存储器18的存取速率非常快,因此当高速缓冲存储器18命中时,处理器12的效率可以显著提高,进而也使整个计算机系统600的性能和效率得以提升。

103.此外,计算机系统600还可以包括存储设备16、显示设备13、音频设备19、鼠标/键盘15等输入/输出设备。存储设备16例如是通过相应接口与总线11耦合的硬盘、光盘以及闪存等用于信息存取的设备。显示设备13例如经相应的显卡与总线11耦合,用于根据总线11提供的显示信号进行显示。

104.计算机系统600通常还包括通信设备17,因此可以通过各种方式与网络或其他设备通信。通信设备17例如可以包括一种或多种通信模块,作为示例,通信设备17可以包括适用于特定的无线通信协议的无线通信模块。例如,通信设备17可以包括wlan模块,用于实现符合电气和电子工程师协会(ieee)制定的602.11标准的wi-fitm通信;通信设备17也可以包括wwan模块,用于实现符合蜂窝或其他无线广域协议的无线广域通信;通信设备17还可以包括蓝牙模块等采用其它协议的通信模块,或其它自定义类型的通信模块;通信设备17也可以是用于串行传输数据的端口。

105.当然,不同的计算机系统根据主板、操作系统和指令集架构的不同,其结构也可能有所变化。例如目前很多计算机系统设置有连接在总线11和各个输入/输出设备之间的输入/输出控制中心,且该输入/输出控制中心可以集成于处理器12之内或独立于处理器12。

106.图7是本公开实施例所应用的嵌入式系统的结构图。上述实施例提供的片上系统可用作处理器701。

107.虽然嵌入式系统在硬件结构上与计算机系统具有高度相似性,但是嵌入式系统应

用上的特点致使嵌入式系统在硬件的组成和实现形式上与通用计算机系统又有较大区别。

108.首先,为满足嵌入式系统700在速度、体积和功耗上的要求,操作系统、应用软件、特殊数据等需要长期保存的数据,通常不使用磁盘这类具有大容量且速度较慢的存储介质,而大多使用随机存储器702或闪存(flash memory)703。

109.另外,在嵌入式系统700中,需要a/d(模拟/数字转换)接口705和串行接口706,用于测控的需要,这在通用计算机中用得很少。a/d接口705主要完成测试中所需要的模拟信号到数字信号的转换、和数字信号到模拟信号的转换。嵌入式系统700应用于工业生产时经常需要测试。由于单片机产生的是数字信号,在测试时需要转换成模拟信号用于测试,因此,与通用计算机不同,需要a/d(模拟/数字转换)接口705完成相关转换。另外,工业中经常需要多个嵌入式系统串接在一起,完成相关功能,因此需要用于将多个嵌入式系统串联的串行接口706,而在通用计算机中则大多不需要。

110.另外,嵌入式系统700作为一个基本的处理单元,常常在工业设计中需要将多个嵌入式系统700联成网络,因此需要将嵌入式系统700联入网络的网络接口707。这在通用计算机中大多也不需要。此外,根据实际应用和规模的不同,有些嵌入式系统700要采用外部总线704。随着嵌入式系统700应用领域的迅速扩张,嵌入式系统700越来越趋于个性化,根据自身特点采用总线的种类也越来越多。另外,为了对嵌入式处理器701内部电路进行测试,处理器芯片普遍采用了边界扫描测试技术。为了适应该测试,采用了调试接口708。

111.随着超大规模集成电路(very large scale integration)和半导体工艺的迅速发展,上述的嵌入式系统的部分或者全部可实现在一个硅片上,即为嵌入式片上系统(soc)。

112.本公开实施例的商业价值

113.本公开实施例提供的片上系统,通过加权计算得到工艺偏差,并基于工艺偏差确定系统要调节到的目标频率和目标电压,由此目标频率和目标电压更能反映当前状况。这样的片上系统可用于形成多种场景使用的计算装置,例如数据中心数量庞大的云服务器;再例如,日常生活中使用的电子设备,包括诸如笔记本和手机等终端设备以及某些消费型电子产品。由此可见,本公开实施例的片上系统以及由该片上系统构建的计算装置在具有实用价值的基础上,具备了商业价值和经济价值。

114.本领域的技术人员能够理解,本公开可以实现为系统、方法和计算机程序产品。因此,本公开可以具体实现为以下形式,即完全的硬件、完全的软件(包括固件、驻留软件、微代码),还可以实现为软件和硬件结合的形式。此外,在一些实施例中,本公开还可以实现为一个或多个计算机可读介质中的计算机程序产品的形式,该计算机可读介质中包含计算机可读的程序代码。

115.可以采用一个或多个计算机可读介质的任意组合。计算机可读介质可以是计算机可读信号介质或者计算机可读存储介质。计算机可读存储介质例如但不限于为电、磁、光、电磁、红外线或半导体的系统、装置或器件,或其他任意以上的组合。计算机可读存储介质的更具体的例子包括:具体一个或多个导线的电连接,便携式计算机磁盘、硬盘、随机存取存储器(ram)、只读存储器(rom)、可擦除可编程只读存储器(eprom或者闪存)、光纤、便携式紧凑磁盘只读存储器(cd-rom)、光存储器、磁存储器或者上述任意合适的组合。在本文中,计算机可读的存储介质可以是任意包含或存储程序的有形介质,该程序可以被处理单元、

装置或者器件使用,或者与其结合使用。

116.计算机可读信号介质可以包括在基带中或者作为截波一部分传播的数据信号,其中承载了计算机可读的程序代码。这种传播的数据信号可以采用多种形式,包括但不限于电磁信号、光信号或者其他任意合适的组合。计算机可读的信号介质还可以是计算机可读存储介质之外的任何计算机可读介质,该计算机可读介质可以发送、传播或者传输用于由指令系统、装置或器件使用或者与其结合使用的程序。

117.计算机可读介质上包含的程序代码可以用任何适当的介质传输,包括但不限于无线、电线、光缆、rf等等,以及上述任意合适的组合。

118.可以以一种或者多种程序设计语言或者组合来编写用于执行本公开实施例的计算机程序代码。所述程序设计语言包括面向对象的程序设计语言,例如java、c++,还可以包括常规的过程式程序设计语言,例如c。程序代码可以完全地在用户计算机上执行、部分地在用户计算机上执行、作为一个独立的软件包执行、部分在用户计算机上部分在远程计算机上执行、或者完全在远程计算机或服务器上执行。在涉及远程计算机的情形中,远程计算机可以通过任意种类的网络包括局域网(lan)或广域网(wan)连接到用户计算机,或者,可以连接到外部计算机(例如利用因特网服务提供商来通过因特网连接)。

119.以上所述仅为本公开的优选实施例,并不用于限制本公开,对于本领域技术人员而言,本公开可以有各种改动和变化。凡在本公开的精神和原理之内所作的任何修改、等同替换、改进等,均应包含在本公开的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1