一种FPGA传输系统及其解密解压器的制作方法

一种fpga传输系统及其解密解压器

技术领域

1.本发明属于信息技术领域,具体地说,是涉及一种fpga传输系统及其解密解压器。

背景技术:

2.随着fpga(field programmable gate array)应用规模越来越大,对开发过程的重视程度也不断增强。产生的配置文件如果不做特殊处理,在数据传输中很容易被破解,导致开发过程重要的信息会泄漏。

3.现有技术中可在电脑上对原配置文件进行加密,jtag仿真器从上游电脑获取加密数据,但目的fpga不能解析加密数据,需要将加密数据进行解密后传送给目的fpga,这导致解密后的配置文件在传送给目的fpga过程中仍然存在泄漏的风险。

技术实现要素:

4.本发明的目的在于提供一种fpga传输系统及其解密解压器,系统包括jtag仿真、解密解压器和目的fpga,在jtag仿真器的上游电脑进行配置数据的加密和压缩,保证配置数据不会在电脑和jtag仿真器之间泄漏,对解密解压器上的通用jtag接口协议进行改造,在目的fpga与捕获设备同时接入其jtag接口时,停止数据下发并产生报警信息,保证解密解压后的配置数据不会在解密解压器和目的fpga之间泄漏。

5.本发明采用以下技术方案予以实现:提出一种fpga传输系统,包括:pc,用于对fpga的配置文件进行加密加压生成加密加压配置文件;目的fpga,接收经解密解压后的配置文件;还包括:jtag仿真器,连接pc,基于pc的驱动接收其下发的加密加压配置文件;解密解压器,连接jtag仿真器,包括存储器、解密解压电路和jtag模块;所述存储器接收并保存所述jtag仿真器传送的加密加压配置文件;所述解密解压电路从所述存储器获取所述加密加压配置文件对其进行解密解压;所述jtag模块连接所述解密解压电路,将解密解压后的配置文件传送给所述目的fpga;其中,所述jtag模块对下游接入设备的电流进行检测,当电流超过阈值时,所述jtag模块产生控制信号,将所述控制信号引入tap状态机,停止tap状态机工作终止数据发送。

6.进一步的,所述解密解压器还包括:报警器,与所述jtag模块连接;当所述jtag模块检测下游接入设备的电流超过阈值时,所述jtag模块产生的控制信号驱动所述报警器发出报警。

7.提出一种应用于fpga传输系统的解密解压器,所述fpga传输系统包括:pc,用于对fpga的配置文件进行加密加压生成加密加压配置文件;目的fpga,接收经解密解压后的配置文件;jtag仿真器,连接pc,基于pc的驱动接收其下发的加密加压配置文件;所述解密解压器包括:存储器,用于接收并保存所述jtag仿真器传送的加密加压配置文件;解密解压电路,用于从所述存储器获取所述加密加压配置文件对其进行解密解压;jtag模块,连接所述解密解压电路,用于将解密解压后的配置文件传送给所述目的fpga;以及,对下游接入设备

的电流进行检测,当电流超过阈值时,所述jtag模块产生控制信号,将所述控制信号引入tap状态机,停止tap状态机工作终止数据发送。

8.进一步的,所述解密解压器还包括:报警器,与所述jtag模块连接;当所述jtag模块检测下游接入设备的电流超过阈值时,所述jtag模块产生的控制信号驱动所述报警器发出报警。

9.与现有技术相比,本发明的优点和积极效果是:本发明提出的fpga传输系统及其解密解压器,系统由pc、jtag仿真器、解密解压器和目的fpga组成,pc用于对fpga的配置文件进行加密加压生成加密加压配置文件;目的fpga接收经解密解压后的配置文件;jtag仿真器,连接pc,基于pc的驱动接收其下发的加密加压配置文件;密解压器连接jtag仿真器,包括存储器、解密解压电路和jtag模块;存储器接收并保存jtag仿真器传送的加密加压配置文件,解密解压电路从存储器获取加密加压配置文件对其进行解密解压,jtag模块连接解密解压电路,将解密解压后的配置文件传送给目的fpga;jtag模块对下游接入设备的电流进行检测,当电流超过阈值时,jtag模块产生控制信号,将控制信号引入tap状态机,停止tap状态机工作终止数据发送。本发明通过在jtag仿真器的上游电脑进行配置数据的加密和压缩,保证了配置数据不会在电脑和jtag仿真器之间泄漏,通过对解密解压器上的通用jtag接口协议进行改造,在目的fpga与捕获设备同时接入其jtag接口时,停止数据下发并产生报警信息,保证了解密解压后的配置数据不会在解密解压器和目的fpga之间泄漏。

10.结合附图阅读本发明实施方式的详细描述后,本发明的其他特点和优点将变得更加清楚。

附图说明

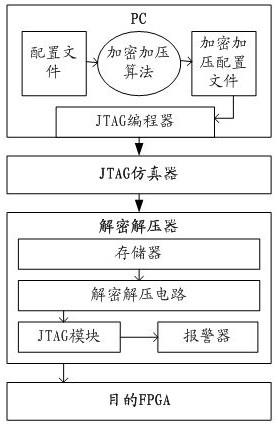

11.图1 为本发明提出的fpga传输系统的系统架构图;图2为本发明提出的解密解压器的组成结构图;图3为本发明tap状态机工作示意图。

具体实施方式

12.下面结合附图对本发明的具体实施方式作进一步详细的说明。

13.如图1所示,本发明提出的fpga传输系统,包括pc、目的fpga、jtag仿真器和解密解压器;pc用于对fpga的配置文件进行加密加压生成加密加压配置文件;目的fpga则接收经解密解压后的配置文件。

14.具体的,jtag仿真器连接pc,基于pc的jtag编程器软件程序的驱动,接收其下发的加密加压配置文件;解密解压器通过jtag接口与jtag仿真器连接,包括存储器、解密解压电路和jtag模块;存储器接收并保存jtag仿真器传送的加密加压配置文件;解密解压电路从存储器获取加密加压配置文件对其进行解密解压;jtag模块则通过改进的jtag接口(如图2所示)连接解密解压电路,将解密解压后的配置文件传送给目的fpga。

15.jtag模块对下游接入设备的电流进行检测,当电流超过阈值时,参考图3所示,jtag模块产生控制信号stall,将控制信号stall引入tap状态机,停止tap状态机工作终止数据发送。

16.具体的,下游接入设备理论上应该为目的fpga,当其他外接设备,诸如数据捕获器

接入时,如图2所示,由于vdd和gnd之间的电压不变,则连接的数据捕获器会使整体流过的电流增大,本发明改进jtag模块,当jtag模块判断电流超过阈值时,产生的控制信号强制tap状态机停止工作关闭tck 、tdi和tms通道。

17.如图3所示,改进的tap状态机将控制信号stall引入每一个状态,当stall置位则不再更新并停止当前状态,当stall复位,tap状态机在tms的变化完成状态更新,并发送数据。

18.本发明中,jtag接口由于不需要对下游接入接口进行修改,因此具有兼容性。

19.如图2所示,在本发明一些实施例中,解密解压器还包括与jtag模块连接的报警器;当jtag模块检测下游接入设备的电流超过阈值时,jtag模块产生的控制信号stall则驱动报警器发出报警。

20.应该指出的是,上述说明并非是对本发明的限制,本发明也并不仅限于上述举例,本技术领域的普通技术人员在本发明的实质范围内所做出的变化、改型、添加或替换,也应属于本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1