控制存储器系统的方法、计算机装置以及存储介质与流程

1.本技术涉及计算机技术领域,更具体地,涉及一种控制存储器系统的方法、计算机装置、存储介质、存储控制器以及存储器系统。

背景技术:

2.非易失性存储装置能够在断电后仍保留存储于其中的数据,并且广泛应用于计算机、蜂窝电话、智能手机、个人数字助理及其它电子设备系统。存储控制器用于控制非易失性存储装置的各项操作,并协调非易失性存储装置和主机(host)之间的数据调度。

3.此外,存储控制器还用于完成主机的逻辑地址到非易失性存储装置中的物理地址的映射(mapping)。通过主机对非易失性存储装置执行例如编程操作时,存储控制器将该编程操作对应的逻辑地址到物理地址的映射关系(l2p)数据写入至非易失性存储装置中,以便主机利用该映射关系数据读取编程操作的编程数据。

4.在一些实际应用中,l2p映射表还可存放于主机的存储器(例如内存)中,以提高存储控制器控制非易失性存储装置执行随机读取速度。然而,将l2p映射表加载至主机内存中进行维护会占用大量的主机内存空间,这是非易失性存储装置的存储控制器开发中亟待解决的技术问题。

技术实现要素:

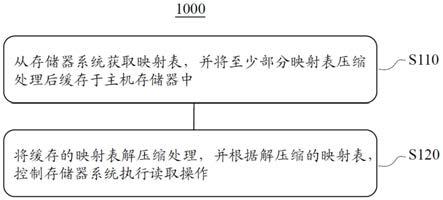

5.本技术一个方面提供了一种控制存储器系统的方法。该方法包括:从存储器系统获取映射表,并将至少部分映射表压缩处理后缓存于主机存储器中;以及将缓存的映射表解压缩处理,并根据解压缩处理后的映射表,控制存储器系统执行读取操作。

6.在一些实施方式中,控制存储器系统执行读取操作的步骤包括:在主机性能提升hpb的读取模式下,控制存储器系统执行读取操作。

7.在一些实施方式中,存储器系统为ufs存储器系统。

8.在一些实施方式中,存储器系统包括存储控制器以及非易失性存储装置,其中,控制存储器系统执行读取操作的步骤包括:根据解压缩处理后的映射表和逻辑地址获取存储于非易失性存储装置中将要被读取的数据的物理地址,并将物理地址发送至存储控制器。

9.在一些实施方式中,从存储器系统获取映射表的步骤包括:在存储器系统处于空闲阶段的情况下,从存储器系统获取映射表。

10.在一些实施方式中,从存储器系统获取映射表的步骤之后,方法还包括:响应于存储器系统对部分映射表的更新请求,从存储器系统获取更新的映射表。

11.在一些实施方式中,从存储器系统获取更新的映射表的步骤包括:将缓存于主机存储器中的欲更新的映射表解压缩处理,对解压缩处理后的映射表执行更新操作。

12.在一些实施方式中,根据映射表的逻辑地址划分为多个逻辑块,其中,在将至少部分映射表压缩处理后缓存于主机存储器中的步骤中,以逻辑块为单位,对每个逻辑块对应的映射表进行压缩处理。

13.在一些实施方式中,将缓存的映射表解压缩处理的步骤包括:根据逻辑地址确定相应的逻辑块,并对包括逻辑块的映射表解压缩处理。

14.在一些实施方式中,根据映射表的逻辑地址划分为多个逻辑块,每个逻辑块包括多个子逻辑块,其中,在将至少部分映射表压缩处理后缓存于主机存储器中的步骤中,以子逻辑块为单位,对每个子逻辑块对应的映射表进行压缩处理。

15.在一些实施方式中,将缓存的映射表解压缩处理的步骤包括:根据逻辑地址确定相应的子逻辑块,并对包括子逻辑块的映射表解压缩处理。

16.在一些实施方式中,从存储器系统获取映射表,并将至少部分映射表压缩处理后缓存于主机存储器中的步骤包括:根据利用映射表执行读取操作的参考频率,将至少部分映射表压缩处理后缓存于主机存储器。

17.在一些实施方式中,通过gzip压缩算法、lzo压缩算法以及zippy/snappy压缩算法的其中之一,对映射表进行压缩和/或解压缩处理。

18.本技术另一个方面提供了一种计算机装置。该计算机装置包括:处理器;以及与处理器通信连接的存储器;存储器存储有可被处理器执行的驱动程序,驱动程序被处理器执行,以使处理器能够执行上文中任意实施方式所描述的控制存储器系统的方法。

19.本技术另一个方面还提供了一种存储有计算机程序的非瞬时计算机可读介质,该计算机程序用于使计算机执行上文中任意实施方式所描述的控制存储器系统的方法。

20.本技术的另一个方面还提供了一种存储控制器。该存储控制器用于控制非易失性存储装置,并且存储控制器和非易失性存储装置用于构成存储器系统。该存储控制器被配置为:将存储于存储器系统的映射表发送至主机,以使至少部分映射表被压缩处理后缓存于主机的主机存储器中;以及根据缓存于主机存储器中的、经过解压缩处理后的映射表,控制非易失性存储装置执行读取操作。

21.本技术的另一个方面还提供了一种存储器系统。该存储器系统包括:非易失性存储装置;以及存储控制器,用于控制非易失性存储装置,其中,该存储控制器被配置为:将存储于存储器系统的映射表发送至主机,以使至少部分映射表被压缩处理后缓存于主机的主机存储器中;以及根据缓存于主机存储器中的、经过解压缩处理后的映射表,控制非易失性存储装置执行读取操作。

22.本技术提供的控制存储器系统的方法、计算机装置、存储介质、存储控制器以及存储器系统,通过使映射表压缩缓存于主机存储器中,可减少缓存于主机存储器中的映射表对主机存储器的存储空间资源的占用,有利于主机与存储器系统的交互操作。

附图说明

23.通过阅读参照以下附图所作的对非限制性实施例所作的详细描述,本技术的其它特征、目的和优点将会变得更明显:

24.图1是根据本技术实施方式的主机和存储器系统的结构示意图;

25.图2是根据本技术实施方式的控制存储器系统的方法的流程图;

26.图3是根据本技术实施方式的利用主机存储器资源执行控制存储器系统方法的示意图;

27.图4是根据本技术实施方式中的逻辑块与物理块映射关系示意图;

28.图5是本技术实施方式的逻辑块中的部分映射表结构示意图;

29.图6是根据本技术实施方式的利用主机存储器资源执行控制映射表执行更新操作方法的示意图;以及

30.图7是适用于实现本技术实施方式的计算机装置的结构示意图。

具体实施方式

31.为了更好地理解本技术,将参考附图对本技术的各个方面做出更详细的说明。应理解,这些详细说明只是对本技术的示例性实施方式的描述,而非以任何方式限制本技术的范围。

32.本文使用的术语是为了描述特定示例性实施方式的目的,并且不意在进行限制。当在本说明书中使用时,术语“包含”、“包含有”、“包括”和/或“包括有”表示存在所述特征、整体、元件、部件和/或它们的组合,但是并不排除一个或多个其它特征、整体、元件、部件和/或它们的组合的存在性。

33.本文参考示例性实施方式的示意图来进行描述。本文公开的示例性实施方式不应被解释为限于示出的具体形状和尺寸,而是包括能够实现相同功能的各种等效结构以及由例如制造时产生的形状和尺寸偏差。附图中所示的位置本质上是示意性的,而非旨在对各部件的位置进行限制。

34.除非另有限定,否则本文使用的所有术语(包括技术术语和科学术语)具有与本公开所属技术领域的普通技术人员的通常理解相同的含义。诸如常用词典中定义的术语应被解释为具有与其在相关领域的语境下的含义一致的含义,并且将不以理想化或过度正式的意义来解释,除非本文明确地如此定义。

35.图1是根据本技术实施方式的主机20和存储器系统10的结构示意图。如图1所示,存储器系统10可存储有主机20访问的数据,主机20可包括移动电话、mp3播放器、膝上型计算机、台式计算机、游戏机、电视或者车载信息娱乐系统等。根据存储器系统10与主机20连接的接口协议,存储器系统10可被配置为诸如通用闪存存储(ufs)装置,固态硬盘(ssd),mmc、emmc、rs

‑

mmc和微型mmc形式的多媒体卡,sd、迷你sd和微型sd形式的安全数字卡,个人计算机存储卡国际协会(pcmcia)卡类型的存储装置,外围组件互连(pci)类型的存储装置,高速pci(pci

‑

e)类型的存储装置,紧凑型闪存(cf)卡,智能媒体卡或者记忆棒等。

36.主机20控制存储器系统10的整体操作。主机20可包括主机处理器310和主机存储器320。

37.主机处理器310可控制主机20的操作。例如,主机处理器310可通过例如存储驱动器与存储器系统10进行交互,以控制存储器系统10的各种操作。其中,存储驱动器可例如为用于控制存储器系统10的软件模块。主机20可经由存储驱动器控制存储器系统10执行例如数据编程、读取以及擦除操作。示例性地,存储驱动器还包括例如主机性能提升(host performance booster,hpb)模块和写入性能提升(write booster,wb)模块。通过主机性能提升模块,主机20可将映射表加载于主机存储器320中,以提升主机处理器310控制存储器系统10执行读取操作的速度。具体地,利用主机性能提升模块控制存储器系统10执行读取操作的方法将在下文中详细地描述。

38.主机存储器320可存储有处理器310执行和/或处理的指令和/或数据。主机存储器

320可为具有相对较快操作速度的存储装置。主机存储器320可至少包括各种易失性存储器之一,例如dram。

39.存储器系统10可包括非易失性存储装置100和存储控制器200。

40.非易失性存储装置100可为存储器系统10用于存储数据的存储介质。非易失性存储装置100可具有一个或多个存储管芯(die)。每个存储管芯可包括存储单元阵列,该存储单元阵列可包括布置于字线和位线相交处的多个存储单元。存储单元阵列可被划分为多个存储块,每个存储块可被进一步地划分为多个子存储块,并且每个存储块或者每个子存储块可包括多个页面。存储单元阵列中的每个存储单元可为能够存储一位数据的单层存储单元(slc)、能够存储两位数据的两层存储单元(mlc)、能够存储三位数据的三层存储单元(tlc)以及能够存储四位数据的四层存储单元(qlc)中的任意一种。示例性地,非易失性存储装置100可为三维nand闪存存储装置,更具体地,非易失性存储装置100可例如为并行地设置的多个三维nand闪存存储装置,以实现例如256g以上的大容量数据存储。

41.存储控制器200可包括主机接口210、处理器220和存储器接口230。存储控制器200可通过驱动存储于非易失性存储装置100中的固件或软件来控制存储器系统10执行操作。存储控制器200可解码并驱动诸如固件或软件的代码类型的指令或算法。并且存储控制器200可被实施为硬件或硬件和软件的组合。

42.主机接口210(也可称为“前端接口”)可根据接口协议连接主机20和存储器系统10。主机接口210可通诸如通用闪存(ufs)协议、串行高级技术附件(sata)协议、外围组件互连(pci)协议和高速pci(pci

‑

e)协议、通用串行总线(usb)协议、多媒体卡(mmc)协议、并行高级技术附件(pata)协议、小型计算机系统接口(scsi)协议、串列scsi(sas)协议等中的任意一种与主机20通信。

43.处理器220可通过例如arm核等实现,并且可驱动被称为闪存转换层(ftl)的固件,以便控制非易失性存储装置100的固有操作并且对主机20提供装置兼容性。当驱动ftl时,主机20可将存储器系统10视为并用作诸如硬盘的通用存储装置。此外,处理器220还可通过诸如驱动固件实现磨损均衡(wear leveling)、垃圾收集(garbage collection)、坏块管理(bad block management)等功能。

44.存储器接口230(也可以称为“后端接口”)可根据处理器220例如flash存储控制器来控制非易失性存储装置100。存储器接口230可将控制信号提供至非易失性存储装置100。控制信号可以包括用于控制非易失性存储装置100的命令、地址和操作控制信号等。存储器接口230可根据相应的接口协议连接非易失性存储装置100。示例性地,存储器接口230可例如通过onfi协议与非易失性存储装置100通信交互。

45.图2是根据本技术实施方式的控制存储器系统的方法1000的流程图。图3是根据本技术实施方式的利用主机存储器资源执行控制存储器系统的方法的示意图。

46.如图2和图3所示,在步骤s110中,示例性地,当主机20与存储器系统10建立通信连接后,主机20中主机处理器310可发送初始化请求,存储器系统10中的存储控制器200接收初始化请求,将存储器系统10的对应于非易失性存储装置100的映射表发送至主机20。

47.在一些实施方式中,可在存储器系统10在空闲阶段的情况下,将存储器系统10的对应于非易失性存储装置100的映射表发送至主机20。换言之,主机20可在存储器系统10处于空闲阶段的情况下,从存储器系统10获取映射表,以避免与存储器系统10执行其它操作

产生冲突。应当理解的是,存储器系统10处于空闲阶段的情况可例如为存储器系统10未执行编程、读取或者擦除操作的情况。

48.映射表可表示为逻辑地址lba至物理地址pba之间的映射关系,故可被称为l2p(logical to physical)表。在现有技术中,主机20可利用逻辑地址lba访问非易失性存储装置100,存储器系统10中的存储控制器200可利用物理地址pba访问非易失性存储装置100。应当理解的是,当主机20读取存储于非易失性存储装置100的数据时,存储器系统10中的存储控制器200利用这些映射表,从非易失性存储装置100读取想要读取的数据,并发送至主机20,从而使主机获取存储于非易失性存储装置100中的想要读取的数据。

49.图4是根据本技术实施方式中的逻辑块与物理块映射关系示意图。如图4所示,根据映射粒度的不同,生成映射表的方法包括块映射。在块映射中,映射表中的一个逻辑块(region)可映射至任意一个非易失性存储装置100中的存储块对应的物理块。应当理解的是,在非易失性存储装置100中的一个存储块包括多个子存储块的情况下,在块映射中,映射表中的一个子逻辑块(subregion)可映射至任意一个非易失性存储装置100中的子存储块对应的子物理块。并且逻辑块对应的物理块,或者子逻辑块对应的子物理块的大小可相同。

50.进一步地,在该步骤中,主机20可将从存储器系统10获取的映射表加载至其主机存储器320中。其中,主机存储器320可包括但不限于dram和sram。具体地,主机处理器310对至少部分映射表进行压缩处理。其中,主机20中的主机处理器310可通过调用数据压缩处理程序,对加载至主机存储器320中的至少部分映射表进行压缩处理。数据压缩处理程序可根据诸如gzip压缩算法、lzo压缩算法以及zippy/snappy压缩算法的任意一种或者其组合而生成。

51.图5是本技术实施方式的逻辑块中的部分映射表结构示意图。如图5所示,映射表以16进制数表示。其中,映射表中的每一行可表示一条逻辑地址至物理地址的映射关系,并将每一行称为一个表项。由于每个表项中的映射表通常采用随机化加密处理,但逻辑块/子逻辑块中的多个表项之间存在规律性,故根据数据压缩原理,可将缓存于主机存储器中的映射表以逻辑块或者子逻辑块为单位执行数据压缩处理,从而提高缓存于主机中的至少部分映射表的压缩率。

52.举例而言,lzo压缩算法采用(重复长度l,指回距离d)代替当前已经在历史字符串中出现过的字符串,其中,重复长度是指后出现的字符串与先出现的字符串中连续相同部分的长度。指回距离d是指先后两个相同字符串之间相隔的距离(每个字节为一个单位)。如果没出现过(定义为新字符),则首先输出新字符的个数,再输出新字符。在本技术实施方式中,采用lzo算法可将行号为000000d0中的字符串(b9 5f b8 fa)作为行号为000000c8的重复出现过的字符串进行压缩处理。

53.表1是现有的gzip压缩算法、lzo压缩算法以及zippy/snappy压缩算法的压缩性能参数表。在采用例如gzip压缩算法对缓存于主机20中的6k大小的映射表执行压缩处理后,实测压缩率可小于或者等于40%。

54.压缩算法压缩率%压缩速率mb/s解压缩速率mb/sgzip1320120lzo20130420

zippy/snappy22170410

55.表1

56.在一些实施方式中,可根据利用映射表执行读取操作的参考频率,将至少部分映射表压缩处理后缓存于主机存储器中。应当理解的是,将一些用于执行读取操作的参考频率较高的映射表以解压缩状态缓存于主机存储器中,并将一些用于执行读取操作的参考频率较低的映射表以压缩状态缓存于主机存储器中,可在减少缓存于主机存储器中的存储空间的前提下,确保主机利用映射表读取非易失性存储装置100中的数据的实时性。

57.在步骤s120中,再次参考图2和图3,当主机20想要控制存储器系统10执行读取存储于非易失性存储装置100中的数据操作时,示例性地,主机20可通过上文中描述的gzip压缩算法、lzo压缩算法以及zippy/snappy压缩算法中的任意一种对应的解压缩算法,对读取操作对应的、缓存于主机存储器320中的压缩映射表进行解压缩处理。主机20根据解压缩处理后的映射表,获取想要读取的数据的物理地址,并将该物理地址发送至存储器系统10。换言之,主机20可访问所请求的数据的逻辑地址和解压缩后的映射表,通过向存储控制器200发送读取请求(包括想要读取的数据的物理地址),使存储控制器200响应于该请求,访问所请求的数据的物理地址以读取存储于非易失性存储装置100中的所请求的数据。进一步地,存储器系统10中的存储控制器200可通过存储控制器200将所请求读取的数据发送回主机20。

58.在一些实施方式中,由于在对缓存于主机存储器320中的映射表以逻辑块/子逻辑块为单位执行数据压缩处理,故在主机20控制存储器系统10执行读取操作时,主机处理器310可根据想要读取的数据的逻辑地址确定出对应的逻辑块/子逻辑块,并对包括该逻辑块/子逻辑块的映射表进行解压缩处理,以使主机20执行后续的读取操作。

59.图6是根据本技术实施方式的利用主机存储器资源执行控制映射表执行更新操作方法的示意图。如图6所示,在该实施方式中,在主机20将存储于存储器系统10中的映射表加载至其内部的主机存储器320中之后,存储控制器200可通过诸如垃圾回收操作、读取回收操作、数据更新操作等使映射表发生改变,故存储控制器200可发送更新数据请求至主机20,使缓存于主机存储器320中的映射表更新。换言之,主机20可响应于存储器系统10的更新请求,获取更新的映射表。具体地,由于部分映射表压缩缓存于主机20的存储器中,故可采用诸如gzip压缩算法、lzo压缩算法以及zippy/snappy压缩算法的一种或者其组合使更新请求所对应的映射表经过解压缩处理、更新及再次压缩处理后缓存于主机20的存储器中,以使映射表中的逻辑地址和物理地址在更新操作后一一对应。

60.如背景技术中所述,在现有的利用主机存储器资源执行存储控制器的操作方法中,在一个物理块对应一个逻辑块的情况下,假设每个逻辑块中的一个表项占用8个字节,则将映射表全部加载至主机存储器中所占用的存储空间大小total size为:

[0061][0062]

其中,lun size为非易失性存储装置中一个逻辑单元lun的存储空间大小,可例如为128gb。block size为非易失性存储装置中一个逻辑单元lun中的存储块block的存储空间大小,可例如为4kb。因而,主机存储器中所占用的存储空间大小total size可为256mb。在非易失性存储装置的逻辑单元lun的存储空间大小逐步增加的发展趋势下,映射表缓存

于主机存储器中所占用的存储空间也会逐步增加,会对主机存储器造成负担,不利于主机与存储控制器/存储器系统的交互操作。

[0063]

本技术提供的控制存储器系统的方法,通过使映射表压缩缓存于主机存储器中,可减少缓存于主机存储器中的映射表对主机存储器的存储空间资源的占用,有利于主机与存储控制器的交互操作。

[0064]

本技术还提供了一种计算机装置,图7是适用于实现本技术实施方式的计算机装置2000的结构示意图。应理解的是,图7示出的计算机装置仅仅是一个示例,不应对本技术实施方式的功能和使用范围带来任何限制。

[0065]

如图7所示,计算机装置2000包括至少一个处理器1(例如cpu),其可以根据存储在只读存储器(rom)2中的程序或者从存储部分6加载到随机访问存储器(ram)3中的程序而执行各种适当的操作和处理。在ram 3中,还存储计算机装置2000操作所需的各种程序和数据。处理器1、rom 2以及ram 3通过总线4彼此相连。输入/输出(i/o)接口5也连接至总线4。

[0066]

以下部件连接至i/o接口5:包括硬盘等的存储部分6;以及包括诸如lan卡、调制解调器等的网络接口卡的通信部分7。通信部分7经由诸如因特网的网络执行通信处理。驱动器8也根据需要连接至i/o接口5。可拆卸介质9,诸如磁盘、光盘、磁光盘、半导体存储器等,根据需要安装在驱动器8上,以便于从其上读出的计算机程序根据需要被安装入存储部分6。

[0067]

本领域普通技术人员可以理解,实现上述实施方式的方法中的全部或部分步骤是可以通过程序来指令相关的硬件来完成,所述的程序可以存储于一计算机可读取存储介质中,该程序在执行时,包括如下步骤:s100,从存储器系统获取映射表,并将至少部分映射表压缩处理后缓存于主机存储器中;以及s120,将缓存的映射表解压缩处理,并根据解压缩的映射表,控制存储器系统执行读取操作。

[0068]

本技术还提供了一种存储控制器和存储器系统。由于上文中所描述的任意实施方式可适用于本技术提供的存储控制器和存储器系统,本技术在此不再赘述。

[0069]

以上描述仅为本技术的较佳实施方式以及对所运用技术原理的说明。本领域技术人员应当理解,本技术中所涉及的发明范围,并不限于上述技术特征的特定组合而成的技术方案,同时也应涵盖在不脱离所述发明构思的情况下,由上述技术特征或其等同特征进行任意组合而形成的其它技术方案。例如上述特征与本技术中公开的(但不限于)具有类似功能的技术特征进行互相替换而形成的技术方案。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1