一种非易失性存储器的制作方法

1.本技术涉及数据存储技术领域,具体是涉及一种非易失性存储器。

背景技术:

2.在嵌入式系统中,由于其中各类设备需要的存储容量和类型各不相同,同一个系统中往往会需要同时使用多种不同类型的存储器,例如或非型闪存(又称nor闪存、nor flash)、与非型闪存(又称nand闪存、nand flash)、只读存储器(read-only memory,rom)、电子程序控制只读存储器(electronic programmable read-only memory,eprom)、可编程只读存储器(programmable read-only memory,prom)、电可擦可编程只读存储器(electrically erasable programmable read-only memory,eeprom)、电改写只读存储器(electrically alterable read-only memory,earom)、磁性随机存储器(magnetic random access memory,mram)、铁电随机存储器(ferroelectric random access memory,fram)等等。这就需要在系统中为多种存储器分别设置不同的封装结构和接口结构。

3.但是另一方面,嵌入式设备的尺寸需要尽量小型化,而设置多种不同的封装结构和接口结构显然需要占用更多的空间,对设备的小型化造成阻碍。

4.因此,需要提供一种可以解决上述问题的适用于嵌入式系统的存储装置。

技术实现要素:

5.本技术的实施方式提供一种非易失性存储器,所述非易失性存储器包括封装结构、第一存储单元和第二存储单元;其中所述第一存储单元和第二存储单元为类型不同的非易失性存储单元,且所述第一存储单元和第二存储单元都封装在所述封装结构内,用于相互独立地进行工作。

6.优选地,所述第一存储单元和第二存储单元是从或非型闪存、与非型闪存、只读存储器、电子程序控制只读存储器、可编程只读存储器、电可擦可编程只读存储器、电改写只读存储器、磁性随机存储器、铁电随机存储器中选择的任意两种类型不同的存储器。

7.优选地,所述第一存储单元的容量小于所述第二存储单元的容量。

8.优选地,所述非易失性存储器还包括第一接口和第二接口,所述第一接口为总线协议接口或者串行外设接口,用于将所述第一存储单元与外界连接;所述第二接口为与非型接口或者串行外设接口,用于将所述第二存储单元与外界连接。

9.优选地,所述第一存储单元的位置相比于所述第二存储单元更加接近所述封装结构的内部。

10.优选地,所述非易失性存储器还包括控制单元,所述控制单元与所述第一存储单元和第二存储单元连接,用于在所述第一存储单元和第二存储单元中读取或写入数据,或者仅与所述第二存储单元连接,用于在所述第二存储单元中读取或写入数据。

11.优选地,所述控制单元与所述第一存储单元和第二存储单元连接;所述封装结构包括内封装部和外封装部,所述第一存储单元、第二存储单元、内封装部和控制单元都封装

在所述外封装部之内,并且所述第一存储单元和第二存储单元封装在所述内封装部之内,所述控制单元处于所述内封装部之外。

12.优选地,所述非易失性存储器还包括第一接口、第二接口和第三接口,所述第一接口为总线协议接口或者串行外设接口,用于将所述第一存储单元与所述控制单元连接;所述第二接口为与非型接口或者串行外设接口,用于将所述第二存储单元与所述控制单元连接;所述第三接口为串行高级技术附加装置接口、周边装置互连高速接口、串行外设接口、通用串行总线接口、安全数码卡接口、嵌入式多媒体卡接口、通用闪存存储接口中的任意一种,用于将所述控制单元与外界连接。

13.优选地,所述控制单元与所述第二存储单元连接;所述封装结构包括内封装部和外封装部,所述第一存储单元、第二存储单元、内封装部和控制单元都封装在所述外封装部之内,并且所述第一存储单元和第二存储单元封装在所述内封装部之内,所述控制单元处于所述内封装部之外。

14.优选地,所述非易失性存储器还包括第一接口、第二接口和第三接口,所述第一接口为总线协议接口或者串行外设接口,用于将所述第一存储单元与外界连接;所述第二接口为与非型接口或者串行外设接口,用于将所述第二存储单元与所述控制单元连接;所述第三接口为串行高级技术附加装置接口、周边装置互连高速接口、串行外设接口、通用串行总线接口、安全数码卡接口、嵌入式多媒体卡接口、通用闪存存储接口中的任意一种,用于将所述控制单元与外界连接。

15.优选地,所述非易失性存储器还包括电源管理单元,所述电源管理单元与所述第一存储单元、第二存储单元以及控制单元分别连接,用于分别给所述第一存储单元、第二存储单元以及控制单元提供工作电压。

16.优选地,所述封装结构为球栅阵列封装结构。

17.如上所述,本技术的各个实施方式提供的非易失性存储器都能够把两种不同类型的存储器封装在同一个封装结构内,并且能够通过例如bga结构使封装结构的整体尺寸不大于(或者不明显大于)仅封装一种类型的存储器的传统存储器封装结构。这样,所述非易失性存储器就能够同时提供两种不同类型的存储器的功能,而且占用的体积并不大于(或者不明显大于)一个仅能提供一种存储器功能的传统存储器,不会影响到小型化的设计需求。因此,本技术的实施方式提供的非易失性存储器能够解决嵌入式系统中一方面需要同时使用多种不同类型的存储器,另一方面又需要顾及小型化设计的技术问题。

附图说明

18.为了更清楚地说明本技术实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

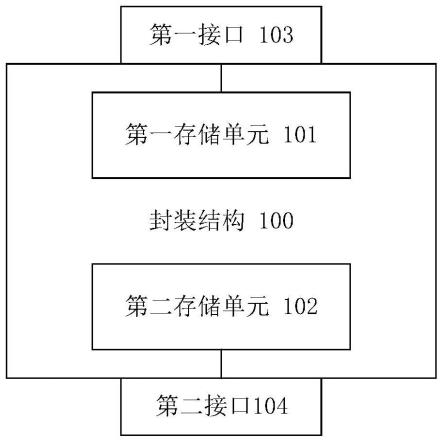

19.图1是本技术的第一种示例性实施方式提供的一种非易失性存储器的结构示意图。

20.图2是本技术的第二种示例性实施方式提供的一种非易失性存储器的结构示意图。

21.图3是本技术的第三种示例性实施方式提供的一种非易失性存储器的结构示意图。

22.图4是本技术的第四种示例性实施方式提供的一种非易失性存储器的结构示意图。

23.图5是图4所示的非易失性存储器安装在嵌入式系统中的电路示意图。

具体实施方式

24.下面结合附图和实施例,对本技术作进一步的详细描述。特别指出的是,以下实施例仅用于说明本技术,但不对本技术的范围进行限定。同样的,以下实施例仅为本技术的部分实施例而非全部实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其它实施例,都属于本技术保护的范围。

25.请参阅图1,本技术的第一种示例性实施方式提供一种非易失性存储器10,所述非易失性存储器10包括封装结构100、第一存储单元101、第二存储单元102、第一接口103、第二接口104。

26.封装结构100优选采用球栅阵列封装(ball grid array package,bga)结构。第一存储单元101和第二存储单元102都封装在封装结构100内。由于bga结构相比于传统的封装技术能够实现更小的体积以及更好的散热性能和电性能,使得单位面积内的存储量有了很大提升,因此封装结构100能够在较小的整体尺寸(例如可以是不大于或者不明显大于传统的单一存储器封装结构的尺寸)下确保其中封装的第一存储单元101和第二存储单元102都具备理想的存储容量,使得第一存储单元101和第二存储单元102能够共享同一个封装结构100,而且能够分别正常工作以实现各自的数据存储功能。

27.其中所述第一存储单元101和第二存储单元102是两个类型不同,且相互独立工作的非易失性存储单元。具体在种类上,第一存储单元101和第二存储单元102可以分别是从nor flash、nand flash、rom、eprom、prom、eeprom、earom、mram、fram中选择的任意两种类型不同的存储器,本实施方式中第一存储单元101优选采用eeprom,第二存储单元102优选采用nand flash。

28.第一接口103和第二接口104都设置在封装结构100上,并且可以和封装结构100一体化设置。第一接口103与第一存储单元101连接,第一存储单元101可以通过第一接口103与外界进行通信。第二接口104与第二存储单元102连接,第二存储单元102可以通过第二接口104与外界进行通信,例如接受nand主控单元的控制。

29.在本实施方式中,第一接口103优选采用适用于eeprom的总线协议(inter-integrated circuit,iic)接口或者串行外设接口(serial peripheral interface,spi),第二接口104优选采用适用于nand flash的与非型(nand)接口或者spi。通过第一接口103和第二接口104,第一存储单元101和第二存储单元102中存储的数据就可以被读取出来,另外若是第一存储单元101及第二存储单元102为非只读存储器,则也可以通过第一接口103和第二接口104向其中写入数据。

30.如上所述,所述非易失性存储器10把两种不同类型的存储器单元101、102封装在同一个封装结构100内,并且能够使封装结构100的整体尺寸不大于(或者不明显大于)仅封装一种类型的存储器的传统存储器封装结构。这样,所述非易失性存储器10就能够同时提

供两种不同类型的存储器的功能,而且占用的体积并不大于(或者不明显大于)一个仅能提供一种存储器功能的传统存储器,不会影响到小型化的设计需求。因此,所述非易失性存储器10就能够解决嵌入式系统中一方面需要同时使用多种不同类型的存储器,另一方面又需要顾及小型化设计的技术问题。

31.可以理解,所述非易失性存储器10除了所述第一存储单元101和第二存储单元102之外,还可以进一步包括其他类型的存储单元,只要确保所有存储单元都能够封装在封装结构100内,并分别正常工作以实现各自的数据存储功能即可。

32.在一些优选的实施方式中,还可以把第一存储单元101和第二存储单元102分别设置成具有不同的容量,优选为第一存储单元101的容量小于第二存储单元102的容量。相应地,也可以减小第一存储单元101在封装结构100内的布局面积,而增大第二存储单元102在封装结构100内的布局面积。

33.在又一些优选的实施方式中,第一接口103和第二接口104的实际位置可以设置成分别靠近于封装结构100的两个相对侧面,这样可以在接线时减少对彼此的影响。

34.另外,由于第一存储单元101通常可以采用低速存储器,相比于第二存储单元102,第一存储单元101的布线长度可以更长,线径可以更细,因此在又一些优选的实施方式中,可以把第一存储单元101布置得相比于第二存储单元102更加接近封装结构100的内部。

35.请参阅图2,本技术的第二种示例性实施方式提供一种非易失性存储器20,所述非易失性存储器20包括封装结构200、第一存储单元201、第二存储单元202、第一接口203、第二接口204、控制单元205、第三接口206。

36.其中封装结构200可以包括内封装部210和外封装部220。内封装部210可以和前述实施方式中的封装结构100采用相同的类型;第一存储单元201、第二存储单元202、第一接口203、第二接口204可以分别和前述实施方式中的第一存储单元101、第二存储单元102、第一接口103、第二接口104采用相同的类型。第一存储单元201和第二存储单元202都封装在内封装部210内。第一接口203和第二接口204都设置在内封装部210上,并且可以和内封装部210一体化设置。

37.第一接口203将第一存储单元201与控制单元205连接,第二接口204将第二存储单元202与控制单元205连接,使得控制单元205能够根据接收到的指令与第一存储单元201及第二存储单元202进行通信,从而读取第一存储单元201及第二存储单元202中的数据(当第一存储单元201及第二存储单元202为非只读存储器时也可以向其中写入数据)。

38.第三接口206与控制单元205连接,使得控制单元205可以通过第三接口206与外界部件例如嵌入式系统的主机连接并进行通信。这样,控制单元205就能够通过第三接口206接收外界的指令,也能够通过第三接口206把从第一存储单元201及第二存储单元202中读取的数据传输出去。第三接口206优选可以采用串行高级技术附加装置(serial advanced technology attachment,sata)接口、周边装置互连高速(peripheral component interconnect express,pcie)接口、spi、通用串行总线(universal serial bus,usb)接口、安全数码卡(secure digital memory card,sd)接口、嵌入式多媒体卡(embedded multi media card,emmc)接口、通用闪存存储(universal flash storage,ufs)接口中的任意一种。

39.外封装部220优选也采用bga结构,将控制单元205和封装有第一存储单元201、第

二存储单元202并设有第一接口203、第二接口204的内封装部210都封装在其中。控制单元205优选被布置在内封装部210之外。第三接口206设置在外封装部220上,并且可以和外封装部220一体化设置。

40.相比于前述实施方式提供的非易失性存储器10,本实施方式的非易失性存储器20进一步整合了控制单元205。当所述非易失性存储器20用于嵌入式系统中时,除了能够具备前述非易失性存储器10的优点之外,其控制单元205还能够分担有关读写存储数据的运算工作,提高嵌入式系统的工作效率。

41.另外,在一些实施方式中,封装结构200也可以不包括内封装部210而仅包括外封装部220,将第一存储单元201、第二存储单元202、第一接口203、第二接口204都直接封装在外封装部220中即可。

42.请参阅图3,本技术的第三种示例性实施方式提供一种非易失性存储器30,所述非易失性存储器30包括封装结构300、第一存储单元301、第二存储单元302、第一接口303、第二接口304、控制单元305、第三接口306。

43.其中封装结构300可以包括内封装部310和外封装部320。内封装部310可以和前述实施方式中的内封装部210采用相同的类型,外封装部320可以和前述实施方式中的外封装部220采用相同的类型。第一存储单元301、第二存储单元302、第一接口303、第二接口304、控制单元305、第三接口306可以分别和前述实施方式中的第一存储单元201、第二存储单元202、第一接口203、第二接口204、控制单元205、第三接口206采用相同的类型。

44.所述非易失性存储器30和前述的非易失性存储器20的区别在于,第一存储单元301并不封装在内封装部310之内,而是位于内封装部310之外;其对应的第一接口303并不与控制单元305连接,而是用于将第一存储单元301直接与外界连接。第二存储单元302及其对应的第二接口304、以及控制单元305则都封装在内封装部310内,封装有第二存储单元302和控制单元305的内封装部310与第一存储单元301一起被封装在外封装部320内。在结构上,所述非易失性存储器30的第一接口303可以设置在外封装部320上或者与外封装部320一体化设置,通过例如导线、过孔等连接方式与第一存储单元301连接。而所述非易失性存储器30的第二接口304及第三接口306则与前述非易失性存储器20的第二接口204及第三接口206类似,第二接口304设置在内封装部310上或者可以与内封装部310一体化设置,用于将第二存储单元302与控制单元305连接;第三接口306设置在外封装部320上或者可以与外封装部320一体化设置,用于将控制器305与外界部件例如嵌入式系统的主机连接。

45.相比于前述实施方式提供的非易失性存储器10及20,本实施方式的非易失性存储器30仅将第二存储单元302通过控制单元305与外界连接,而将第一存储单元301通过另一条独立的路径直接与外界连接,这样进一步扩展了非易失性存储器30的连接方式,同时能够减轻控制单元305的运算负荷。

46.在一些优选的实施方式中,还可以把第一存储单元301和第二存储单元302分别设置成具有不同的容量,优选为第一存储单元301的容量小于第二存储单元302的容量。这样有助于在封装时尽量减小第一存储单元301占用的空间,给需要封装在一起的第二存储单元302、第二接口304、以及控制单元305提供较充裕的安装空间。

47.在又一些优选的实施方式中,第一接口303和第二接口304的实际位置可以设置成分别靠近于外封装部320的两个相对侧面,这样可以在接线时减少对彼此的影响。

48.另外,由于第一存储单元301通常可以采用低速存储器,相比于第二存储单元302,第一存储单元301的布线长度可以更长,线径可以更细,因此在又一些优选的实施方式中,可以把第一存储单元301布置得相比于第二存储单元302更加接近外封装部320的内部。

49.显然,在又一些优选的实施方式中,封装结构300也可以不包括内封装部310而仅包括外封装部320,此时可以将第一存储单元301、第二存储单元302、第二接口304也都直接封装在外封装部320中。

50.请参阅图4,本技术的第四种示例性实施方式提供一种非易失性存储器40,所述非易失性存储器40包括封装结构400、第一存储单元401、第二存储单元402、第一接口403、第二接口404、控制单元405、第三接口406、以及电源管理单元407。

51.所述封装结构400包括内封装部410和外封装部420。其中内封装部410、外封装部420、第一存储单元401、第二存储单元402、第一接口403、第二接口404、控制单元405、第三接口406都可以分别和前述实施方式的非易失性存储器30的内封装部310、外封装部320、第一存储单元301、第二存储单元302、第一接口303、第二接口304、控制单元305、第三接口306相同。

52.电源管理单元407设置在外封装部420之内,优选地处于内封装部410之外。电源管理单元407与第一存储单元401、第二存储单元402以及控制单元405分别建立有电性连接,用于分别给第一存储单元401、第二存储单元402以及控制单元405提供适当的工作电压。

53.本实施方式的非易失性存储器40整合有电源管理单元407,有利于更精确地控制内部工作电压。

54.请参阅图5,其中示出了图4所示的非易失性存储器40安装在嵌入式系统中的电路示意图。

55.如图5所示,第一存储单元401通过数据线(sdl)和控制线(scl)与第一接口403连接,同时嵌入式系统的供电电压(vcc)分别通过上拉电阻(r)提供给数据线(sdl)和控制线(scl),这样第一存储单元401就可以由供电电压(vcc)进行启动。控制单元405通过主设备数据输出线(sdo)、主设备数据输入线(sdi)线和时钟信号线(clk)与第二接口404连接,这样控制单元405就能够和第二存储单元402建立通信,在第二存储单元402中读写数据。第三接口406还通过电源线(vbus)、接地线(gnd)、差分信号线(d+、d-)与嵌入式系统的主机连接,使得主机能够通过第三接口406与控制单元405进行通信。

56.这样,在嵌入式系统开始工作后,本实施方式的非易失性存储器40就能够在嵌入式系统中同时提供两种不同类型的存储器的功能,同时只占用基本上相当于传统的一种存储器的体积。

57.如上所述,本技术的各个实施方式提供的非易失性存储器都能够把两种不同类型的存储器封装在同一个封装结构内,并且能够通过例如bga结构使封装结构的整体尺寸不大于(或者不明显大于)仅封装一种类型的存储器的传统存储器封装结构。这样,所述非易失性存储器就能够同时提供两种不同类型的存储器的功能,而且占用的体积并不大于(或者不明显大于)一个仅能提供一种存储器功能的传统存储器,不会影响到小型化的设计需求。因此,本技术的实施方式提供的非易失性存储器能够解决嵌入式系统中一方面需要同时使用多种不同类型的存储器,另一方面又需要顾及小型化设计的技术问题。

58.以上所述仅为本技术的部分实施例,并非因此限制本技术的保护范围,凡是利用

本技术说明书及附图内容所作的等效装置或等效流程变换,或直接或间接运用在其他相关的技术领域,均同理包括在本技术的专利保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1