一种基于双边缘连接器的COMe模块的制作方法

一种基于双边缘连接器的come模块

技术领域

1.本发明属于come模块技术领域,尤其是涉及一种基于基于双边缘连接器的come模块。

背景技术:

2.com express标准是在2005年首次发布,由pci工业计算机制造商协会(picmg)和它寻求几种不同的目标应用程序提供了标准化的模块接口。com express是模块计算机(com)的外形尺寸,是一种高度集成且紧凑的pc,可以像集成电路组件一样用于设计应用。每个com express模块都集成了核心cpu和内存功能,通用i/o、usb、音频、图形(peg)和以太网。所有i/o信号都映射到模块底部的两个高密度薄型连接器。come模块插入通常针对应用定制的底板。随着时间的流逝,可以将com express夹层模块升级到较新的,向后兼容的版本。com express通常用于工业,军事/航空航天,医疗,运输,物联网和双边缘连接器通用计算嵌入式应用程序。

3.come连接器定义成本昂贵,实际测试中由于连接器本身信号阻抗不连续,导致整个高速信号链路阻抗不匹配,高速信号插损较大。最高速率只能支持到10gbps,同时信号定义不能满足新的需求。

技术实现要素:

4.本发明旨在解决上述技术问题,提供一种基于双边缘连接器的come模块。

5.为了达到上述目的,本发明采用如下技术方案:一种基于双边缘连接器的come模块,come模块安装在扣板上并插入针对应用定制的底板,come模块包括cpu、cpld和双边缘连接器,所述双边缘连接器包括第一双边缘连接器;所述第一双边缘连接器包括第一边缘连接器a和第一边缘连接器b,所述第一边缘连接器a包括60位接口a1

‑

a60,所述第一边缘连接器b包括60位接口b1

‑

b60;接口a1

‑

a4为供电接口,每个接口接12v输入电压,每一pin的电流为0.5a;接口a5、a11、a17、a20、a21、a24、a25、a28、a29、a32、a33、a36、a37、a40、a41、a44、a45、a48、a49、a52、a53、a56、a57、a60为电源接地接口;接口a6为rsv接口,接口a6从逻辑电路连出,作为通用接口,由软件写高或写低;接口a7、a9为串口发送接口,分别连接cpu的两个串口发送引脚,然后经过逻辑电路连接到底板;接口a8、a10为串口接收接口,分别连接cpu的两个串口接收引脚;接口a12为i2c总线的数据信号线sda接口,连接cpu的smb_host数据引脚;接口a13为i2c总线的数据信号线scl接口,连接cpu的smb_host时钟引脚;接口a14为mdc的通用接口或mdc的串行吉比特媒体独立接口或mdc的局域网接口或i2c总线的数据信号线scl的局域网接口,mdc的通用接口从逻辑电路连出,用于配置cpu管理不了的端口物理层phy和开关switch,mdc的串行吉比特媒体独立接口从端口物理层phy连出,配合端口物理层phy的串行吉比特媒体独立接口使用;接口a15为mdio的通用接口或mdio的串行吉比特媒体独立接口或mdio的局域网接口或i2c总线的数据信号线sda的局域网接口,mdio的通用接口从逻辑电

路连出,用于配置cpu管理不了的端口物理层phy和开关switch,mdio的串行吉比特媒体独立接口从端口物理层phy连出,配合端口物理层phy的串行吉比特媒体独立接口使用;接口a16为复位接口,从逻辑电路连出,使扣板给底板的全局复位信号;接口a18、a19为pcie的时钟正极接口和pcie的时钟负极接口,用于输出cpu给底板的pcie同源时钟,扣板直流耦合无电容,采用hcsl电平;接口a22、a23、接口a26、a27、接口a30、a31为三组usb正极数据接口和usb负极数据接口,其中接口a22、a23用于接收usb2.0信号,接口a26、a27、接口a30、a31用于接收usb3.0信号;接口a34、a35为sata正极接收接口和sata负极接收接口,用于接收sata信号;接口a38、a39、接口a42、a43、接口a46、a47、接口a50、a51为4组pcie正极接收接口和pcie负极接收接口,用于接收pcie信号;接口a38、a38还可以作为串行吉比特媒体独立接口的rp端和rn端,串行吉比特媒体独立接口从phy连出;接口a54、a55、接口a58、a59为两组局域网接收正极接口和局域网接收负极接口;接口b1

‑

b4为供电接口,每个接口接12v输入电压,每一pin的电流为0.5b;接口b5、b9、b14、b18、b19、b22、b23、b26、b27、b30、b31、b34、b35、b38、b39、b42、b43、b46、b47、b50、b51、b54、b55、b58、b59为电源接地接口;接口b6为spi时钟接口,接口b7为spi的mosi接口,接口b8为spi的miso接口,接口b10、b11、b12为spi片选接口;接口b11、b12也可以做为通用接口;接口b12也可以作为局域网led灯数据接口;b13为复位电路直流输入接口,底板给扣板复位信号,扣板默认上拉;接口b15、b16为mdc接口和mdio接口,mdc接口从cpu的局域网控制器连出,用于管理cpu局域网总线上的端口物理层phy或开关switch,或者接口b15、b16为mdc的局域网接口和mdio的局域网接口,或者接口b15、b16为i2c总线的数据信号线scl的局域网接口和i2c总线的数据信号线sda的局域网接口;接口b17为pg信号使能接口,底板电源ok及扣板上电使能信号;接口b20、b21、接口b24、b25、接口b28、b29为三组usb正极数据接口和usb负极数据接口,其中接口b20、b21发送usb2.0信号,接口b24、b25、接口b28、b29发送usb3.0信号;接口b32、b33为sata正极发送接口和sata负极发送接口,用于sata发送信号;接口b36、b37、接口b40、b41、接口b44、b45、接口b48、b49为4组pcie正极接口和pcie负极接口,用于pcie发送信号;接口b36、b37还可以作为串行吉比特媒体独立接口的tp端和tn端;接口b52、b53、接口b56、b57为局域网发送正极接口和局域网发送负极接口。

6.作为优选,所述双边缘连接器还包括第二双边缘连接器,所述第二双边缘连接器包括第二边缘连接器c和第二边缘连接器d;所述第二边缘连接器c包括60位接口c1

‑

c60,所述第二边缘连接器d包括60位接口d1

‑

d60;接口c1

‑

c5为供电接口,每个接口接12v输入电压,每一pin的电流为0.5a;接口c6、c10、c13、c16、c17、c20、c21、c24、c25、c28、c29、c32、c33、c36、c37、c40、c41、c44、c45、c48、c49、c52、c53、c56、c57、c60为电源接地接口;接口c7为bat供电接口,用于给cpu内部的rtc供电,或者接口c7作为通用接口;接口c8、c11为mdc的局域网接口,或者接口c8、c11作为i2c总线的数据信号线scl的局域网接口,或者接口c8、c11作为通用接口;接口c9、c12为mdio的局域网接口,或者接口c9、c12作为i2c总线的数据信号线sda的局域网接口,或者接口c9、c12作为通用接口;接口c14、c15为一组usb正极数据接口和usb负极数据接口,用于接收usb2.0信号;接口c18、c19 为sata正极接收接口和sata负极接收接口,用于接收sata信号;接口c22、c23、接口c26、c27、接口c30、c31、接口c34、c35、接口c38、c39、接口c42、c43、接口c46、c47、接口c50、c51为8组pcie正极接收接口和pcie负极接收接口,用于接收pcie信号;

接口c54、c55、接口c58、c59为为两组局域网接收正极接口和局域网接收负极接口;接口d1

‑

d5为供电接口,每个接口接12v输入电压,每一pin的电流为0.5a;接口d6、d10、d14、d15、d18、d19、d22、d23、d26、d27、d30、d31、d34、d35、d38、d39、d42、d43、d46、d47、d50、d51、d54、d55、d58、d59为电源接地接口;接口d7为rsv接口,或者d7作为cpu的低设备复位信号pltrst接口;接口d8、d9、d11、d12为bmc串行外设接口,分别为bmc串行外设时钟接口、bmc串行外设片选信号接口、bmc串行外设miso接口、bmc串行外设mosi接口;接口d13为电源按钮接口,或者d13作为通用接口;接口d16、d17为sata正极发送接口和sata发送接收接口,用于sata发送信号;接口d20、d21、接口d24、d25、接口d28、d29、接口d32、d33、接口d36、d37、接口d40、d41、接口d44、d45、接口d48、d49为8组pcie正极接口和pcie负极接口,用于pcie发送信号;接口d52、d53、接口d56、d57为局域网发送正极接口和局域网发送负极接口;接口d60为m.2硬盘使用的sus时钟接口,或者接口d60作为通用接口。

7.作为优选,所述双边缘连接器还包括第三双边缘连接器,所述第三双边缘连接器包括第三边缘连接器e和第三边缘连接器f;所述第三边缘连接器e包括60位接口e1

‑

e60,所述第三边缘连接器f包括60位接口f1

‑

f60;接口e1

‑

e7为供电接口,每个接口接12v输入电压,每一pin的电流为0.5a;接口e8、e9、e12、e16、e20、e21、e24、e25、e28、e29、e32、e33、e36、e37、e40、e41、e44、e45、e48、e49、e52、e53、e56、e57、e60为电源接地接口;接口e10、e11为bmc升级bios的串行外设接口,分别为bmc升级bios的串行外设mosi接口、bmc升级bios的串行外设时钟接口,bmc做主,spiflash做从;接口e13、e14为i2c总线的bmc数据信号线scl接口、i2c总线的bmc数据信号线sda接口;接口e15为i2c总线的bmc数据信号线提醒接口,或者接口e15作为通用接口,或者接口e15作为bmc输入接口;接口e17为lpc总线的serirq串行中断接口,lpc总线用于连接cpu和cpld,或者接口e17作为epsi的片选信号接口;接口e18作为epsi的复位接口,或者作为通用接口;接口e19作为lpc总线的时钟接口,或者作为epsi的时钟接口;接口e22、e23、e26、e27为rsv接口,或者接口e22作为1v05电源供电接口;接口e30、e31、接口e34、e35、接口e38、e39、接口e42、e43、接口e46、e47、接口e50、e51、接口e54、e55、接口e58、e59为8组serdes接收正极接口和serdes接收负极接口;接口f1

‑

f7为供电接口,每个接口接12v输入电压,每一pin的电流为0.5a;接口f8、f9、f12、f19、f22、f23、f26、f27、f30、f31、f34、f35、f38、f39、f42、f43、f46、f47、f50、f51、f54、f55、f58、f59为电源接地接口;接口f10、f11为bmc升级bios的串行外设miso接口、bmc升级bios的串行外设片选信号接口,bmc做主,spiflash做从;接口f13、f14、f15、f16为lpc总线的ad接口,或者接口f13、f14、f15、f16作为espi的io接口;接口f17为lpc总线的数据帧接口,或者接口f17作为espi的片选接口;接口f18为bmc的通用接口;接口f20、f21为i2c总线的数据信号线scl的cpu的me接口和i2c总线的数据信号线sda的cpu的me接口;接口f24、f25为rsv接口;接口f28、f29、接口f32、f33、接口f36、f37、接口f40、f41、接口f44、f45、接口f48、f49、接口f52、f53、接口f56、f57为8组serdes发送正极接口和serdes发送负极接口;接口f60为peci接口,或者接口f60作为通用接口。

8.采用上述技术方案后,本发明具有如下优点:本发明通过双边缘连接器的设置,在靠近数据源头的网络边缘侧,设置融合网络、计算、存储、应用核心能力的分布式开放平台,就近提供边缘智能服务,满足行业数字化在

敏捷联接、实时业务、数据优化、应用智能、安全与隐私保护等方面的关键需求。它可以作为联接物理和数字世界的桥梁,使能智能资产、智能网关、智能系统和智能服务。

9.其次,双边缘连接器提供bmc接口,bmc需在底板实现;提供8xpcie*1或4x pcie*2 或2xpcie*4或1xpcie*8接口,支持pcie v3.1协议;提供4路sgmii/kr接口,最高支持10g;提供2路uart接口;提供2路sata 3.0接口;提供3路usb2.0接口,2路usb3.0接口;提供一路lpc接口到底板;提供1路spi接口,访问底板逻辑寄存器;提供1路i2c接口到底板;提供一路mdc/mdio接口到底板;底板通过串行中断信号上报中断信号给扣板;提供1路100m pcie时钟到底板;提供单板运行状态、电压状态监控功能;单板支持ict测试;单板支持jtag测试。

10.因此,本基于双边缘连接器的come模块,显著降低了连接器成本,解决了come连接器阻抗不匹配的问题,可同封装升级到25gbps,pcb扩展能力强,信号定义扩展性强,可满足产品升级需求。

附图说明

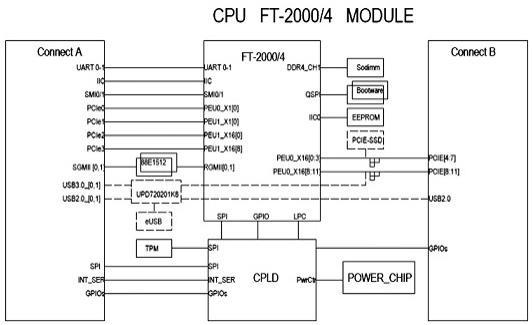

11.图1为come模块的结构示意图。

具体实施方式

12.以下结合附图及具体实施例,对本发明作进一步的详细说明。

13.一种基于双边缘连接器的come模块,come模块安装在扣板上并插入针对应用定制的底板,come模块包括cpu、cpld和双边缘连接器,所述双边缘连接器包括第一双边缘连接器、第二双边缘连接器、第三双边缘连接器。

14.所述第一双边缘连接器包括第一边缘连接器a和第一边缘连接器b,所述第一边缘连接器a包括60位接口a1

‑

a60,所述第一边缘连接器b包括60位接口b1

‑

b60;所述第二双边缘连接器包括第二边缘连接器c和第二边缘连接器d,所述第二边缘连接器c包括60位接口c1

‑

c60,所述第二边缘连接器d包括60位接口d1

‑

d60;所述第三双边缘连接器包括第三边缘连接器e和第三边缘连接器f,所述第三边缘连接器e包括60位接口e1

‑

e60,所述第三边缘连接器f包括60位接口f1

‑

f60。

15.接口a1

‑

a4为供电接口,每个接口接12v输入电压,每一pin的电流为0.5a;接口a5、a11、a17、a20、a21、a24、a25、a28、a29、a32、a33、a36、a37、a40、a41、a44、a45、a48、a49、a52、a53、a56、a57、a60为电源接地接口;接口a6为rsv接口,rsv接口为特定的程序/线程所调用的保留接口,接口a6从逻辑电路连出,作为通用接口,由软件写高或写低;接口a7、a9为串口发送接口,分别连接cpu的两个串口发送引脚,然后经过逻辑电路连接到底板;接口a8、a10为串口接收接口,分别连接cpu的两个串口接收引脚;接口a12为i2c总线的数据信号线sda接口,连接cpu的smb_host数据引脚;接口a13为i2c总线的数据信号线scl接口,连接cpu的smb_host时钟引脚;接口a14为mdc的通用接口或mdc的串行吉比特媒体独立接口或mdc的局域网接口或i2c总线的数据信号线scl的局域网接口,mdc的通用接口从逻辑电路连出,用于配置cpu管理不了的端口物理层phy和开关switch,mdc的串行吉比特媒体独立接口从端口物理层phy连出,配合端口物理层phy的串行吉比特媒体独立接口使用;接口a15为mdio的通用接口或mdio的串行吉比特媒体独立接口或mdio的局域网接口或i2c总线的数据信号线sda的局域网接口,mdio的通用接口从逻辑电路连出,用于配置cpu管理不了的端口物理层

phy和开关switch,mdio的串行吉比特媒体独立接口从端口物理层phy连出,配合端口物理层phy的串行吉比特媒体独立接口使用;接口a16为复位接口,从逻辑电路连出,使扣板给底板的全局复位信号;接口a18、a19为pcie的时钟正极接口和pcie的时钟负极接口,用于输出cpu给底板的pcie同源时钟,扣板直流耦合无电容,采用hcsl电平;接口a22、a23、接口a26、a27、接口a30、a31为三组usb正极数据接口和usb负极数据接口,其中接口a22、a23用于接收usb2.0信号,接口a26、a27、接口a30、a31用于接收usb3.0信号;接口a34、a35为sata正极接收接口和sata负极接收接口,用于接收sata信号;接口a38、a39、接口a42、a43、接口a46、a47、接口a50、a51为4组pcie正极接收接口和pcie负极接收接口,用于接收pcie信号;接口a38、a38还可以作为串行吉比特媒体独立接口的rp端和rn端,串行吉比特媒体独立接口从phy连出;接口a54、a55、接口a58、a59为两组局域网接收正极接口和局域网接收负极接口;接口b1

‑

b4为供电接口,每个接口接12v输入电压,每一pin的电流为0.5b;接口b5、b9、b14、b18、b19、b22、b23、b26、b27、b30、b31、b34、b35、b38、b39、b42、b43、b46、b47、b50、b51、b54、b55、b58、b59为电源接地接口;接口b6为spi时钟接口,接口b7为spi的mosi接口,接口b8为spi的miso接口,接口b10、b11、b12为spi片选接口;接口b11、b12也可以做为通用接口;接口b12也可以作为局域网led灯数据接口;b13为复位电路直流输入接口,底板给扣板复位信号,扣板默认上拉;接口b15、b16为mdc接口和mdio接口,mdc接口从cpu的局域网控制器连出,用于管理cpu局域网总线上的端口物理层phy或开关switch,或者接口b15、b16为mdc的局域网接口和mdio的局域网接口,或者接口b15、b16为i2c总线的数据信号线scl的局域网接口和i2c总线的数据信号线sda的局域网接口;接口b17为pg信号使能接口,底板电源ok及扣板上电使能信号;接口b20、b21、接口b24、b25、接口b28、b29为三组usb正极数据接口和usb负极数据接口,其中接口b20、b21发送usb2.0信号,接口b24、b25、接口b28、b29发送usb3.0信号;接口b32、b33为sata正极发送接口和sata负极发送接口,用于sata发送信号;接口b36、b37、接口b40、b41、接口b44、b45、接口b48、b49为4组pcie正极接口和pcie负极接口,用于pcie发送信号;接口b36、b37还可以作为串行吉比特媒体独立接口的tp端和tn端;接口b52、b53、接口b56、b57为局域网发送正极接口和局域网发送负极接口。

16.接口c1

‑

c5为供电接口,每个接口接12v输入电压,每一pin的电流为0.5a;接口c6、c10、c13、c16、c17、c20、c21、c24、c25、c28、c29、c32、c33、c36、c37、c40、c41、c44、c45、c48、c49、c52、c53、c56、c57、c60为电源接地接口;接口c7为bat供电接口,用于给cpu内部的rtc供电,或者接口c7作为通用接口;接口c8、c11为mdc的局域网接口,或者接口c8、c11作为i2c总线的数据信号线scl的局域网接口,或者接口c8、c11作为通用接口;接口c9、c12为mdio的局域网接口,或者接口c9、c12作为i2c总线的数据信号线sda的局域网接口,或者接口c9、c12作为通用接口;接口c14、c15为一组usb正极数据接口和usb负极数据接口,用于接收usb2.0信号;接口c18、c19 为sata正极接收接口和sata负极接收接口,用于接收sata信号;接口c22、c23、接口c26、c27、接口c30、c31、接口c34、c35、接口c38、c39、接口c42、c43、接口c46、c47、接口c50、c51为8组pcie正极接收接口和pcie负极接收接口,用于接收pcie信号;接口c54、c55、接口c58、c59为为两组局域网接收正极接口和局域网接收负极接口;接口d1

‑

d5为供电接口,每个接口接12v输入电压,每一pin的电流为0.5a;接口d6、d10、d14、d15、d18、d19、d22、d23、d26、d27、d30、d31、d34、d35、d38、d39、d42、d43、d46、d47、d50、d51、d54、d55、d58、d59为电源接地接口;接口d7为rsv接口,或者d7作为cpu的低设备复

位信号pltrst接口;接口d8、d9、d11、d12为bmc串行外设接口,分别为bmc串行外设时钟接口、bmc串行外设片选信号接口、bmc串行外设miso接口、bmc串行外设mosi接口;接口d13为电源按钮接口,或者d13作为通用接口;接口d16、d17为sata正极发送接口和sata发送接收接口,用于sata发送信号;接口d20、d21、接口d24、d25、接口d28、d29、接口d32、d33、接口d36、d37、接口d40、d41、接口d44、d45、接口d48、d49为8组pcie正极接口和pcie负极接口,用于pcie发送信号;接口d52、d53、接口d56、d57为局域网发送正极接口和局域网发送负极接口;接口d60为m.2硬盘使用的sus时钟接口,或者接口d60作为通用接口。

17.接口e1

‑

e7为供电接口,每个接口接12v输入电压,每一pin的电流为0.5a;接口e8、e9、e12、e16、e20、e21、e24、e25、e28、e29、e32、e33、e36、e37、e40、e41、e44、e45、e48、e49、e52、e53、e56、e57、e60为电源接地接口;接口e10、e11为bmc升级bios的串行外设接口,分别为bmc升级bios的串行外设mosi接口、bmc升级bios的串行外设时钟接口,bmc做主,spiflash做从;接口e13、e14为i2c总线的bmc数据信号线scl接口、i2c总线的bmc数据信号线sda接口;接口e15为i2c总线的bmc数据信号线提醒接口,或者接口e15作为通用接口,或者接口e15作为bmc输入接口;接口e17为lpc总线的serirq串行中断接口,lpc总线用于连接cpu和cpld,或者接口e17作为epsi的片选信号接口;接口e18作为epsi的复位接口,或者作为通用接口;接口e19作为lpc总线的时钟接口,或者作为epsi的时钟接口;接口e22、e23、e26、e27为rsv接口,或者接口e22作为1v05电源供电接口;接口e30、e31、接口e34、e35、接口e38、e39、接口e42、e43、接口e46、e47、接口e50、e51、接口e54、e55、接口e58、e59为8组serdes接收正极接口和serdes接收负极接口;接口f1

‑

f7为供电接口,每个接口接12v输入电压,每一pin的电流为0.5a;接口f8、f9、f12、f19、f22、f23、f26、f27、f30、f31、f34、f35、f38、f39、f42、f43、f46、f47、f50、f51、f54、f55、f58、f59为电源接地接口;接口f10、f11为bmc升级bios的串行外设miso接口、bmc升级bios的串行外设片选信号接口,bmc做主,spiflash做从;接口f13、f14、f15、f16为lpc总线的ad接口,或者接口f13、f14、f15、f16作为espi的io接口;接口f17为lpc总线的数据帧接口,或者接口f17作为espi的片选接口;接口f18为bmc的通用接口;接口f20、f21为i2c总线的数据信号线scl的cpu的me接口和i2c总线的数据信号线sda的cpu的me接口;接口f24、f25为rsv接口;接口f28、f29、接口f32、f33、接口f36、f37、接口f40、f41、接口f44、f45、接口f48、f49、接口f52、f53、接口f56、f57为8组serdes发送正极接口和serdes发送负极接口;接口f60为peci接口,或者接口f60作为通用接口。

18.如图1所示,come模块使用第一双边缘连接器的结构示意图;或者,come模块可以使用第一双边缘连接器和第二双边缘连接器;或者,come模块可以使用第一双边缘连接器、第二双边缘连接器和第三双边缘连接器。使用第一双边缘连接器的电流最大支持4a,使用第一双边缘连接器、第二双边缘连接器的电流最大支持9a,使用第一双边缘连接器、第二双边缘连接器、第三双边缘连接器的电流最大支持14a。

19.双边缘连接器的通用接口模块必须严格按照进行硬件设计,以保证新扣板与各产品底板的兼容性和各个通用扣板之间的可替换性。

20.双边缘连接器提供bmc接口,bmc需在底板实现;提供8xpcie*1或4x pcie*2 或2xpcie*4或1xpcie*8接口,支持pcie v3.1协议;提供4路sgmii/kr接口,最高支持10g;提供2路uart接口;提供2路sata 3.0接口;提供3路usb2.0接口,2路usb3.0接口;提供一路lpc接

口到底板;提供1路spi接口,访问底板逻辑寄存器;提供1路i2c接口到底板;提供一路mdc/mdio接口到底板;底板通过串行中断信号上报中断信号给扣板;提供1路100m pcie时钟到底板;提供单板运行状态、电压状态监控功能;单板支持ict测试;单板支持jtag测试。

21.除上述优选实施例外,本发明还有其他的实施方式,本领域技术人员可以根据本发明作出各种改变和变形,只要不脱离本发明的精神,均应属于本发明所附权利要求所定义的范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1