神经元网络单元、卷积运算模块以及卷积神经网络

1.本发明涉及集成电路设计领域,尤其涉及一种神经元网络单元、卷积运算模块以及卷积神经网络。

背景技术:

2.随着大数据时代的发展,人工智能已经成为一个非常重要的学科领域,神经网络专用芯片则是计算系统高效完成神经网络计算的重要硬件工具。传统计算架构采用计算和存储分离的冯诺依曼体系,在大数据趋势下,冯诺依曼体系结构中内存带宽和内存功耗已经开始主导计算带宽和能量。其中很大一部分功耗被花费在内存和计算单元的数据搬运上。以存储器为主导的存内计算,通过神经网络算法与存储硬件架构的结合,非常大程度的降低了数据搬运带来的巨大时间和功耗开销。

3.现有的卷积神经网络存算一体存储器(cim sram),沿用了传统的sram的字线和位线架构,因此在进行数据输入时,每一行字线接收的数据均是同一组输入数据。虽然对于同一组数据进行卷积运算时可以使用不同的卷积核进行乘加运算,但是基于目前简单的卷积神经网络算法,对于同一组卷积窗口的数据,最多使用16

‑

20组卷积核,因此对于sram阵列来说,仅使用16

‑

20列位线进行操作对剩下的阵列部分造成了资源浪费。

技术实现要素:

4.本发明所要解决的技术问题是,提供一种神经元网络单元、卷积运算模块以及卷积神经网络,提高阵列单元资源利用率并降低了功耗。

5.为了解决上述问题,本发明提供了一种神经元网络单元,包括静态随机存储单元、正向读出隔离支路、以及反向读出隔离支路;所述静态随机存储单元包括电学串联的第一传输晶体管和第二传输晶体管,以及并联在第一和第二传输晶体管之间的两个对置互锁的第一和第二反相器,所述正向读出隔离支路连接至第一传输晶体管与两个对置互锁的反相器之间,用于根据静态随机存储单元存储的控制信号,将一外部输入的数字电压转化为模拟电流输出;所述反向读出隔离支路连接至第二传输晶体管与两个对置互锁的反相器之间,用于根据静态随机存储单元存储的控制信号,将一外部输入的数字电压转化为模拟电流输出。

6.可选的,所述正向读隔离支路包括串联的第一读出晶体管和第二读出晶体管;第一读出晶体管的栅极连接至第一传输晶体管与两个对置互锁的反相器之间,作为正向读隔离支路的控制端,第一读出晶体管的漏/源极接工作电压;第二读出晶体管的栅极作为外部输入端,第二读出晶体管的源/漏极作为正向读出隔离支路的输出端。

7.可选的,所述反向读隔离支路包括串联的第三读出晶体管和第四读出晶体管;第三读出晶体管的栅极连接至第二传输晶体管与两个对置互锁的反相器之间,作为反向读隔离支路的控制端,第三读出晶体管的漏/源极接地;第四读出晶体管的栅极作为外部输入端,第四读出晶体管的源/漏极作为反向读出隔离支路的输出端。

8.本发明还提供了一种卷积运算模块,所述模块包括卷积运算子块和脉冲频率量化单元;所述卷积运算子块包括n

×

n个上述的神经元网络单元所组成的阵列,n为正整数,其中:神经元网络单元的第一和第二传输晶体管连接阵列的写字线,第一传输晶体管的漏/源极和第二传输晶体管源/漏极分别连接位线和反向位线,正向隔离支路的外部输入端连接行字线,反向隔离支路的外部输入端连接列字线,正向隔离支路的输出端连接行电流输出,反向隔离支路的输出端连接列电流输出;所述脉冲频率量化单元与所述卷积运算子块的输出端连接,将卷积运算子块中的电流输出转化为脉冲信号进行脉冲频率计数,进而转换成多比特数字输出。

9.可选的,所述脉冲频率量化单元包括串联的放大器、比较器、以及计数器:所述放大器与一积分电容并联,并与比较器串联,作为脉冲频率量化单元的输入端;所述比较器的输出端进一步通过一放电控制开关连接至积分电容的两端,所述放电控制开关用于在所述比较器输出高电平时对积分电容进行放电;上述积分电容被模拟电流输入充电后经放大器放大,引起比较器的脉冲式输出,从而将电流值等效转化为脉冲频率;所述计数器与所述比较器串联,对脉冲个数进行计数进而形成多比特数字输出。

10.本发明还提供了一种卷积神经网络,包括n

×

n个上述的卷积运算模块所组成的阵列,n为正整数。

11.本发明每一行字线接收两组不同的数据,分别进行卷积运算,对于同一组卷积窗口的数据可以使用更多组的卷积核,避免了资源浪费。

附图说明

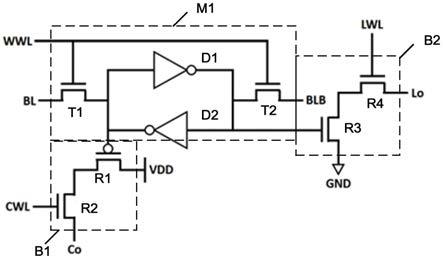

12.附图1所示是本发明一具体实施方式提供的一种神经元网络单元的电路结构示意图。

13.附图2所示是本发明一具体实施方式所述的卷积运算模块中卷积运算子块的电路结构示意图。

14.附图3所示是本发明一具体实施方式所述的卷积运算模块中的脉冲量化单元的电路结构示意图。

具体实施方式

15.下面结合附图对本发明提供的静态随机存储器单元、卷积运算模块以及卷积神经网络的具体实施方式做详细说明。

16.以下具体实施方式中对晶体管的源极和漏极的连接方式择一叙述,应当指出的是,在其他的具体实方式中,在不影响实际电学功能的前提下,晶体管的源极和漏极可以等效替换。

17.附图1所示是本发明一具体实施方式提供的一种神经元网络单元的电路结构示意图,包括静态随机存储单元m1、正向读出隔离支路b1、以及反向读出隔离支路b2。静态随机存储单元m1为6t结构,包括电学串联的第一传输晶体管t1和第二传输晶体管t2,以及并联在第一传输晶体管t1和第二传输晶体管t2之间的两个对置互锁的第一反相器d1和第二反相器d2。

18.在本具体实施方式中,所述正向读出隔离支路b1包括串联的第一读出晶体管r1和

第二读出晶体管r2;第一读出晶体管r1的栅极连接至第一传输晶体管t1与两个对置互锁的反相器之间,作为正向读隔离支路的控制端,第一读出晶体管r1的漏极接工作电压vdd;第二晶读出体管r2的栅极作为外部输入端,第二读出晶体管r2的源极作为正向读出隔离支路的输出端。所述正向读出隔离支路b1连接至第一传输晶体管与两个对置互锁的反相器之间,用于根据静态随机存储单元m1存储的控制信号,将一外部输入的数字电压转化为模拟电流输出。

19.在本具体实施方式中,所述反向读隔离支路b2包括串联的第三读出晶体管r3和第四读出晶体管r4。第三读出晶体管r3的栅极连接至第二传输晶体t2管与两个对置互锁的反相器之间,作为反向读隔离支路的控制端,第三读出晶体管r3的漏极接地。第四传输晶体管r4的栅极作为外部输入端,第四读出晶体管r4的源极作为反向读出隔离支路的输出端。所述反向读出隔离支路连接至第二传输晶体管t2与两个对置互锁的反相器之间,用于根据静态随机存储单元m1存储的控制信号,将一外部输入的数字电压转化为模拟电流输出。

20.接下来给出本发明的卷积运算模块的具体实施方式。所述模块包括卷积运算子块和脉冲频率量化单元。附图2所示是本发明一具体实施方式所述的卷积运算模块中卷积运算子块的电路结构示意图。所述卷积运算子块包括n

×

n个上述的神经元网络单元所组成的阵列。在本具体实施方式中,以3

×

3个神经元网络单元c11~c33为例进行叙述。其中,神经元网络单元的第一传输晶体管t1和第二传输晶体管t2连接阵列的写字线wwl,第一传输晶体管t1的漏极和第二传输晶体管源极分别连接位线bl和反向位线blb,正向隔离支路的外部输入端连接行字线lwl,反向隔离支路的外部输入端连接列字线cwl,正向隔离支路的输出端连接行电流输出lo,反向隔离支路的输出端连接列电流输出co。该阵列可实现在三个周期内3

×

3卷积核对4

×

8输入矩阵进行卷积运算。

21.附图3所示是本发明一具体实施方式所述的卷积运算模块中的脉冲量化单元的电路结构示意图。所述脉冲频率量化单元与所述卷积运算子块的输出端连接,将卷积运算子块中的电流输出转化为脉冲信号进行脉冲频率计数,进而转换成多比特数字输出。作为上述的一种具体实施方式,如附图2所示,所述脉冲频率量化单元包括串联的放大器21、比较器22、以及计数器23。所述放大器21与一积分电容c并联,并与比较器22串联,作为脉冲频率量化单元的输入端。所述比较器22的输出端进一步通过一放电控制开关k连接至积分电容c的两端,所述放电控制开关k用于在所述比较器22输出高电平1时对积分电容c进行放电;上述积分电容c被模拟电流输入充电后经放大器21放大,引起比较器22的脉冲式输出,从而将电流值等效转化为脉冲频率。具体的说,比较器22的翻转输出作为积分电容c的放电信号,每当积分电容c被模拟电流输入充电到比较器22翻转电压,比较器22输出进行0

→

1翻转,当比较器22输出为1时,积分电容c放电,比较器22输出1

→

0,进而比较器22形成脉冲输出,当模拟输入电流越大,该脉冲形成的频率越快。所述计数器23与所述比较器22串联,对脉冲个数进行计数进而形成多比特数字输出。

22.将上述附图2和附图3构成的包括包括卷积运算子块和脉冲频率量化单元的卷积运算模块的组成n

×

n的阵列,即构成一卷积神经网络,可以进行卷积神经网络的加速计算。

23.以上所述仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1