一种卷积计算中4bit特征图的存储和解析方法与流程

1.本发明涉及图像处理技术领域,特别涉及一种卷积计算中4bit特征图的存储和解析方法。

背景技术:

2.集成电路技术现在越来越成为技术发展的焦点,很多芯片厂商也都开发自己的芯片。而在芯片应用中,在各自的芯片设计中也会产生各自的需求问题。例如,北京君正集成电路股份有限公司生产的芯片,目前市场大部分的芯片只支持的8位数据运算,对应的存储最小单位为8比特存储,不能直接支持4比特的存储,如北京君正的t30,t31型号的芯片。存放4比特数据,以8位存储数据,也就是一个字节,使用数据时最小单位也是一个字节,占用更大的存储空间,加载数据时间增加,使得在整个卷积计算的时间增加。

3.另外,现有技术中的常用术语如下:

4.1、特征图:输入数据通过卷积计算后得到的结果称之为特征图,数据通过全连接后生成的结果也称为特征图。特征图大小一般表示为长

×

宽

×

深度,或1

×

深度。深度也被称为通道数。

技术实现要素:

5.为了解决上述现有技术中的问题,本技术的目的在于:降低占用的存储空间。加载到二级缓存中的特征图数据更多,缓解数据传输中导致的等待问题。特别是,能适应例如北京君正的t30,t31型号类型的芯片指令的需要,根据适用于t30,t31型号的芯片上运行卷积的效率进行设计存储方式。

6.具体地,本发明提供一种卷积计算中4b it特征图的存储和解析方法,所述方法包括:

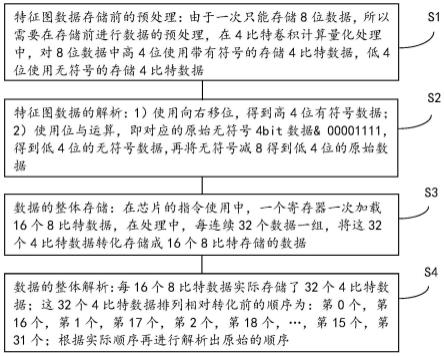

7.s1,特征图数据存储前的预处理:

8.由于一次只能存储8位数据,所以需要在存储前进行数据的预处理,在4比特卷积计算量化处理中,对8位数据中高4位使用带有符号的存储4比特数据,低4位使用无符号的存储4比特数据;

9.s2,特征图数据的解析:

10.1)使用向右移位,得到高4位有符号数据;

11.2)使用位与运算,即对应的原始无符号4bit数据&00001111,得到低4位的无符号数据,再将无符号减8得到低4位的原始数据;

12.s3,数据的整体存储:

13.在芯片的指令使用中,一个寄存器一次加载16个8比特数据,在处理中,每连续32个数据一组,将这32个4比特数据转化存储成16个8比特存储的数据;

14.s4,数据的整体解析:

15.每16个8比特数据实际存储了32个4比特数据;这32个4比特数据排列相对转化前

的顺序为:第0个,第16个,第1个,第17个,第2个,第18个,

…

,第15个,第31个;根据实际顺序再进行解析出原始的顺序:

16.首先将数据加载到寄存器vrs中,再通过右移得到高4位有符号数据,结果存到寄存器vrd0中;

17.接着对vrs通过位与运算,得到低4位的无符号数据,再将无符号减8得到低4位的原始数据,结果存到寄存器vrd1中;

18.vrd0存储的顺序为:第0个,第1个,第2个,

…

,第15个;vrd1存储的顺序为:第16个,第17个,第18个,

…

,第31个。

19.所述步骤s1中,在4比特卷积计算量化处理中,把卷积结果进行量化到无符号4比特数据,根据实际需要再进一步处理成有符号4比特数据;每一层输入使用4比特有符号数据,能够直接使用有符号数据,也能够使用无符号数据,即将无符号数据减去8得到有符号数据。

20.所述步骤s1中,所述一个8位数据的存储方式包括:高4位,带有符号,即无符号4位减8后的数据,再左移位4位;低4位,无符号的8位存储,也就是不减8;然后再将这两个数使用位或运算,得到的数据即是要存储的8位的数据;设8位数据中的高4位为a,对应的原始无符号4bit数据是x,低4位为b,对应的原始无符号4比特数据是y,使用位或运算后的数据为z,公式为:

[0021][0022]

z=[(x-8)<<4]|y (0≤x≤15,0≤y≤15,x∈n,y∈n)。

[0023]

设有两个无符号4位数x=6,y=11;将a处理有符号数据为6-8=-2,再左移4位是-32;z=-32|11,得z=-21。

[0024]

数据的解析中,使用位与运算,即x&00001111,

[0025]

公式为:

[0026][0027]

设z=-21,x=-21》》4,得x=-2,y=(-21)&(0x0f),得y=11,对应的无符号结果为6,11,这个结果与原始数据a=6,b=11,z=-21完全吻合。

[0028]

所述步骤s3中,每连续32个4bit数据一组即一个8bit中存储两个4比特数据,其中前16个数据为有符号4比特数据,后16个数据为无符号4比特数据。

[0029]

设寄存器vrs0里面存储的是前16个8比特数据,寄存器vrs1里面存储的是后16个8比特数据,里面的8比特数据的有效数据只有一个4比特数据,处理后的数据用寄存器vrd表示,最后将vrd中的数据保存到ddr硬件中即可;

[0030]

将无符号4比特数据转化为有符号4比特数据,结果存储到vrs0:

[0031]

使用减法指令,输入变量vrs0、8,输出变量是vrs0,vrs0存储的是16个8比特的数据;可表示为vrd1=ingenic_sub(vrd1,8);

[0032]

移位操作,结果存储到vrs0:

[0033]

使用左移位指令,将变量vrs0里的数据进行左移动4位;可表示为vrs0=ingenic_shift_left(vrs0,4);

[0034]

将高4比特有符号数据与低4比特无符号数据相加:

[0035]

使用位或指令,输入变量vrs0、vrs1,输出变量是vrd,vrd存储的是16个8比特的数据,vrs0和vrs1存储的是16个8比特数据;可表示为vrd=ingenic_or(vrs0,vrs1)。

[0036]

所述步骤s4,进一步包括:

[0037]

对vrs移位操作,结果存储到vrd0中:

[0038]

使用右移位指令,将变量vrs0里的数据进行右移动4位;可表示为vrd0=ingenic_shift_right(vrs0,4);

[0039]

对vrs位与操作,结果存储到vrd1中:

[0040]

使用位与指令,输入变量vrs0,15,输出变量vrd1,vrd1存储的是16个8比特的数据,vrs0存储的是16个8比特数据;可表示为vrd1=ingenic_and(vrs0,15);

[0041]

将无符号4比特转化为有符号4比特数据:

[0042]

使用减法指令,输入变量vrd1、8,输出变量是vrd1;vrd1存储的是16个8比特的数据;可表示为vrd1=ingenic_sub(vrd1,8)。

[0043]

所述在芯片的指令使用中使用的芯片为具有simd指令集的芯片,适用于北京君正t30、t31型号的芯片,其中有这样的指令,8比特符号位不参与左右移位运算,但8比特符号位参与与或运算,所以仅采用高4位存储有符号4比特数据,低4位存储无符号4比特数据;常规指令8比特加法和减法运算。凡是具有这样指令功能的芯片,均可使用该方法。

[0044]

所述步骤s4进一步还包括:使用vrd0,vrd1进行卷积计算。

[0045]

由此,本技术的优势在于:提供了一种卷积计算中4bit特征图的存储和解析方法,该种方法,可以将数据存储空间缩小一倍,在数据加载过程中,极大的减少了加载时间,等效速度加快一倍,而计算量没有增加。

附图说明

[0046]

此处所说明的附图用来提供对本发明的进一步理解,构成本技术的一部分,并不构成对本发明的限定。

[0047]

图1是本发明的方法流程图。

具体实施方式

[0048]

为了能够更清楚地理解本发明的技术内容及优点,现结合附图对本发明进行进一步的详细说明。

[0049]

如图1所示,本发明涉及一种卷积计算中4bit特征图的存储和解析方法,所述方法包括:

[0050]

s1,特征图数据存储前的预处理:

[0051]

由于一次只能存储8位数据,所以需要在存储前进行数据的预处理,在4比特卷积计算量化处理中,对8位数据中高4位使用带有符号的存储4比特数据,低4位使用无符号的存储4比特数据;

[0052]

s2,特征图数据的解析:

[0053]

1)使用向右移位,得到高4位有符号数据;

[0054]

2)使用位与运算,即对应的原始无符号4bit数据&00001111,得到低4位的无符号数据,再将无符号减8得到低4位的原始数据;

[0055]

s3,数据的整体存储:

[0056]

在芯片的指令使用中,一个寄存器一次加载16个8比特数据,在处理中,每连续32个数据一组,将这32个4比特数据转化存储成16个8比特存储的数据;

[0057]

s4,数据的整体解析:

[0058]

每16个8比特数据实际存储了32个4比特数据;这32个4比特数据排列相对转化前的顺序为:第0个,第16个,第1个,第17个,第2个,第18个,

…

,第15个,第31个;根据实际顺序再进行解析出原始的顺序:

[0059]

首先将数据加载到寄存器vrs中,再通过右移得到高4位有符号数据,结果存到寄存器vrd0中;

[0060]

接着对vrs通过位与运算,得到低4位的无符号数据,再将无符号减8得到低4位的原始数据,结果存到寄存器vrd1中;

[0061]

vrd0存储的顺序为:第0个,第1个,第2个,

…

,第15个;vrd1存储的顺序为:第16个,第17个,第18个,

…

,第31个。

[0062]

具体地,本技术的具体实施例还可以描述为如下:

[0063]

1、使用要求。输入特征图通道需要是32的倍数。涉及使用的是北京君正t30、t31型号芯片相应的指令集有移位指令、减法指令、位与指令、保存数据指令。指令如下:

[0064]

a)移位指令:

[0065]

将变量里的每个元素进行移动i位。

[0066]

左移移位指令

[0067]

vrd=ingenic_shift_left(vrs,i)

[0068]

右移移位simd指令

[0069]

vrd=ingenic_shift_right(vrs,i)

[0070]

b)减法指令:

[0071]

vrd=ingenic_sub(vrs,i);

[0072]

输入变量vrs,i,输出变量是vrd。vrd存储的是16个8比特的数据,vrs存储的是16个8比特数据。i是常规变量。

[0073]

等价的运算:

[0074]

vrd0:=vrs0-i;

[0075]

vrd1:=vrs1-i;

[0076]

……

[0077]

vrd7:=vrs7-i;

[0078]

c)位与指令:

[0079]

vrd=ingenic_and(vrs,i);

[0080]

输入变量vrs,i,输出变量是vrd。vrd存储的是16个8比特的数据,vrs存储的是16个8比特数据。i是常规变量。

[0081]

等价的运算:

[0082]

vrd0:=vrs0&i;

[0083]

vrd1:=vrs1&i;

[0084]

……

[0085]

vrd7:=vrs7&i;

[0086]

d)位或指令:

[0087]

vrd=ingenic_or(vrs,i);

[0088]

输入变量vrs,i,输出变量是vrd。vrd存储的是16个8比特的数据,vrs存储的是16个8比特数据。i是常规变量。

[0089]

等价的运算:

[0090]

vrd0:=vrs0|i;

[0091]

vrd1:=vrs1|i;

[0092]

……

[0093]

vrd7:=vrs7|i;

[0094]

1、特征图数据存储前的预处理。

[0095]

在4比特卷积计算量化处理中,把卷积结果进行量化到无符号4比特数据,根据实际需要是否再进一步处理成有符号4比特数据。每一层输入使用4比特有符号数据,所以可以直接使用有符号数据,也可以使用无符号数据,将无符号数据减去8得到有符号数据。根据这种情况,对8位中高4位使用带有符号的存储4比特数据,低4位使用无符号的存储4比特数据。在t30、t31型号芯片的指令中,8比特符号位不参与左右移位运算,但8比特符号位参与“与或”运算,并且有这样的指令,所以仅可以采用高4位存储有符号4比特数据,低4位存储无符号4比特数据。由于一次只能存储8位,所以需要在存储前将数据处理好。

[0096]

一个8位数据存储方式:高4位,带有符号,即无符号4位减8后的数据,再左移位4位;低4位无符号的8位存储,也就是不减8;然后再将这两个数使用位或运算,得到的数据即是要存储的8位的数据。不妨设8位数据中的高4位为a,对应的原始无符号4bit数据是x,低4位为b,对应的原始无符号4比特数据是y,使用位或运算后的数据为z。公式为:

[0097][0098]

z=[(x-8)<<4]|y (0≤x≤15,0≤y≤15,x∈n,y∈n)。

[0099]

例如:设有两个无符号4位数x=6,y=11。将a处理有符号数据为6-8=-2,再左移4位是-32。z=-32|11,得z=-21。

[0100]

3、特征图数据的解析。

[0101]

数据的解析:

[0102]

1)使用向右移位,得到高4位有符号数据;

[0103]

2)使用位与运算(x&00001111),得到低4位的无符号数据,再将无符号减8得到低4位的原始数据。

[0104]

公式为:

[0105][0106]

例如:设z=-21。x=(-21>>4),得x=-2,y=(-21)&(0x0f),得y=11,对应的无符号结果为6,11。这个结果与1中的举例中“a=6,b=11,z=-21”完全吻合。

[0107]

4、数据的整体存储

[0108]

在北京君正t30、t31型号芯片的指令使用中,一个寄存器一次加载16个8比特数据,所以我们在处理中,每连续32个4比特数据(一个8比特数据里面只存储一个4比特数据)一组,其中前16个数据为有符号4比特数据,后16个数据为无符号4比特数据。将这32个4比特数据转化存储成16个8比特存储的数据。使用t30、t31的指令处理如下。

[0109]

设寄存器vrs0里面存储的是前16个8比特数据,寄存器vrs1里面存储的是后16个8比特数据,里面的8比特数据的有效数据只有一个4比特数据。处理后的数据用寄存器vrd表示。最后将vrd中的数据保存到ddr硬件中即可。

[0110]

将无符号4比特数据转化为有符号4比特数据,结果存储到vrs0,

[0111]

vrs0=ingenic_sub(vrs0,8);

[0112]

移位操作,结果存储到vrs0,

[0113]

vrs0=ingenic_shift_left(vrs0,4);

[0114]

将高4比特有符号数据与低4比特无符号数据进行或运算,

[0115]

vrd=ingenic_or(vrs0,vrs1);

[0116]

5、数据的整体解析

[0117]

数据的解析:

[0118]

每16个8比特数据实际存储了32个4比特数据。这32个4比特数据排列相对转化前的顺序为:第0个,第16个,第1个,第17个,第2个,第18个,

…

,第15个,第31个。根据实际顺序,再进行解析出原始的顺序。

[0119]

首先将数据加载到寄存器vrs中,再通过右移得到高4位有符号数据,结果存到寄存器vrd0中;接着对vrs通过位与运算,得到低4位的无符号数据,再将无符号减8得到低4位的原始数据,结果存到寄存器vrd1中。vrd0存储的顺序为:第0个,第1个,第2个,

…

,第15个。vrd1存储的顺序为:第16个,第17个,第18个,

…

,第31个。后面使用vrd0,vrd1进行卷积计算。

[0120]

对vrs移位操作,结果存储到vrd0中,

[0121]

vrd0=ingenic_shift_right(vrs0,4);

[0122]

对vrs位的与操作,结果存储到vrd1中,

[0123]

vrd1=ingenic_and(vrs0,15);

[0124]

将无符号4比特转化为有符号4比特数据,

[0125]

vrd1=ingenic_sub(vrd1,8);

[0126]

该种方法,可以将数据存储空间缩小一倍,在数据加载过程中,极大的减少了加载时间,等效速度加快一倍,而计算量没有增加。

[0127]

以上所述仅为本发明的优选实施例而已,并不用于限制本发明,对于本领域的技术人员来说,本发明实施例可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1