具备分组密码算法的处理器及其处理方法与流程

1.本发明有关于具备密码算法的处理器及其处理方法。

背景技术:

2.中国国家密码局发布多种密码算法,包括sm2、sm3、以及sm4

…

等密码算法,替代rsa(简写自rivest

‑

shamir

‑

adleman)、sha(简写自secure hash algorithm)、aes(advanced encryption standard)

…

等国际通用密码算法。

3.sm4密码算法为分组密码算法,应用于无线局域网产品。sm4密码算法的数据块长度、以及密钥长度都是128位。

4.在已知的技术中,都是使用多条指令集架构指令在处理器中实现分组密码算法,无法有效保护运算过程中生成的中间数据,所以安全性较差。

5.如何高效且更安全的完成sm4密码算法,为本技术领域一项重大课题。

技术实现要素:

6.为了提高安全性,本发明提供一种具备分组密码算法(sm4)的处理器及其处理方法。

7.根据本发明一种实施方式实现的处理器使用第一寄存器,储存输入密钥指针,指向输入密钥。响应指令集架构的单一条分组密码算法指令,该处理器从第一内存空间取得输入数据,基于该输入密钥对该输入数据进行分组密码算法,加密、或解密出输出数据,并将该输出数据存入第二内存空间或内部硬件存储空间。

8.该处理器根据该输入数据的一输入数据块数(number of 16

‑

byte blocks),分组该输入数据为定尺寸的多个输入数据块。该处理器对各输入数据块分别进行n轮运算,以对应各输入数据块分别产生一个输出数据块,组成该输出数据,n为整数。该处理器基于该输入密钥扩展出n个扩展密钥,使各输入数据块的不同轮运算是使用不同的扩展密钥。

9.一种实施方式中,该处理器包括密码执行单元、一组架构寄存器、储存微码的微码储存装置、以及解码器。该解码器响应该单一条分组密码算法指令,根据该微码解码出多条微指令。所述多条微指令包括定义、使用、以及且管理该组架构寄存器的内容,以及操作该密码执行单元基于该输入密钥对该输入数据进行该分组密码算法。

10.一种实施方式中,该密码执行单元包括分组密码算法加速器。所述多条微指令包括加速器操作微指令。响应该加速器操作微指令,该分组密码算法加速器为该输入数据各输入数据块分别进行n轮运算,以对应各输入数据块分别产生一个输出数据块,组成该输出数据,n为整数。

11.一种实施方式中,该分组密码算法加速器包括密钥扩展逻辑硬件、以及第一加速器内部储存空间。该密钥扩展逻辑硬件接收该输入密钥,并基于该输入密钥扩展出n个扩展密钥,使各输入数据块的不同轮运算是使用不同的扩展密钥。该第一加速器内部储存空间依照生成顺序将所述n个扩展密钥缓存成n个顺序密钥,供加密使用。

12.一种实施方式中,该分组密码算法加速器包括密钥反序转换硬件、以及第二加速器内部储存空间。该密钥反序转换硬件将该第一加速器内部储存空间储存的所述n个顺序密钥反序转换为n个反序密钥。该第二加速器内部储存空间缓存所述n个反序密钥,供解密使用。

13.一种实施方式中,该分组密码算法加速器包括一轮运算逻辑硬件、多路复用器、以及控制逻辑硬件。该多路复用器将该第一加速器内部储存空间缓存的所述n个顺序密钥、或该第二加速器内部储存空间缓存的所述n个反序密钥供应该轮运算逻辑硬件,使该轮运算逻辑硬件对各输入数据块分别进行n轮运算,分别产生对应各输入数据块的输出数据块。该控制逻辑硬件,接收控制字,并在该控制字的加解密设定位指示加密时,操作该多路复用器,将所述n个顺序密钥供应该轮运算逻辑硬件,并在该加解密设定位指示解密时,操作该多路复用器,将所述n个反序密钥供应该轮运算逻辑硬件。

14.根据本发明一种实施方式实现的处理器的处理方法,包括:响应指令集架构的单一条分组密码算法指令,从第一内存空间取得输入数据,基于输入密钥对该输入数据进行分组密码算法,加密、或解密出输出数据,并将该输出数据存入第二内存空间或内部硬件存储空间。

15.通过本发明提供的具备分组密码算法(sm4)的处理器及其处理方法,只需使用一条指令集架构指令就可以实现分组密码算法,可将在实现分组密码算法的过程中生成的中间数据储存在处理器内部硬件存储空间中,使得在处理器外部无法访问这些中间数据,因而极大地提高了安全性。

16.下文特举实施例,并配合附图,详细说明本发明内容。

附图说明

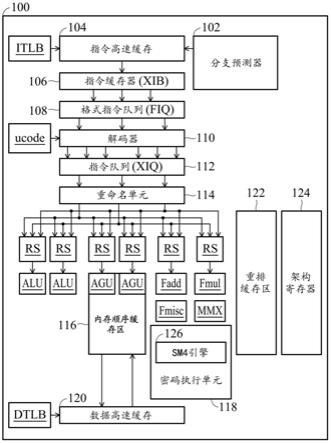

17.图1为方块图,根据本发明一种实施方式图解一处理器100;

18.图2a至图2c根据本发明不同实施方式图解isa的sm4密码算法指令的格式、以及相关的微码ucode设计;

19.图3图解isa指令撰写的一种实施方式;

20.图4为流程图,根据本发明一种实施方式图解sm4密码算法指令引发的步骤程序,相应sm4密码算法指令所转换出的多条微指令;以及

21.图5根据本发明一种实施方式图解一sm4引擎500。

具体实施方式

22.以下叙述列举本发明的多种实施例。以下叙述介绍本发明的基本概念,且并非意图限制本发明内容。实际发明范围应依照权利要求来界定。

23.本发明揭示一种具备分组密码算法(sm4密码算法)的处理器。本发明为sm4密码算法设计指令集架构(instruction set architecture,简称isa)的一分组密码算法指令(sm4密码算法指令)。一种实施方式中,相应该sm4密码算法指令,本发明设计该处理器的微码(ucode)、并且在该处理器的密码执行单元增设分组密码算法加速器(sm4引擎)。处理该sm4密码算法指令时,处理器根据该微码产生多条微指令,包括解读架构寄存器(architecture registers)的内容,再据以操作该sm4引擎,实现sm4密码算法。处理器支持

的指令集可包括x86指令集。sm4密码算法的中间数据(例如,扩展密钥,或输入数据转至输出数据的中间运算内容)可妥善隐藏在处理器内部硬件储存空间中。

24.图1为方块图,根据本发明一种实施方式图解一处理器100。根据分支预测器(branch predictor)102,指令根据指令转译后备缓冲区(instruction translation lookaside buffer)itlb转译结果加载指令高速缓存(instruction cache)104,待缓存至指令缓存器(instruction buffer,简称xib)106,再推入格式指令队列(format instruction queue,简称fiq)108,交由解码器110根据微码(ucode,储存在一微码储存器)解码成流水线可识别的多条微指令(microinstructions),推入指令队列(instruction queue,简称xiq)112,再经重命名单元(rename)114存入相应的保留站(reservation station)rs,驱动逻辑运算单元(arithmetic logical unit)alu、内存顺序缓存区(memory order buffer)116的地址产生单元(address generating unit)agu、多种指令的对应硬件fadd、fmul、fmisc、mmx、或密码执行单元118。运算所需要的数据则可以是根据数据转译后备缓冲区(data translation lookaside buffer)dtlb转译结果加载数据高速缓存(data cache)120,再缓存至该内存顺序缓存区116。处理器100还包括一重排缓存区(reorder buffer,简称rob)122以及架构寄存器(architecture registers)124,以实现运算。

25.密码执行单元118包括sm4引擎126。微码ucode则包括访问相应sm4密码算法指令的架构寄存器124的微指令,具体包括访问控制字(control word,例如,注明加密或解密、是sm4密码算法的哪个模式)寄存器、输入数据块数(number of 16

‑

byte blocks)寄存器、输入密钥指针寄存器、甚至输入、输出数据的信息寄存器的微指令。解码器110根据微码ucode将本发明sm4密码算法指令(一isa指令)解码为处理器100流水线可识别的多条微指令,据以解读架构寄存器124内容,取得控制字、输入密钥、以及输入数据,再驱动该sm4引擎126,基于输入密钥完成输入数据的sm4密码算法的加密、或解密,产生输出数据。所生成的输出数据可存入一内存空间(本发明所述内存空间可以是处理器所链接的一系统内存(如ram)空间,可遵循es segment分段技术)、或是存入一内部硬件存储空间(处理器100中)。解码出的多条微指令中包括使用一条加速器操作微指令(sm4引擎微指令),即负责该sm4引擎126的驱动。解码出的多条微指令中还包括访问、以及管理该组架构寄存器的内容,以及操作密码执行单元118基于该输入密钥对该输入数据进行该分组密码算法。

26.图2a至图2c根据本发明不同实施方式图解isa的sm4密码算法指令的格式、以及相关的微码ucode设计。

27.图2a图解isa的sm4密码算法指令的格式202,并以表格204介绍相关的微码ucode设计。格式202的前缀、操作码(opcode)、字段modr/m为:0xf3 0x0f 0xa 0xf0。字段sib、displacement、以及immediate则不填(non)。解码器110识别出编码”0xf3 0x0f 0xa7 0xf0”后,即依照微码ucode产生多条微指令,其中包括定义、使用、以及且管理架构寄存器124,以操作密码执行单元118基于输入密钥对输入数据进行sm4密码算法。

28.首先,参考表格204,讨论微码ucode如何对应isa的sm4密码算法指令定义输入寄存器(input registers),使用到架构寄存器124中的寄存器ebx(第一寄存器)、ecx(第二寄存器)、eax(第三寄存器)、、esi(第四寄存器)、以及edi(第五寄存器)。

29.第三寄存器eax储存的是控制字,其位0(bit[0])可以

‘0’

代表加密,

‘1’

代表解密;位[10:6]代表sm4密码算法的模式设定,

‘1’

设定一电码本模式(ecb mode),

‘2’

设定一密文

分组链接模式(ccb mode),

‘4’

设定一密文反馈模式(cfb mode),

‘8’

设定一输出反馈模式(ofb mode),

‘

10’设定一计算器模式(ctr mode)。第二寄存器ecx储存的是输入数据块数,以16字节(128位)为一数据块。第一寄存器ebx储存的是一输入密钥指针(指向一系统内存空间,其中储存输入密钥),可遵循es segment分段技术。第四寄存器esi储存的是输入数据指针(指向另一系统内存空间,其中储存输入数据),可遵循es segment分段技术;控制字为加密时,是指向明文(plaintext);控制字为解密时,是指向密文(ciphertext)。第五寄存器edi储存的是输出数据指针(指向另一系统内存空间,用于储存输出数据),可遵循es segment分段技术;控制字为加密时,是指示密文的储存;控制字为解密时,是指示明文的储存。

[0030]

此外,表格204还显示微码ucode如何对应isa的sm4密码算法指令定义输出寄存器(output registers)。一输入数据的所有输入数据块的sm4密码算法完成,第二寄存器ecx清0。第四寄存器esi上维护的输入数据指针、第五寄存器edi上维护的输出数据指针会随每完成一输入数据块的sm4密码算法而递增。执行该分组密码算法后,该处理器令该第四寄存器esi内容基于该输入数据的字节数增加一位移量(所增加的位移量为该输入数据的字节数),并令该第五寄存器edi内容基于该输出数据的字节数增加一位移量(所增加的位移量为该输出数据的字节数)。

[0031]

特别是,输入输出寄存器表格所定义的寄存器使用方式,也可有其他变化,取决于使用者设计。

[0032]

图2b图解isa的sm4密码算法指令的格式212,并以表格214介绍相关的微码ucode设计。格式212同格式202。解码器110识别出编码“0xf3 0x0f 0xa7 0xf0”后,即依照微码ucode产生多条微指令,使用架构寄存器124、并操作sm4引擎126。另一种实施方式是为格式212设定足以与格式202的编码“0xf3 0x0f 0xa7 0xf0”区别的其他编码,使该处理器有能力根据多种格式的sm4密码算法指令进行sm4密码算法。

[0033]

不同于表格204所示微码ucode设计为输入数据指针、输出数据指针分别提供第四寄存器esi以及第五寄存器edi,表格214所示微码ucode设计是以第四寄存器esi储存一输入输出信息指针,指向一系统内存空间,其中储存一输入数据指针、以及一输出数据指针。该输入数据指针指向系统内存储存的一输入数据。该输出数据指针指示一系统内存空间,用于储存输出数据。关于sm4密码算法的输出寄存器,表格214所示微码ucode设计不变动第四寄存器esi。

[0034]

图2c图解isa的sm4密码算法指令的格式222,并以表格224介绍相关的微码ucode设计。不同于格式202、212,格式222有字段inpointer以及outpointer,分别储存指向系统内存储存的一输入数据指针、以及一输出数据指针。该输入数据指针指向系统内存储存的一输入数据。该输出数据指针指示一系统内存空间,用于储存输出数据。解码器110识别出编码“0xf3 0x0f 0xa7 0xf0”后(或特别为了识别格式222的特殊数值编码),即依照微码ucode设计224产生多条微指令,其中包括定义、使用、以及且管理架构寄存器124,以操作密码执行单元118基于输入密钥对输入数据进行sm4密码算法。表格224所示微码ucode设计无须为了输入、输出数据的信息定义架构缓存器。一种实施方式中,字段inpointer以及outpointer分别为32位。

[0035]

图3图解isa指令撰写的一种实施方式。程序代码300可包括以上格式202、212、或

222的sm4密码算法指令302。该条sm4密码算法指令302之前可包括至少一条寄存器设定指令304,用以填写架构寄存器124,为sm4密码算法指令302的执行做准备。

[0036]

图4为流程图,根据本发明一种实施方式图解sm4密码算法指令引发的步骤程序,相应sm4密码算法指令所转换出的多条微指令。

[0037]

步骤s402检查输入数据块数(例如,判读第二寄存器ecx)。若输入数据块数为0(ecx为0),流程进入步骤s404,结束sm4密码算法。若输入数据块数非0(ecx不为0),流程进入步骤s406,令sm4引擎126根据控制字、输入密钥、一输入数据块(分解自一输入数据)操作。步骤s408,sm4引擎126产生的一输出数据块存入内存,以组成输出数据。然后,sm4引擎126将第二寄存器ecx中的值减1。步骤s410检查是否完成所有输入数据块的sm4密码算法。例如,检查第二寄存器ecx是否为0。若ecx非0,流程回到步骤s406,令sm4密码算法引擎126根据控制字、输入密钥、下一输入数据块操作。若ecx为0,流程进入步骤s412,结束sm4密码算法。在另一实施例中,sm4引擎126将第二寄存器ecx中的值减1的步骤是安排在执行完步骤s406之后,执行步骤s408之前。

[0038]

上述sm4引擎微指令对应步骤s406用于驱动该sm4引擎126完成各输入数据块的sm4密码算法。

[0039]

图5根据本发明一种实施方式图解一sm4引擎500,其中硬件用作:控制逻辑502、轮运算逻辑(rounding logic)504、密钥扩展逻辑(key extension logic)506、以及密钥反序转换(anti

‑

tone transform)508,且包括加速器内部储存空间m1~m3、以及多路复用器mux。

[0040]

根据第二寄存器ebx所储存的输入密钥指针,一输入密钥510取自系统内存,并输入该sm4引擎500。基于该输入密钥510,密钥扩展逻辑506产生一数据块32轮运算所需的32个密钥rk0...rk

31

,储存于加速器内部储存空间m1作为32个顺序密钥。密钥反序转换508将32个顺序密钥rk0...rk

31

反序为rk

31

...rk0,储存于加速器内部储存空间m2作为32个反序密钥。顺序、反序密钥都交予多路复用器mux输入端。

[0041]

控制字512取自第三寄存器eax。控制逻辑502根据控制字512提供选择信号dec/enc切换多路复用器mux,使提供顺序密钥rk0...rk

31

给该轮运算逻辑504进行加密,或提供反序密钥rk

31

...rk0给该轮运算逻辑504进行解密。轮运算逻辑504也可根据此选择信号dec/enc做加、解密切换。

[0042]

输入数据514取自系统内存,逐数据块输入该轮运算逻辑504。该轮运算逻辑504以多路复用器mux传来的32个密钥对各数据块进行32轮加密、或解密。

[0043]

轮运算逻辑504包括多重异或逻辑(multi

‑

xor logic)516、非线性转换(non

‑

linear transform)518、线性转换(linear transform)520、单异或逻辑(singlexor logic)522、以及反序转换524。对应一目标数据块轮运算逻辑504以从该多路复用器mux取得的密钥i=0,1,2,...31,进行32轮运算。加、解密都采此硬件。内部各硬件设计如下。

[0044]

·

多重异或逻辑516进行运算:

[0045]

(x

i+1

^x

i+2

^x

i+3

^k

i

)

[0046]

^为32位异或。

[0047]

·

非线性转换518进行运算:

[0048]

b=t(a),即

[0049]

(b0,b1,b2,b3)=(sbox(a0),sbox(a1),sbox(a2),sbox(a3)),

[0050]

sbox为s盒运算,为固定的8位输入8位输出的置换。a为硬件方块518

[0051]

输入,b为硬件方块518输出,b为硬件方块518输出,

[0052]

·

线性转换520进行运算:

[0053]

l(b)=b^(b<<<2)^(b<<<10)^(b<<<18)^(b<<<24)

[0054]

<<<i为32位循环左移i位。

[0055]

·

单异或逻辑522进行运算:

[0056]

x

i+4

=x

i

^t(x

i+1

^x

i+2

^x

i+3

^k

i

)

[0057]

t为可逆转换,t(x

i+1

^x

i+2

^x

i+3

^k

i

)即非线性转换518、和线性转换

[0058]

520的运算结果,t(.)=l(t(.))。

[0059]

·

反序转换524进行运算:

[0060]

r(a0,a1,a2,a3)=(a3,a2,a1,a0)

[0061]

a为硬件方块524输入。32轮运算后,反序转换524输出该目标数据块(x0,x1,x2,x3)的输出数据块为r(x

32

,x

33

,x

34

,x

35

)=(x

35

,x

34

,x

33

,x

32

)。

[0062]

以加密为例,为明文输入,32轮密钥为取自加速器内部储存空间m1的32个顺序密钥i=0,1,2,...31。

[0063]

以解密为例,为密文输入,32轮密钥为取自加速器内部储存空间m2的32个反序密锣i=31,30,29,...0。

[0064]

密钥扩展逻辑506包括密钥异或逻辑(key

‑

xor logic)526、多重异或逻辑(multi

‑

xor logic)528、非线性转换(non

‑

linear transformm)530、线性转换(linear transform)532、以及单异或逻辑(single xor logic)534。密钥扩展逻辑506根据输入密钥510(即mk=(mk0,mk1,mk2,mk3),mk0、mk1、mk2、mk3各自为32位)、系统参数fk(=(fk0,fk1,fk2,fk3),fk0、fk1、fk2、fk3各自为32位)、以及固定参数ck(=(ck0,ck1,...,ck

31

),ck0、ck1、...、ck

31

各自为32位)操作。系统参数fk、以及固定参数ck可由内部储存空间m3提供。内部各硬件设计如下。

[0065]

·

密钥异或逻辑526进行运算:

[0066]

(k0,k1,k2,k3)=(mk0^fk0,mk1^fk1,mk2^fk2,mk3^fk3)

[0067]

^为32位异或。

[0068]

·

多重异或逻辑528进行运算:

[0069]

(k

i+1

^k

i+2

^k

i+3

^ck

i

)

[0070]

·

非线性转换530进行运算:

[0071]

b=t(a),即

[0072]

(b0,b1,b2,b3)=(sbox(a0),sbox(a1),sbox(a2),sbox(a3)),

[0073]

sbox为s盒运算,为固定的8位输入8位输出的置换。a为硬件方块530

[0074]

输入,b为硬件方块530输出,b为硬件方块530输出,

[0075]

·

线性转换532进行运算:

[0076]

l’(b)=b^(b<<<13)^(b<<<23)

[0077]

<<<i为32位循环左移i位。

[0078]

·

单异或逻辑534进行运算:

[0079]

rk

i

=k

i+4

=k

i

^t

′

(k

i+1

^x

i+2

^x

i+3

^ck

i

)

[0080]

t’为可逆转换,t

′

(k

i+1

^x

i+2

^x

i+3

^ck

i

)即非线性转换530、和线性转换532的运算结果,t’(.)=l’(t(.))。rk

i

,i=0,...,31顺序计算出,并顺序存入加速器内部储存空间m1,再由密钥反序转换硬件508进行反序转换,形成反序密钥存入加速器内部储存空间m2。

[0081]

扩展密钥rk

i

不论是顺序或反序,都妥善保护在sm4引擎500中。甚至,轮运算逻辑504和密钥扩展逻辑506也使得轮运算和密钥扩展运算的中间数据妥善保护于sm4引擎500中。本发明设计提供更高安全度的密码算法硬件。

[0082]

一种实施方式中,该处理器对各输入数据块分别进行n轮运算,以对应各输入数据块分别产生一个输出数据块,组成该输出数据,n为整数。该处理器基于该输入密钥扩展出n个扩展密钥,使各输入数据块的不同轮运算是使用不同的扩展密钥。n不限定为32。

[0083]

一种实施方式中,密码执行单元118没有特地设计sm4引擎126。此实施例通过规划微码ucode内容,令单一条isa的sm4密码算法指令转换出多条微指令操作逻辑运算单元alu,即完成sm4密码算法。特别是,此实施例还能将sm4密码算法的重要中间数据保护在处理器的内部储存空间。

[0084]

一种实施方式中,sm4引擎的功能不如sm4引擎500强大,而是将sm4引擎500的部分功能模块(比如,密码扩展逻辑506)由微码ucode配置微指令操作逻辑运算单元alu来实现。此实施例还能将sm4密码算法的重要中间数据保护在处理器的内部储存空间。

[0085]

综上所述,根据本发明一种实施方式实现的一处理器包括一密码执行单元、一组架构寄存器、储存一微码的一微码储存装置、以及一解码器。相应一指令集架构(isa)的一分组密码算法指令,该解码器根据该微码产生多条微指令(microinstructions)。所述多条微指令包括定义、使用、以及且管理该组架构寄存器的内容,以及操作该密码执行单元基于一输入密钥对一输入数据进行一分组密码算法(sm4),产生、并储存一输出数据。关于该输入数据的该分组密码算法,源于该输入密钥的多个扩展密钥可以保护于该处理器内部硬件储存空间,从而极大地提高了安全性。本发明为sm4密码算法设计了专用的isa的sm4密码算法指令。

[0086]

由上可知,在已知的技术中,需要使用多条指令集架构指令才能实现分组密码算法,无法有效保护运算过程中生成的中间数据,所以安全性较差。但是,通过本发明提供的具备分组密码算法(sm4)的处理器及其处理方法,只需使用一条指令集架构指令就可以实现分组密码算法,可将在实现分组密码算法的过程中生成的中间数据储存在处理器内部硬件存储空间中,使得在处理器外部无法访问这些中间数据,因而极大地提高了安全性。

[0087]

虽然本发明已以较佳实施例揭示如上,然其并非用以限定本发明,任何本领域技

术人员,在不脱离本发明的精神和范围内,当可做些许更动与润饰,因此本发明的保护范围以权利要求书界定为准。

[0088]

[符号说明]

[0089]

100:处理器;

[0090]

102:分支预测器;

[0091]

104:指令高速缓存;

[0092]

106:指令缓存器(xib);

[0093]

108:格式指令队列(fiq);

[0094]

110:解码器;

[0095]

112:指令队列(xiq);

[0096]

114:重命名单元;

[0097]

116:内存顺序缓存区;

[0098]

118:密码执行单元;

[0099]

120:数据高速缓存;

[0100]

122:重排缓存区;

[0101]

124:架构寄存器;

[0102]

126:sm4引擎(分组密码算法加速器);

[0103]

202、212、222:sm4密码算法指令的格式;

[0104]

204、214、224:表格,相应sm4密码算法的输入、输出寄存器设计;

[0105]

300:程序代码;

[0106]

302:sm4密码算法指令;

[0107]

304:至少一条寄存器设定指令;

[0108]

500:sm4引擎;

[0109]

502:硬件,用作控制逻辑;

[0110]

504:硬件,用作轮运算逻辑;

[0111]

506:硬件,用作密钥扩展逻辑;

[0112]

508:硬件,用作密钥反序转换;

[0113]

510:输入密钥;

[0114]

512:控制字;

[0115]

514:输入数据;

[0116]

516:硬件,用作多重异或逻辑;

[0117]

518:硬件,用作非线性转换;

[0118]

520:硬件,用作线性转换;

[0119]

522:硬件,用作单异或逻辑;

[0120]

524:硬件,用作反序转换;

[0121]

526:硬件,用作密钥异或逻辑;

[0122]

528:硬件,用作多重异或逻辑;

[0123]

530:硬件,用作非线性转换;

[0124]

532:硬件,用作线性转换;

[0125]

534:硬件,用作单异或逻辑;

[0126]

agu:地址产生单元;

[0127]

alu:逻辑运算单元;

[0128]

dec/enc:选择信号;

[0129]

dtlb:数据转译后备缓冲区;

[0130]

eax、ecx、ebx、esi、edi:寄存器;

[0131]

fadd、fmul、fmisc、mmx:多种指令的对应硬件;

[0132]

inpointer、outpointer:字段,填输入数据指针、输出数据指针;

[0133]

itlb:指令转译后备缓冲;

[0134]

m1、m2、m3:加速器内部储存空间;

[0135]

mux:多路复用器;

[0136]

non:无填值;

[0137]

opcode、modr/m、sib、displacement、immediate:字段;

[0138]

rs:保留站;

[0139]

s402

…

s412:步骤;

[0140]

ucode:微码。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1