SRAM存储单元版图及设计方法、电路、半导体结构、存储器与流程

sram存储单元版图及设计方法、电路、半导体结构、存储器

技术领域

1.本技术涉及集成电路领域,尤其涉及一种sram存储单元版图及设计方法、电路、半导体结构、存储器。

背景技术:

2.随着电子技术的发展,对集成电路的性能要求也在不断提高。在相同的加工面积上,需要集成更多的电子元件,以提高集成电路的集成度。同时,随着集成电路结构的复杂化,也使得加工工艺更加复杂,带来了低良率风险。

3.在集成电路中,连接线用于将各半导体器件之间导通。在布置连接线的过程中,需要多布置一部分金属材料,留出余量空间,以避免导通不良。这样,额外占用了加工面积,不利于提高集成电路的集成度。同时,布置连接线的工艺较为复杂,存在低良率风险。

技术实现要素:

4.本技术实施例期望提出一种sram存储单元版图及设计方法、电路、半导体结构、存储器,能够减少连接线的使用,以节约加工面积,提高集成电路的集成度;同时,简化加工工艺,减少低良率风险。

5.本技术的技术方案是这样实现的:

6.本技术实施例提供一种sram存储单元版图,所述版图包括:

7.衬底;

8.沿第一方向延伸的至少一个有源区;

9.沿第二方向延伸的至少一个栅极结构;所述第二方向垂直于所述第一方向;

10.至少一个接触结构;其中,

11.所述至少一个接触结构连接所述至少一个有源区中的两个相邻有源区,以及目标栅极结构;所述目标栅极结构属于所述至少一个栅极结构;

12.所述目标栅极结构在所述衬底中的投影相交于所述至少一个有源区中除所述两个相邻有源区外的其他有源区在所述衬底中的投影。

13.本技术实施例还提供一种sram存储单元设计方法,所述方法包括:

14.提供衬底;

15.设置沿第一方向延伸的至少一个有源区;所述至少一个有源区包括:第一有源区和第二有源区;

16.设置沿第二方向延伸的至少一个栅极结构;所述第二方向垂直于所述第一方向;第一栅极结构;

17.设置至少一个接触结构;其中,

18.所述至少一个接触结构接触结构连接所述至少一个有源区中的两个相邻有源区,以及目标栅极结构;所述目标栅极结构属于所述至少一个栅极结构;

19.所述目标栅极结构在所述衬底中的投影相交于所述至少一个有源区中除所述两

个相邻有源区外的其他有源区在所述衬底中的投影。

20.本技术实施例还提供一种sram存储单元电路,其特征在于,包括:开关单元、第一锁存单元和第二锁存单元;

21.所述开关单元、所述第一锁存单元和所述第二锁存单元通过至少一个接触结构连接;

22.所述第一锁存单元连接电源端;所述第二锁存单元连接接地端;

23.所述开关单元连接位线;所述开关单元还接收字线信号;其中,

24.所述开关单元,用于在读取状态和写入状态时,在被所述字线信号触发的情况下,将所述第一锁存单元和所述第二锁存单元导通于所述位线,以进行存储信号的读取和写入;

25.所述第一锁存单元和所述第二锁存单元组成锁存电路,用于对所述存储信号进行锁定和保存。

26.本技术实施例还提供一种半导体结构,其特征在于,由上述方案中的版图示出。

27.本技术实施例还提供一种半导体存储器,其特征在于,包括上述方案中的半导体结构。

28.由此可见,本技术实施例提供了一种sram存储单元版图及设计方法、电路、半导体结构、存储器,sram存储单元版图包括:衬底;沿第一方向延伸的至少一个有源区;沿第二方向延伸的至少一个栅极结构,其中,第二方向垂直于第一方向;以及,至少一个接触结构。其中,至少一个接触结构连接至少一个有源区中的两个相邻有源区,以及目标栅极结构;目标栅极结构属于至少一个栅极结构;目标栅极结构在衬底中的投影相交于至少一个有源区中除两个相邻有源区外的其他有源区在衬底中的投影。这样,通过接触结构直接连接了半导体器件,减少了连接线的使用,从而,能够节约加工面积,提高集成电路的集成度;同时,减少了金属布线的过程,从而,简化了加工工艺,能够提高产品良率。

附图说明

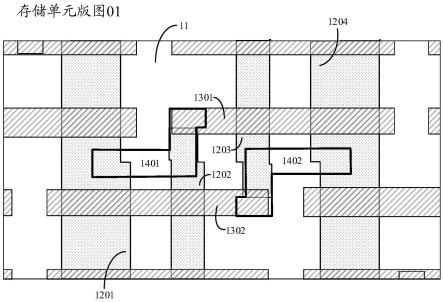

29.图1为本技术实施例提供的一种sram存储单元版图的示意图一;

30.图2为本技术实施例提供的一种sram存储单元版图的示意图二;

31.图3为本技术实施例提供的一种sram存储单元版图的示意图三;

32.图4为本技术实施例提供的一种sram存储单元版图的示意图四;

33.图5为本技术实施例提供的一种sram存储单元版图设计方法的流程图一;

34.图6为本技术实施例提供的一种sram存储单元版图设计方法的流程图二;

35.图7为本技术实施例提供的一种sram存储单元版图设计方法的流程图三;

36.图8为本技术实施例提供的一种sram存储单元电路的示意图一;

37.图9为本技术实施例提供的一种sram存储单元电路的示意图二;

38.图10为本技术实施例提供的一种半导体存储器的结构示意图。

具体实施方式

39.为了使本技术的目的、技术方案和优点更加清楚,下面结合附图和实施例对本技术的技术方案进一步详细阐述,所描述的实施例不应视为对本技术的限制,本领域普通技

术人员在没有做出创造性劳动前提下所获得的所有其它实施例,都属于本技术保护的范围。

40.在以下的描述中,涉及到“一些实施例”,其描述了所有可能实施例的子集,但是可以理解,“一些实施例”可以是所有可能实施例的相同子集或不同子集,并且可以在不冲突的情况下相互结合。

41.如果申请文件中出现“第一/第二”的类似描述则增加以下的说明,在以下的描述中,所涉及的术语“第一/第二/第三”仅仅是区别类似的对象,不代表针对对象的特定排序,可以理解地,“第一/第二/第三”在允许的情况下可以互换特定的顺序或先后次序,以使这里描述的本技术实施例能够以除了在这里图示或描述的以外的顺序实施。

42.除非另有定义,本文所使用的所有的技术和科学术语与属于本技术的技术领域的技术人员通常理解的含义相同。本文中所使用的术语只是为了描述本技术实施例的目的,不是旨在限制本技术。

43.在集成电路中,半导体衬底上形成了各个半导体器件,连接线则用于将各半导体器件之间导通。然而,在布置连接线的过程中,在连接线与半导体器件的接触位置需要多布置一部分金属材料,留出余量空间,以避免导通不良,影响集成电路性能。这样,不仅需要为布置连接线预留更大的空间,额外占用了加工面积,不利于提高集成电路的集成度;同时,布置连接线的工艺较为复杂,有更高的风险造成低良率。

44.图1是本技术实施例提供的一种sram存储单元版图,如图1所示,存储单元版图01中,包括了:衬底11(图1中空白填充区域);沿第一方向延伸的至少一个有源区(图1中点状填充区域),包括:第一有源区1201、第二有源区1202、第三有源区1203和第四有源区1204;沿第二方向延伸的至少一个栅极结构(图1中斜线填充区域),包括:第一栅极结构1301和第二栅极结构1302,其中,第二方向垂直于第一方向;至少一个接触结构(图1中加粗黑框所包含区域),包括:第一接触结构1401和第二接触结构1402。

45.其中,至少一个接触结构连接至少一个有源区中的两个相邻有源区,以及目标栅极结构,其中,目标栅极结构属于至少一个栅极结构。结合图1,目标栅极结构可以为第一栅极结构1301,第一接触结构1401连接第一有源区1201、第二有源区1202和第一栅极结构1301;目标栅极结构也可以为第二栅极结构1302,第二接触结构1402连接第三有源区1203、第四有源区1204和第二栅极结构1302。

46.目标栅极结构在衬底中的投影相交于至少一个有源区中除两个相邻有源区外的其他有源区在衬底中的投影。参考图1,目标栅极结构可以为第一栅极结构1301,第三有源区1203在衬底11中的投影和第四有源区1204在衬底11中的投影分别相交于第一栅极结构1301在衬底11中的投影;目标栅极结构也可以为第二栅极结构1302,第一有源区1201在衬底11中的投影和第二有源区1202在衬底11中的投影分别相交于第二栅极结构1302在衬底11中的投影。

47.需要说明的是,集成电路版图,是真实集成电路物理情况的平面几何形状描述,其包含了各硬件单元在芯片上的形状、面积和位置信息。也就是说,集成电路版图中的图形,表征了集成电路中的硬件单元及其电连接关系。

48.在本技术实施例中,图9中的电路结构与图1具有对应关系。结合图1和图9,第三有源区1203在衬底11中的投影和第四有源区1204在衬底11中的投影分别相交于第一栅极结

构1301在衬底11中的投影,表征了第三有源区1203中在第一栅极结构1301两侧的源漏区,第一栅极结构1301两侧的源漏区和第一栅极结构1301共同形成第一pmos管pu1;以及,第四有源区1204在第一栅极结构1301两侧的源漏区,第一栅极结构1301两侧的源漏区和第一栅极结构1301共同形成第三nmos管pd1。第一有源区1201在衬底11中的投影和第二有源区1202在衬底11中的投影分别相交于第二栅极结构1302在衬底11中的投影,表征了第一有源区1201中在第二栅极结构1302两侧的源漏区,第二栅极结构1302两侧的源漏区和第二栅极结构1302共同形成第四nmos管pd2;以及,第二有源区1202中在第二栅极结构1302两侧的源漏区,第二栅极结构1302两侧的源漏区和第二栅极结构1302共同形成第二pmos管pu2。

49.第一接触结构1401连接第一有源区1201、第二有源区1202和第一栅极结构1301,表征了第四nmos管pd2的漏极、第二pmos管pu2的漏极、第一pmos管pu1的栅极和第三nmos管pd1的栅极通过第一接触结构1401而电连接。第二接触结构1402连接第三有源区1203、第四有源区1204和第二栅极结构1302,表征了第三nmos管pd1的漏极、第一pmos管pu1的漏极、第二pmos管pu2的栅极和第四nmos管pd2的栅极通过第二接触结构1402而电连接。

50.在本技术实施例中,如图1所示,第一有源区1201、第二有源区1202、第三有源区1203和第四有源区1204依次相邻排列。第一有源区1201与第四有源区1204呈中心对称。第二有源区1202与第三有源区1203呈中心对称。第一栅极结构1301与第二栅极结构1302呈中心对称。第一接触结构1401与第二接触结构1402呈中心对称。

51.从而,第一有源区1201、第二有源区1202、第三有源区1203、第四有源区1204、第一栅极结构1301、第二栅极结构1303、第一接触结构1401和第二接触结构1402,能够设置如图9中相对称的半导体器件第一pmos管pu1与第二pmos管pu2、第三nmos管pd1与第四nmos管pd2,这些半导体器件具有相对称的电连接关系。

52.在本技术实施例中,如图2所示,至少一个接触结构(即第一接触结构1401和第二接触结构1402)的形状可以为l形。l形的各个边的长度可以如表1所示:

[0053][0054][0055]

表1

[0056]

可以理解的是,通过第一接触结构1401,直接连接了第四nmos管pd2的漏极、第二

pmos管pu2的漏极、第一pmos管pu1的栅极和第三nmos管pd1的栅极;通过第二接触结构1402,直接连接了第三nmos管pd1的漏极、第一pmos管pu1的漏极、第二pmos管pu2的栅极和第四nmos管pd2的栅极。这样,减少了连接线的使用,从而,能够节约加工面积,提高集成电路的集成度;同时,减少了金属布线的过程,从而,简化了加工工艺,能够提高产品良率。

[0057]

在本技术的一些实施例中,如图3所示,存储单元版图01中,还包括:沿第二方向延伸的第三栅极结构1303;第三接触结构1403、第四接触结构1404、第五接触结构1405和第六接触结构1406。

[0058]

其中,第三栅极结构1303在衬底11中的投影相交于第一有源区1201在衬底11中的投影;第三接触结构1403和第四接触结构1404均位于第一有源区1201中;第三接触结构1403和第一接触结构1401分别位于第三栅极结构1303的两侧;第四接触结构1404和第一接触结构1401分别位于第二栅极结构1302的两侧;第五接触结构1405位于第二有源区1202中;第五接触结构1405和第一接触结构1401分别位于第二栅极结构1302的两侧;第六接触结构1406位于第三栅极结构1303中。

[0059]

在本技术实施例中,结合图3和图9,第三栅极结构1303在衬底11中的投影相交于第一有源区1201在衬底11中的投影,表征了第一有源区1201中在第三栅极结构1303两侧的源漏区,第三栅极结构1303两侧的源漏区和第三栅极结构1303共同形成第二nmos管pg2;第二nmos管pg2的源极亦为第四nmos管pd2的漏极。

[0060]

第三接触结构1403位于第一有源区1201中,第三接触结构1403和第一接触结构1401分别位于第三栅极结构1303的两侧,表征了第三接触结构1403连接第二nmos管pg2的漏极,第一接触结构1401连接第二nmos管pg2的源极(亦为第四nmos管pd2的漏极)。

[0061]

第四接触结构1404位于第一有源区1201中,第四接触结构1404和第一接触结构1401分别位于第二栅极结构1302的两侧,表征了第四接触结构1404连接第四nmos管pd2的源极,第一接触结构1401连接第四nmos管pd2的漏极(亦为第二nmos管pg2的源极)。

[0062]

第五接触结构1405位于第二有源区1202中,第五接触结构1405和第一接触结构1401分别位于第二栅极结构1302的两侧,表征了第五接触结构1405连接第二pmos管pu2的源极,第一接触结构1401连接第二pmos管pu2的漏极。

[0063]

第六接触结构1406位于第三栅极结构1303中,表征了第六接触结构1406连接第二nmos管pg2的栅极。

[0064]

在本技术的一些实施例中,如图3所示,存储单元版图01中,还包括:沿第二方向延伸的第四栅极结构1304;第七接触结构1407、第八接触结构1408、第九接触结构1409和第十接触结构1410。

[0065]

其中,第四栅极结构1304在衬底11中的投影相交于第四有源区1204在衬底11中的投影;第七接触结构1407位于第三有源区1203中;第七接触结构1407和第二接触结构1402分别位于第一栅极结构1301的两侧;第八接触结构1408和第九接触结构1409均位于第四有源区1204中;第八接触结构1408和第二接触结构1402分别位于第一栅极结构1301的两侧;第九接触结构1409和第二接触结构1402分别位于第四栅极结构1304的两侧;第十接触结构1410位于第四栅极结构1304中。

[0066]

在本技术实施例中,结合图3和图9,第四栅极结构1304在衬底11中的投影相交于第四有源区1204在衬底11中的投影,表征了第四有源区1204中在第四栅极结构1304两侧的

源漏区,第四栅极结构1304两侧的源漏区和第四栅极结构1304设置第一nmos管pg1;第一nmos管pg1的源极亦为第三nmos管pd1的漏极。

[0067]

第七接触结构1407位于第三有源区1203中,第七接触结构1407和第二接触结构1402分别位于第一栅极结构1301的两侧,表征了第七接触结构1407连接第一pmos管pu1的源极,第二接触结构1402连接第一pmos管pu1的漏极。

[0068]

第八接触结构1408位于第四有源区1204中,第八接触结构1408和第二接触结构1402分别位于第一栅极结构1301的两侧,表征了第八接触结构1408连接第三nmos管pd1的源极,第二接触结构1402连接第三nmos管pd1的漏极(亦为第一nmos管pg1的源极)。

[0069]

第九接触结构1409位于第四有源区1204中,第九接触结构1409和第二接触结构1402分别位于第四栅极结构1304的两侧,表征了第九接触结构1409连接第一nmos管pg1的漏极,第二接触结构1402连接第一nmos管pg1的源极(亦为第三nmos管pd1的漏极)。

[0070]

第十接触结构1410位于第四栅极结构1304中,表征了第十接触结构1410连接第一nmos管pg1的栅极。

[0071]

在本技术实施例中,如图3所示,第三栅极结构1303与第四栅极结构1304呈中心对称。第一栅极结构1301和第三栅极结构1303位于第二栅极结构1302的同一侧,第二栅极结构1302和第四栅极结构1304位于第一栅极结构1301的同一侧。

[0072]

从而,第一有源区1201、第四有源区1204、第三栅极结构1303、第四栅极结构1304、第一接触结构1401和第二接触结构1402,能够设置如图9中相对称的半导体器件第一nmos管pg1与第二nmos管pg2,这些半导体器件具有相对称的电连接关系。

[0073]

可以理解的是,通过有源区、栅极结构和接触结构,用新的物理结构,构建了图9中的存储单元电路。从而在制造存储单元电路的过程中,减少了连接线的使用,节约了加工面积,提高集成电路的集成度;同时,减少了金属布线的过程,简化了加工工艺,能够提高产品良率。

[0074]

在本技术的一些实施例中,如图4所示,存储单元版图01中,还包括:

[0075]

至少一个金属线(图4中横线填充区域),包括:第一金属线1501、第二金属线1502、第三金属线1503、第四金属线1504、第五金属线1505、第六金属线1506、第七金属线1507和第八金属线1508。

[0076]

其中,第一金属线1501、第二金属线1502、第三金属线1503、第四金属线1504、第五金属线1505、第六金属线1506、第七金属线1507和第八金属线1508,分别依次连接第三接触结构1403、第四接触结构1404、第五接触结构1405、第六接触结构1406、第七接触结构1407、第八接触结构1408、第九接触结构1409和第十接触结构1410。

[0077]

在本技术实施例中,金属线和接触结构对应连接,表征了连接在接触结构上的有源区或栅极结构,通过接触结构和金属线和其他对象电连接。

[0078]

可以理解的是,通过金属线的使用,完成了存储单元电路中各mos端口与对应电连接对象的电连接。

[0079]

sram存储单元版图设计方法的一个可选的流程示意图,将结合图5示出的步骤进行说明。

[0080]

s201、提供衬底。

[0081]

本技术实施例中,设计sram存储单元版图需要先提供衬底,sram存储单元是在衬

底上加工制造而得到的。衬底是具有特定晶面和适当电学、光学和机械特性的洁净单晶半导体薄片。衬底通常为单晶硅材料,也可以为其他半导体材料。

[0082]

s202、设置沿第一方向延伸的至少一个有源区。

[0083]

本技术实施例中,设计人员可以在版图中的衬底上设置沿第一方向延伸的至少一个有源区。其中,有源区是衬底上做有源器件的区域;有源器件在外加电源下能够进行工作。

[0084]

参考图1,至少一个有源区可以包括:第一有源区1201、第二有源区1202、第三有源区1203和第四有源区1204。第一有源区1201、第二有源区1202、第三有源区1203和第四有源区1204依次相邻排列。

[0085]

需要说明的是,有源区的制造可以通过以下方法完成:半导体设备可以向衬底中的部分区域掺杂,改变这些区域的电学特性,形成至少一个有源区。以单晶硅材料的衬底为例,向硅衬底中掺入3价元素,如硼(b),可以形成p型有源区,p型有源区中包含空穴;向硅衬底中掺入5价元素,如磷(p)、砷(as),可以形成n型有源区,n型有源区中包含自由电子。基于p型有源区和n型有源区,可以形成半导体器件,如pmos和nmos。

[0086]

其中,可以根据所需要的掺杂深度,选择扩散(diffusion)或者离子注入(ion implantation)来完成对衬底的掺杂。扩散是将掺杂元素直接跟硅衬底表面接触,通过热能的辅助,将掺杂元素掺入到硅衬底中,扩散的掺杂深度较浅。离子注入是将掺杂材料激活为等离子态(plasma),经过高能加速后,注入到硅衬底中需要掺杂的区域,离子注入的掺杂深度较深。由于离子注入会对硅衬底造成晶格损伤(lattice damage),因此还需要进行热处理(thermal annealing)来修复晶格损伤。

[0087]

s203、设置沿第二方向延伸的至少一个栅极结构;第二方向垂直于第一方向。

[0088]

本技术实施例中,设计人员可以在版图中的有源区上设置沿着第二方向延伸的至少一个栅极结构,其中,第二方向垂直于第一方向。

[0089]

参考图1,至少一个栅极结构可以包括:第一栅极结构1301和第二栅极结构1302。

[0090]

需要说明的是,栅极结构包括了栅介质层、栅介质层上的其他介质层,栅介质层下为栅极有源区,栅介质层和其他介质层在栅极有源区上沉积形成。栅极结构在衬底中的投影与对应有源区在衬底中的投影垂直相交,有源区在栅极结构的两侧形成有源漏区,源漏区和栅极有源区的掺杂类型相反。栅极结构和其两侧的源漏区形成了mos。

[0091]

s204、设置至少一个接触结构;其中,至少一个接触结构连接至少一个有源区中的两个相邻有源区,以及目标栅极结构;目标栅极结构属于至少一个栅极结构;目标栅极结构在衬底中的投影相交于至少一个有源区中除两个相邻有源区外的其他有源区在衬底中的投影。

[0092]

本技术实施例中,设计人员在设置了至少一个有源区和至少一个栅极结构后,可以在版图中设置至少一个接触结构。其中,至少一个接触结构连接至少一个有源区中的两个相邻有源区,以及目标栅极结构。而目标栅极结构属于至少一个栅极结构,目标栅极结构在衬底中的投影相交于至少一个有源区中除两个相邻有源区外的其他有源区在衬底中的投影。

[0093]

参考图1,至少一个接触结构可以包括:第一接触结构1401和第二接触结构1402。目标栅极结构可以为第一栅极结构1301,第一接触结构1401连接第一有源区1201、第二有

源区1202和第一栅极结构1301。目标栅极结构也可以为第二栅极结构1302,第二接触结构1402连接第三有源区1203、第四有源区1204和第二栅极结构1302。

[0094]

在本技术实施例中,如图2所示,至少一个接触结构(即第一接触结构1401和第二接触结构1402)的形状可以为l形。l形的各个边的长度可以如表1所示。

[0095]

需要说明的是,接触结构的材料为导电材料,从而将对应区域电连接,也就是说,通过至少一个接触结构,可以将至少一个有源区中的两个相邻有源区,以及目标栅极结构电连接。参考图1,通过第一接触结构1401,可以将第一有源区1201、第二有源区1202和第一栅极结构1301电连接;通过第二接触结构1402,可以将第三有源区1203、第四有源区1204和第二栅极结构1302电连接。

[0096]

继续参考图1,第三有源区1203在衬底11中的投影和第四有源区1204在衬底11中的投影分别相交于第一栅极结构1301在衬底11中的投影;第一有源区1201在衬底11中的投影和第二有源区1202在衬底11中的投影分别相交于第二栅极结构1302在衬底11中的投影。

[0097]

第一有源区1201与第四有源区1204呈中心对称。第二有源区1202与第三有源区1203呈中心对称。第一栅极结构1301与第二栅极结构1302呈中心对称。第一接触结构1401与第二接触结构1402呈中心对称。

[0098]

从而,第一有源区1201、第二有源区1202、第三有源区1203、第四有源区1204、第一栅极结构1301、第二栅极结构1303、第一接触结构1401和第二接触结构1402,能够形成如图9中相对称的半导体器件第一pmos管pu1与第二pmos管pu2、第三nmos管pd1与第四nmos管pd2,这些半导体器件具有相对称的电连接关系。

[0099]

可以理解的是,通过第一接触结构1401,直接连接了第四nmos管pd2的漏极、第二pmos管pu2的漏极、第一pmos管pu1的栅极和第三nmos管pd1的栅极;通过第二接触结构1402,直接连接了第三nmos管pd1的漏极、第一pmos管pu1的漏极、第二pmos管pu2的栅极和第四nmos管pd2的栅极。这样,减少了连接线的使用,从而,能够节约加工面积,提高集成电路的集成度;同时,减少了金属布线的过程,从而,简化了加工工艺,能够提高产品良率。

[0100]

在本技术的一些实施例中,在图5示出的s202之后还包括图6示出的s205,将结合各步骤进行说明。

[0101]

s205、设置沿第二方向延伸的第三栅极结构和第四栅极结构;第三栅极结构在衬底中的投影相交于第一有源区在衬底中的投影;第四栅极结构在衬底中的投影相交于第四有源区在衬底中的投影。

[0102]

本技术实施例中,设计人员在设置至少一个有源区之后,还可以在版图上设置沿第二方向延伸的第三栅极结构和第四栅极结构。

[0103]

参考图3,第三栅极结构1303和第四栅极结构1304呈中心对称;第三栅极结构1303在衬底11中的投影相交于第一有源区1201在衬底11中的投影;第四栅极结构1304在衬底11中的投影相交于第四有源区1204在衬底11中的投影。

[0104]

第三栅极结构1303与第四栅极结构1304呈中心对称。第一栅极结构1301和第三栅极结构1303位于第二栅极结构1302的同一侧,第二栅极结构1302和第四栅极结构1304位于第一栅极结构1301的同一侧。

[0105]

从而,第一有源区1201、第四有源区1204、第三栅极结构1303、第四栅极结构1304、第一接触结构1401和第二接触结构1402,能够形成如图9中相对称的半导体器件第一nmos

管pg1与第二nmos管pg2,这些半导体器件具有相对称的电连接关系。

[0106]

s206、设置第三接触结构、第四接触结构、第五接触结构、第六接触结构、第七接触结构、第八接触结构、第九接触结构和第十接触结构;其中,第三接触结构和第四接触结构均位于第一有源区中;第五接触结构位于第二有源区中;第六接触结构位于第三栅极结构中;第七接触结构位于第三有源区中;第八接触结构和第九接触结构均位于第四有源区中;第十接触结构位于第四栅极结构中。

[0107]

本技术实施例中,设计人员还可以在版图中设置第三接触结构、第四接触结构、第五接触结构、第六接触结构、第七接触结构、第八接触结构、第九接触结构和第十接触结构。

[0108]

参考图4,第三接触结构1403和第四接触结构1404均位于第一有源区1201中;第五接触结构1405位于第二有源区1202中;第六接触结构1406位于第三栅极结构1303中;第七接触结构1407位于第三有源区1203中;第八接触结构1408和第九接触结构1409均位于第四有源区1204中;第十接触结构1410位于第四栅极结构1304中。

[0109]

第三接触结构1403和第一接触结构1401分别位于第三栅极结构1303的两侧,表征第三接触结构1403和第一接触结构1401分别连接第二nmos管pg2的漏极和源极。第四接触结构1404和第一接触结构1401分别位于第二栅极结构1302的两侧,表征第四接触结构1404和第一接触结构1401分别连接第四nmos管pd2的源极和漏极。第五接触结构1405和第一接触结构1401分别位于第二栅极结构1302的两侧,表征第五接触结构1405和第一接触结构1401分别连接第二pmos管pu2的源极和漏极。第六接触结构1406连接第二nmos管pg2的栅极。第七接触结构1407和第二接触结构1402分别位于第一栅极结构1301的两侧,表征第七接触结构1407和第二接触结构1402分别连接第一pmos管pu1的源极和漏极。第八接触结构1408和第二接触结构1402分别位于第一栅极结构1301的两侧,表征第八接触结构1408和第二接触结构1402分别连接第三nmos管pd1的源极和漏极。第九接触结构1409和第二接触结构1402分别位于第四栅极结构1304的两侧,表征第九接触结构1409和第二接触结构1402分别连接第一nmos管pg1的漏极和源极。第十接触结构1410连接第一nmos管pg1的栅极。

[0110]

需要说明的是,半导体设备可以通过光刻(photomasking)和刻蚀(etch)等工艺,来制造上述接触结构。半导体设备可以基于包含特定图案的光罩(mask),形成图案化的光刻胶层;再基于图案化的光刻胶层,采用不同刻蚀选择比进行至少一次刻蚀,以在对应位置形成接触结构。

[0111]

可以理解的是,通过有源区、栅极结构和接触结构,用新的物理结构,构建了图9中的存储单元电路。从而在制造存储单元电路的过程中,减少了连接线的使用,节约了加工面积,提高集成电路的集成度;同时,减少了金属布线的过程,简化了加工工艺,能够提高产品良率。

[0112]

在本技术的一些实施例中,在图6示出的s206之后还包括图7示出的s207,将结合各步骤进行说明。

[0113]

s207、设置第一金属线、第二金属线、第三金属线、第四金属线、第五金属线、第六金属线、第七金属线和第八金属线;第一金属线、第二金属线、第三金属线、第四金属线、第五金属线、第六金属线、第七金属线和第八金属线分别依次连接第三接触结构、第四接触结构、第五接触结构、第六接触结构、第七接触结构、第八接触结构、第九接触结构和第十接触结构。

[0114]

本技术实施例中,设计人员在设置了上述接触结构后,可以在版图中的导电材料上设置至少一条金属线,与接触结构电连接。至少一条金属线包括了:第一金属线、第二金属线、第三金属线、第四金属线、第五金属线、第六金属线、第七金属线和第八金属线。

[0115]

参考图5,第一金属线1501、第二金属线1502、第三金属线1503、第四金属线1504、第五金属线1505、第六金属线1506、第七金属线1507和第八金属线1508,分别依次连接第三接触结构1403、第四接触结构1404、第五接触结构1405、第六接触结构1406、第七接触结构1407、第八接触结构1408、第九接触结构1409和第十接触结构1410。

[0116]

在本技术实施例中,金属线和接触结构对应连接,表征了连接在接触结构上的有源区或栅极结构,通过接触结构和金属线,和其他对象电连接。

[0117]

可以理解的是,通过金属线的使用,完成了存储单元电路中各mos端口与对应电连接对象的电连接。

[0118]

图8为本技术实施例提供的sram存储单元电路的一个可选的结构示意图。如图8所示,存储单元电路03中,包括了:开关单元301、第一锁存单元302和第二锁存单元303。

[0119]

开关单元301、第一锁存单元302和第二锁存单元303通过至少一个接触结构连接于点q和点qb;第一锁存单元302连接电源端v

dd

;第二锁存单元303连接接地端;开关单元301连接位线(bit line,bl)和反位线(bit line bar,blb);开关单元301还接收字线(word line,wl)的字线信号。

[0120]

其中,开关单元301,用于在读取状态和写入状态时,在被字线信号触发的情况下,将第一锁存单元302和第二锁存单元303导通于位线bl和blb,以进行存储信号的读取和写入;

[0121]

第一锁存单元302和第二锁存单元303组成锁存电路304,用于对存储信号进行锁定和保存。

[0122]

在本技术的一些实施例中,如图9所示,开关单元301包括:第一nmos管pg1和第二nmos管pg2;第一锁存单元302包括:第一pmos管pu1和第二pmos管pu2;第二锁存单元303包括:第三nmos管pd1和第四nmos管pd2;至少一个接触结构包括:第一接触结构和第二接触结构。

[0123]

本技术实施例中,结合图3和图9,至少一个接触结构包括:第一接触结构1401和第二接触结构1402;第二nmos管pg2的源极为第四nmos管pd2的漏极;第一nmos管pg1的源极为第三nmos管pd1的漏极。

[0124]

第四nmos管pd2的漏极、第二pmos管pu2的漏极和第一pmos管pu1,通过第一接触结构1401连接于点qb(图9中示出)。第三nmos管pd1的漏极、第一pmos管pu1的漏极和第二pmos管pu2的栅极,通过第二接触结构1402连接于点q(图9中示出)。

[0125]

在本技术实施例中,参考图9,位线包括第一位线bl和第二位线blb,二者的信号反相。第一pmos管pu1和第二pmos管pu2的源极还连接电源端v

dd

。第三nmos管pd1和第四nmos管pd2的源极还连接接地端。第一nmos管pg1和第二nmos管pg2的栅极还连接字线wl,接收字线信号。第一nmos管pg1的漏极还连接第一位线bl;第二nmos管pg2的漏极还连接第二位线blb。结合图3和图9,图3中的接触结构,与图9中存储单元电路3的各mos端口、及电连接对象的对应连接关系,如表2所示:

[0126]

接触结构mos端口电连接对象

1401pg2源极、pd2漏极、pu1栅极和pu2漏极qb1402pg1源极、pd1漏极、pu1漏极和pu2栅极q1403pg2漏极blb1404pd2源极接地端1405pu2源极v

dd

1406pg2栅极wl1407pu1源极v

dd

1408pd1源极接地端1409pg1漏极bl1410pg1栅极wl

[0127]

表2

[0128]

在本技术实施例中,第一nmos管pg1,用于在读取状态和写入状态时,在被字线信号触发的情况下,将第一pmos管pu1的漏极、第三nmos管pd1的漏极、第二pmos管pu2的栅极、第四nmos管pd2的栅极和第一位线bl导通,以进行存储信号的读取和写入。

[0129]

第二nmos管pg2,用于在读取状态和写入状态时,在被字线信号触发的情况下,将第二pmos管pu2的漏极、第四nmos管pd2的漏极、第一pmos管pu1的栅极、第三nmos管pd1的栅极和第二位线blb导通,以进行存储信号的读取和写入。

[0130]

可以理解的是,通过第一接触结构1401,直接连接了第四nmos管pd2的漏极、第二pmos管pu2的漏极、第一pmos管pu1的栅极和第三nmos管pd1的栅极;通过第二接触结构1402,直接连接了第三nmos管pd1的漏极、第一pmos管pu1的漏极、第二pmos管pu2的栅极和第四nmos管pd2的栅极。这样,减少了连接线的使用,从而,能够节约加工面积,提高集成电路的集成度;同时,减少了金属布线的过程,从而,简化了加工工艺,能够提高产品良率。

[0131]

本技术实施例还提供了一种半导体结构800,如图10所示。半导体结构800由前述实施例提供的版图示出。从而,能够减少连接线的使用,提高集成电路的集成度;减少金属布线的过程,简化加工工艺,提高产品良率。

[0132]

本技术实施例还提供了一种半导体存储器900,如图10所示,半导体存储器900至少包括图10示出的半导体结构800。

[0133]

需要说明的是,在本技术中,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者装置不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者装置所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括该要素的过程、方法、物品或者装置中还存在另外的相同要素。

[0134]

上述本技术实施例序号仅仅为了描述,不代表实施例的优劣。本技术所提供的几个方法实施例中所揭露的方法,在不冲突的情况下可以任意组合,得到新的方法实施例。本技术所提供的几个产品实施例中所揭露的特征,在不冲突的情况下可以任意组合,得到新的产品实施例。本技术所提供的几个方法或设备实施例中所揭露的特征,在不冲突的情况下可以任意组合,得到新的方法实施例或设备实施例。

[0135]

以上所述,仅为本技术的具体实施方式,但本技术的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本技术揭露的技术范围内,可轻易想到变化或替换,都应涵

盖在本技术的保护范围之内。因此,本技术的保护范围应以所述权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1