硬盘模拟装置及应用该装置的测试系统及其测试方法与流程

1.本发明涉及一种监测与控制系统及其方法,特别是硬盘模拟装置及应用该装置的测试系统及其测试方法。

背景技术:

2.近年来,随着自动化测试的普及与蓬勃发展,许多厂商纷纷将其应用在生产线。然而,在实际进行测试时,往往需要搭配相应的零组件,导致测试成本高昂且维护困难。因此,已经成为各家厂商亟欲解决的问题。

3.一般而言,假设要对待测装置的硬盘连接端口进行测试,如:nvme连接端口,则搭配的零组件为硬盘。当待测装置存在多个硬盘连接端口且欲同时进行测试时,便需要准备相应数量的实际的硬盘,并且设置在待测装置以便用于测试。然而,大量实际的硬盘不但维护困难,同时也使得测试成本居高不下,特别是硬盘有读写次数的物理限制,长时间的测试将导致硬盘使用寿命大幅缩短。因此,传统的测试方式具有待测装置的测试成本高昂的问题。

4.综上所述,可知现有技术中长期以来一直存在待测装置的测试成本高昂的问题,因此实有必要提出改进的技术手段,来解决此问题。

技术实现要素:

5.本发明公开一种硬盘模拟装置及应用该装置的测试系统及其测试方法。

6.首先,本发明公开一种硬盘模拟装置,此装置包含:电路板及检测电路。其中,电路板一端允许与待测装置电性连接,此电路板另一端设置第一连接端口及一组第二连接端口,所述第一连接端口允许通过排线电性连接另一硬盘模拟装置的第一连接端口,当连接排线时,使设置在待测装置且分别对应于不同硬盘模拟装置的两个数字信号处理器之间的总线信号相互连接且与待测装置的处理单元形成回路。接着,所述第二连接端口允许通过传输线串接其它硬盘模拟装置及待测装置;以及检测电路设置在电路板上,并且电性连接多个引脚,所述引脚包含电源引脚、时脉引脚及系统管理总线,所述检测电路包含:模数转换器(analog-to-digital converter,adc)、电子可擦除可编程只读存储器(electrically-erasable programmable read-only memory,eeprom)及复杂可编程逻辑装置(complex programmable logic device,cpld)。其中,模数转换器电性连接电源引脚,用以读取电源引脚的电压;电子可擦除可编程只读存储器电性连接系统管理总线,用以储存在系统管理总线传输的总线数据,并且允许待测装置存取总线数据以验证系统管理总线的正确性;以及复杂可编程逻辑装置电性连接时脉引脚,用以接收时脉信号,以及通过此组第二连接端口读取时脉信号的频率以验证正确性。

7.接着,本发明公开一种应用硬盘模拟装置的测试系统,此系统包含:多个硬盘模拟装置及待测装置。其中,每一硬盘模拟装置皆包含第一连接端口、一组第二连接端口及检测电路,此检测电路电性连接电源引脚、时脉引脚及系统管理总线,当硬盘模拟装置接收到检

测指令时,驱动检测电路检测电源引脚、时脉引脚及系统管理总线的信号以产生检测结果并进行传送;以及待测装置,此待测装置包含:多个插槽、测试连接端口及处理单元。其中,每一插槽电性连接相应的数字信号处理器,当硬盘模拟装置插入插槽且通过排线串接硬盘模拟装置的第一连接端口时,使设置在待测装置且分别对应于不同硬盘模拟装置的数字信号处理器之间的总线信号相互连接;测试连接端口与已插入至插槽的硬盘模拟装置的此组第二连接端口通过多个传输线相互串接;以及处理单元电性连接所述测试连接端口及数字信号处理器,使处理单元与已通过排线串接且插入至插槽的硬盘模拟装置及其相应的数字信号处理器形成回路,并且执行测试程序以读取每一所述插槽上的信号连接状态,以及通过测试连接端口传送检测指令至所有通过传输线串接的硬盘模拟装置,并且接收信号连接状态及硬盘模拟装置产生的检测结果以验证正确性并进行输出。

8.另外,本发明还公开一种应用硬盘模拟装置的测试方法,其步骤包括:提供待测装置及多个硬盘模拟装置,其中,此待测装置包含多个插槽、测试连接端口及处理单元,每一硬盘模拟装置皆包含第一连接端口、一组第二连接端口及检测电路,此检测电路电性连接电源引脚、时脉引脚及系统管理总线;将硬盘模拟装置分别插入插槽,并且通过排线串接硬盘模拟装置的第一连接端口,使设置在待测装置且分别对应于不同硬盘模拟装置的两个数字信号处理器之间的总线信号相互连接且与待测装置的处理单元形成回路,以及通过多个传输线串接所有硬盘模拟装置的此组第二连接端口及待测装置的测试连接端口;待测装置执行测试程序以读取每一插槽上的信号连接状态,以及通过测试连接端口传送检测指令至所有通过传输线串接的硬盘模拟装置;当硬盘模拟装置接收到检测指令时,驱动检测电路检测电源引脚、时脉引脚及系统管理总线的信号以产生检测结果,并且将产生的检测结果传送至测试程序;以及测试程序接收信号连接状态及硬盘模拟装置产生的检测结果以验证正确性并进行输出。

9.本发明所公开的装置、系统与方法如上,与现有技术的差异在于本发明是通过提供具有检测电路的硬盘模拟装置以连接待测装置,并且串接硬盘模拟装置及待测装置的测试连接端口,以便在待测装置执行测试程序时,读取待测装置的插槽的信号连接状态,以及通过测试连接端口传送检测指令驱动硬盘模拟装置的检测电路检测电源引脚、时脉引脚及系统管理总线的信号以产生检测结果,进而根据信号连接状态及检测结果验证待测装置的正确性。

10.通过上述的技术手段,本发明可以达成降低待测装置的测试成本的技术功效。

附图说明

11.图1为本发明硬盘模拟装置的方框图。

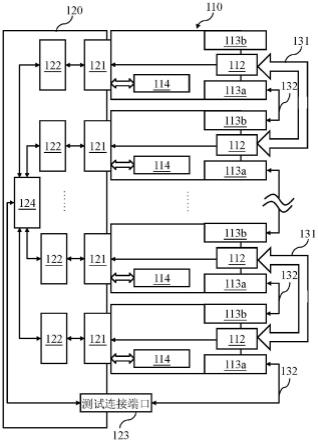

12.图2为应用本发明硬盘模拟装置的测试系统的系统方框图。

13.图3为应用本发明硬盘模拟装置的测试方法的方法流程图。

14.附图标记说明:

15.110

ꢀꢀꢀꢀꢀꢀꢀꢀ

硬盘模拟装置

16.111

ꢀꢀꢀꢀꢀꢀꢀꢀ

电路板

17.112

ꢀꢀꢀꢀꢀꢀꢀꢀ

第一连接端口

18.113a、113b 第二连接端口

19.114

ꢀꢀꢀꢀꢀꢀꢀꢀ

检测电路

20.120

ꢀꢀꢀꢀꢀꢀꢀꢀ

待测装置

21.121

ꢀꢀꢀꢀꢀꢀꢀꢀ

插槽

22.122

ꢀꢀꢀꢀꢀꢀꢀꢀ

数字信号处理器

23.123

ꢀꢀꢀꢀꢀꢀꢀꢀ

测试连接端口

24.124

ꢀꢀꢀꢀꢀꢀꢀꢀ

处理单元

25.131

ꢀꢀꢀꢀꢀꢀꢀꢀ

排线

26.132

ꢀꢀꢀꢀꢀꢀꢀꢀ

传输线

具体实施方式

27.以下将配合图式及实施例来详细说明本发明的实施方式,借此对本发明如请先参阅图1,图1为本发明硬盘模拟装置的方框图,此硬盘模拟装置110包含:电路板111及检测电路114。其中,电路板111一端允许与待测装置电性连接,此电路板111另一端设置第一连接端口112及一组第二连接端口(113a、113b),所述第一连接端口112允许通过排线电性连接另一硬盘模拟装置110的第一连接端口112,当连接排线时,使设置在待测装置且分别对应于不同硬盘模拟装置110的两个数字信号处理器之间的总线信号相互连接(如:pcie信号连接)且与待测装置的处理单元形成回路。接着,所述第二连接端口(113a、113b)允许通过传输线串接其它硬盘模拟装置110及待测装置。在实际实施上,电路板111与待测装置电性连接的一端可为符合“nvme”规格或其相似规格的连接器,用以与待测装置的“nvme”插槽或其相似物连接;所述第一连接端口可为柔性扁平排线(flexible flat cable,ffc)连接器或其相似物;所述排线可为柔性扁平排线或其相似物;所述第二连接端口可为“rs232”串列端口或其相似物,而传输线则可为“rs232”传输线或相似物。

28.检测电路114设置在电路板111上,并且电性连接多个引脚,所述引脚包含电源(power)引脚、时脉(clk)引脚及系统管理总线(smbus),所述检测电路114包含:模数转换器、电子可擦除可编程只读存储器及复杂可编程逻辑装置。其中,模数转换器电性连接电源引脚,用以读取电源引脚的电压。举例来说,每一个电源引脚都单独连接到模数转换器上,通过模数转换器读取每一个引脚的电压,以便由检测程序判断电压是否符合规范来确认每一个电源引脚的状态。

29.电子可擦除可编程只读存储器电性连接系统管理总线,用以储存在系统管理总线传输的总线数据,并且允许待测装置存取总线数据以验证系统管理总线的正确性。举例来说,通过检测程序存取eeprom中的数据,从而验证系统管理总线的正确性。

30.复杂可编程逻辑装置电性连接时脉引脚,用以接收时脉信号,以及通过此组第二连接端口(113a、113b)读取时脉信号的频率以验证正确性。以第二连接端口为rs232连接端口为例,可通过复杂可编程逻辑装置接收100m的clk信号,然后再通过rs232连接端口读取clk信号的频率来验证其正确性。

31.如图2所示意,图2为应用本发明硬盘模拟装置的测试系统的系统方框图,此系统包含:多个硬盘模拟装置110及待测装置120。其中,每一硬盘模拟装置110皆包含第一连接端口112、一组第二连接端口(113a、113b)及检测电路114,此检测电路114电性连接电源引脚、时脉引脚及系统管理总线,当硬盘模拟装置110接收到检测指令时,驱动检测电路114检

测电源引脚、时脉引脚及系统管理总线的信号以产生检测结果并进行传送。在实际实施上,第一连接端口112负责将通过排线相连接的两个硬盘模拟装置110的pcie信号连接在一起,以此来使相应的两个数字信号处理器122连接在一起。此时,每个pcie下行端口(downstream port)都有一组暂存器(register)来表示其支持pcie特征和当前的pcie状态。作业系统可通过读取这些暂存器来得知这个pcie下行端口的实际连接状态,进而验证当前的两个插槽121的连接状况。要补充说明的是,在测试高频信号时,还可针对pcie信号进行各项测试,例如:连接速度(link speed)、连接频宽(link width)、连接速度变化(link speed change)等等。这三个测试项目都是通过控制待测装置120的pcie下行端口来实现。具体逻辑是,以连接速度及连接频宽为例,通过pcie下行端口的相关暂存器来确认当前的状态,进而判断是否正确。接着,以连接速度变化为例,需要测试程序通过控制pcie下行端口的相关暂存器来实现连接速度在“gen4/3/2/1”四种状态中逐一切换,并且验证切换后与待测装置120的连接状态,进而验证待测装置120对不同速度的兼容性及连接稳定性。

32.除此之外,所述第二连接端口(113a、113b)有两个,一个输入,一个输出,通过传输线串接不同的硬盘模拟装置110,而待测装置120只需一条传输线连接第二连接端口113a及测试连接端口123。特别要说明的是,每一个硬盘模拟装置110具有唯一识别码,并且通过寻址来识别不同的硬盘模拟装置110,从而实现通信。所述检测电路114可将读取到的电源引脚的电压、存取的总线数据及通过此组第二连接端口(113a、113b)读取到的时脉信号的频率一并输出为检测结果。

33.接着,在待测装置120的部分,其包含:多个插槽121、测试连接端口123及处理单元124。其中,每一插槽121电性连接相应的数字信号处理器122,当硬盘模拟装置110插入插槽121且通过排线131串接硬盘模拟装置110的第一连接端口112时,使设置在待测装置120且分别对应于不同硬盘模拟装置110的数字信号处理器122之间的总线信号相互连接。在实际实施上,所述数字信号处理器122包含下行端口(downstream port)及其相应的暂存器,当测试程序执行时,可读取下行端口的暂存器以确认当前连接状态,以及逐一切换连接速度,并且在切换后验证硬盘模拟装置110与待测装置120的连接状态。

34.测试连接端口123与已插入至插槽121的硬盘模拟装置110的此组第二连接端口(113a、113b)通过多个传输线132相互串接。以图2为例,测试连接端口123可通过一条传输线132连接至图式下方的硬盘模拟装置110的第二连接端口113a,而此硬盘模拟装置110的第二连接端口113b同样通过一条传输线132连接另一个硬盘模拟装置110的第二连接端口113a,并且以此类推,使用传输线132将所有硬盘模拟装置110及待测装置120串接在一起。

35.处理单元124电性连接测试连接端口123及数字信号处理器122,使处理单元124与已经通过排线131串接且已经插入至插槽121的硬盘模拟装置110及其相应的数字信号处理器122形成回路,并且执行测试程序以读取每一插槽121上的信号连接状态(如:pcie差分信号的状态),以及通过测试连接端口123传送检测指令至所有通过传输线132串接的硬盘模拟装置110,并且接收信号连接状态及硬盘模拟装置110产生的检测结果以验证正确性并进行输出。在实际实施上,处理单元124可以通过微控制单元(micro controller unit,mcu)、微处理器(microprocessor)、中央处理器(central processing unit,cpu)、系统单芯片(system on a chip,soc)等等来实现,用以执行计算机指令,如:检测、比对、读取、写入等等。以测试nvme的pcie差分信号为例,当两个硬盘模拟装置110分别插入相应的插槽121

(nvme slot),并且以排线131电性连接这两个硬盘模拟装置110的第一连接端口112时,处理单元124与这两个硬盘模拟装置110及其相应的数字信号处理器122便形成一个回路(loop),如此一来,处理单元124在执行测试程序时,便可利用两个pcie下行端口之间相连(link)的方法来测试nvme的pcie差分信号。特别要说明的是,此部分的pcie差分信号的测试与测试连接端口123无关,所述测试连接端口123仅用于测量电源引脚、系统管理总线及时脉引脚的信号。

36.特别要说明的是,在实际实施上,所述测试程序为计算机程序,可以包括计算机可读储存介质,其上载有用于使处理器实现本发明的各个方面的计算机可读程序指令,计算机可读储存介质可以是可以保持和储存由指令执行设备使用的指令的有形设备。计算机可读储存介质可以是但不限于电储存设备、磁储存设备、光储存设备、电磁储存设备、半导体储存设备或上述的任意合适的组合。计算机可读储存介质的更具体的例子(非穷举的列表)包括:硬盘、随机存取存储器、只读存储器、快闪存储器、光盘、软盘以及上述的任意合适的组合。此处所使用的计算机可读储存介质不被解释为瞬时信号本身,诸如无线电波或者其它自由传播的电磁波、通过波导或其它传输介质传播的电磁波(例如,通过光纤电缆的光信号)、或者通过电线传输的电信号。另外,此处所描述的计算机可读程序指令可以从计算机可读储存介质下载到各个计算/处理设备,或者通过网络,例如:网际网络、区域网络、广域网络和/或无线网络下载到外部计算机设备或外部储存设备。网络可以包括铜传输电缆、光纤传输、无线传输、路由器、防火墙、交换器、集线器和/或网关。每一个计算/处理设备中的网卡或者网络接口从网络接收计算机可读程序指令,并转发此计算机可读程序指令,以供储存在各个计算/处理设备中的计算机可读储存介质中。执行本发明操作的计算机程序指令可以是组合语言指令、指令集架构指令、机器指令、机器相关指令、微指令、固件指令、或者以一种或多种程序语言的任意组合编写的原始码或目的码(object code),所述程序语言包括面向对象的程序语言,如:common lisp、python、c++、objective-c、smalltalk、delphi、java、swift、c#、perl、ruby与php等,以及常规的程序式(procedural)程序语言,如:c语言或类似的程序语言。所述计算机程序指令可以完全地在计算机上执行、部分地在计算机上执行、作为一个独立的软件执行、部分在客户端计算机上部分在远端计算机上执行、或者完全在远端计算机或服务器上执行。

37.请参阅图3,图3为应用本发明硬盘模拟装置的测试方法的方法流程图,其步骤包括:提供待测装置120及多个硬盘模拟装置110,其中,此待测装置120包含多个插槽121、测试连接端口123及处理单元124,每一硬盘模拟装置110皆包含第一连接端口112、一组第二连接端口(113a、113b)及检测电路114,此检测电路114电性连接电源引脚、时脉引脚及系统管理总线(步骤210);将硬盘模拟装置110分别插入插槽121,并且通过排线131串接硬盘模拟装置110的第一连接端口112,使设置在待测装置120且分别对应于不同硬盘模拟装置110的两个数字信号处理器122之间的总线信号相互连接且与待测装置120的处理单元124形成回路,以及通过多个传输线132串接所有硬盘模拟装置110的此组第二连接端口(113a、113b)及待测装置120的测试连接端口123(步骤220);待测装置120执行测试程序以读取每一插槽121上的信号连接状态,以及通过测试连接端口123传送检测指令至所有通过传输线132串接的硬盘模拟装置110(步骤230);当硬盘模拟装置110接收到检测指令时,驱动检测电路114检测电源引脚、时脉引脚及系统管理总线的信号以产生检测结果,并且将产生的检

测结果传送至测试程序(步骤240);以及测试程序接收信号连接状态及硬盘模拟装置110产生的检测结果以验证正确性并进行输出(步骤250)。

38.综上所述,可知本发明与现有技术之间的差异在于通过提供具有检测电路的硬盘模拟装置以连接待测装置,并且串接硬盘模拟装置及待测装置的测试连接端口,以便在待测装置执行测试程序时,读取待测装置的插槽的信号连接状态,以及通过测试连接端口传送检测指令驱动硬盘模拟装置的检测电路检测电源引脚、时脉引脚及系统管理总线的信号以产生检测结果,进而根据信号连接状态及检测结果验证待测装置的正确性,借由此技术手段可以解决现有技术所存在的问题,进而达成降低待测装置的测试成本的技术功效。

39.虽然本发明以前述的实施例公开如上,然而其并非用以限定本发明,任何本领域技术人员,在不脱离本发明的精神和范围内,当可作些许的更动与润饰,因此本发明的专利保护范围须视本说明书所附的权利要求书所界定的范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1