一种数据访问系统、方法及相关设备与流程

本技术涉及存储领域,尤其涉及一种数据访问系统、方法及相关设备。

背景技术:

1、随着科学技术的不断发展,信息爆炸时代产生的海量数据已经渗透到当今每一个行业和业务职能领域,大数据(big data)和人工智能(artificial intelligence,ai)领域也随之得到了发展,成为两个非常热门的研究方向。

2、计算节点在执行数据处理时(例如:大数据或者ai任务),常需要较大的内存容量来存储数据,通常情况下,可将数据分布式地放在多台存储节点的内存中,计算节点可通过远程直接内存访问(remote direct memory access,rdma)协议读取存储节点内存中的数据,实现内存容量的扩展。

3、但是,rdma协议下,计算节点与存储节点之间的通信通过网卡实现,二者的网卡之间通过网卡队列进行数据传输,使得计算节点每次读取数据都需要将数据读取请求放入网卡队列,导致数据读取过程消耗大量时间在队列单元的准备上,甚至一些情况下,队列单元的准备时间相比数据传输的时间更长,导致计算节点数据访问效率低,网络延迟高,影响大数据或者ai任务的处理效率。

技术实现思路

1、本技术提供了一种数据访问系统、方法及相关设备,用于解决计算节点访问存储节点内存时的访问效率低、网络延迟高的问题。

2、第一方面,提供了一种数据访问系统,该数据访问系统包括第一节点和第二节点,第一节点与第二节点通过线缆连接;第一节点用于生成数据访问请求,其中,数据访问请求用于请求第二节点的内存中的数据;第一节点用于通过线缆发送数据访问请求至第二节点;第二节点用于将数据访问请求中的第一目的地址转换为第一目的地址对应的本地物理地址,并根据本地物理地址访问第二节点的内存中的数据。

3、实施第一方面描述的系统,第一节点和第二节点通过线缆连接,二者之间的通信交互无需通过网卡或路由设备,使得第一节点访问第二节点内存时无需额外等待网卡队列单元的准备时间,从而提高第一节点访问第二节点内存的效率,降低访问时延。

4、在一可能的实现方式中,第一节点包括计算芯片和互联芯片,其中,互联芯片的第一高速互联端口与第二节点中的处理器的第二高速互联端口通过线缆连接,计算芯片通过端口与互联芯片相连,计算芯片用于生成数据访问请求,并将数据访问请求发送至互联芯片,互联芯片用于通过线缆发送数据访问请求至第二节点。

5、计算芯片可以由至少一个通用处理器构成,例如cpu、npu或者cpu和硬件芯片的组合。上述硬件芯片可以是专用集成电路(application-specific integrated circuit,asic)、可编程逻辑器件(programmable logic device,pld)或其组合。上述pld可以是复杂可编程逻辑器件(complex programmable logic device,cpld)、现场可编程逻辑门阵列(field-programmable gate array,fpga)、通用阵列逻辑(generic array logic,gal)或其任意组合。其中,第一节点内的计算芯片的数量可以是一个或者多个,本技术不作具体限定。

6、互联芯片可以是asic、pld或其组合,上述pld可以是cpld、fpga、gal或其任意组合,本技术不作具体限定。其中,第一节点中互联芯片的数量可以是多个,本技术不作具体限定。互联芯片上设置有高速互联端口,互联芯片可通过高速互联端口与第二节点进行数据通信,互联芯片的第一高速互联端口与第二节点上的第二高速互联端口通过线缆连接,需要说明的,每个互联芯片上的第一高速互联端口的数量可以是一个或者多个,每个第一高速互联端口与第二节点上的第二高速互联端口呈一一对应关系。

7、高速互联端口可以是高速串行总线端口,比如serdes总线端口,线缆可以是电缆、光纤、双绞线等可以传输数据的线缆,本技术不对线缆进行具体限定。其中,第一节点上高速互联端口的数量可以是一个或者多个,且第一节点上的第一高速互联端口与第二节点上的第二高速互联端口呈一一对应的关系。

8、计算芯片的端口可以是高速串行总线端口,比如serdes总线端口,计算芯片可以通过总线与互联芯片相连,总线可以是外设部件互联标准(peripheral componentinterconnect,pci)总线或扩展工业标准结构(extended industry standardarchitecture,eisa)总线等,计算芯片、互联芯片、计算芯片的端口和总线可以在加工时统一印制在电路板上。具体实现中,计算芯片的端口的数量可以是一个或者多个,本技术不对此进行限定。

9、实施上述实现方式,在第一节点中部署互联芯片,可以使得第一节点可以与更多的第二节点进行通信,互联芯片的数量越多,第一节点中可部署的高速互联端口的数量越多,使得与第一节点相连的第二节点数量越多,从而扩大第一节点的内存扩展能力,使得第一节点可以适用于更多的应用场景。

10、在另一可能的实现方式中,第一节点的计算芯片、互联芯片和第二节点之间的数据通信可通过地址译码器实现寻址功能。

11、可选地,计算芯片中包括第一地址译码器,计算芯片具体用于:生成数据访问请求,根据数据访问请求中的第一目的地址和第一地址译码器确定第一端口,通过第一端口向互联芯片发送数据访问请求,其中,第一地址译码器用于记录目的地址与计算芯片的端口之间的对应关系。

12、可选地,计算芯片中部署有第一地址译码器,计算芯片具体用于生成数据访问请求,根据数据访问请求中的第一目的地址和第一地址译码器确定第一端口,通过第一端口向互联芯片发送数据访问请求,其中,第一地址译码器可记录目的地址与计算芯片的端口之间的对应关系。

13、可选地,互联芯片中部署有第二地址译码器,互联芯片具体用于根据第一目的地址和第二地址译码器确定第一高速互联端口,通过第一高速互联端口向第二节点发送数据访问请求,其中,第二地址译码器用于记录目的地址与高速互联端口之间的对应关系。

14、可选地,第二节点中部署有第三地址译码器,第二节点具体用于根据第一目的地址和第三地址译码器,确定第一目的地址对应的本地物理地址,其中,第三地址译码器用于记录目的地址与本地物理地址之间的对应关系。其中,第三地址译码器记录的对应关系可以是:本地物理地址=目的地址-基地址,其中,基地址指的是一个地址段的起始地址,又称为首地址或者段地址,属于同一个地址段的目的地址的基地址相同。

15、可选地,该数据访问系统还可包括配置节点,配置节点可以对第一地址译码器、第二地址译码器以及第三地址译码器进行配置。具体地,配置节点用于向第二节点获取第二节点的内存的至少一个本地物理地址,配置节点用于根据至少一个本地物理地址确定对应的至少一个目的地址,对第三地址译码器进行配置;配置节点还用于根据至少一个目的地址,结合第二节点与互联芯片之间的高速互联端口,对第二地址译码器进行配置;配置节点还用于根据至少一个目的地址,结合互联芯片与计算芯片之间的芯片端口,对第一地址译码器进行配置。

16、具体实现中,配置节点向第二节点获取第二节点的内存的至少一个本地物理地址时,可以根据第二节点内存的大小,结合业务需求,确定第二节点划分出来供第一节点使用的拓展内存的本地物理地址。可选地,供第一节点使用的拓展内存可以是第二节点的部分内存,该部分拓展内存可以通过内存隔离技术进行处理,使得第二节点无法访问该部分拓展内存,提高拓展内存中存储的数据的安全性。

17、实施上述实现方式,通过配置节点配置的第一、第二和第三地址译码器,可以确保计算芯片生成的数据访问请求通过地址译码器路由寻址,将数据访问请求传输至目的地址对应的第二节点的cpu进行内存读写,从而免于网卡队列准备的等待时间,提高第一节点对拓展内存读写的效率,时延甚至能达到微秒级别(以太网时延可以达到毫秒级),带宽可以达到400gb,相比带宽只有100gb的rdma网卡,拥有更高的带宽和时延。

18、在另一可能的实现方式中,在将第一目的地址与第一地址译码器和第二地址译码器进行匹配时,可以将完整或部分第一目的地址与译码器中的地址进行匹配,从而提高匹配效率,进而提高数据访问的效率。

19、可选地,可根据数据访问请求中第一目的地址的基地址和长度确定第一端口。具体地,计算芯片具体用于将第一地址译码器中记录的目的地址的基地址和长度与第一目的地址的基地址和长度进行匹配,确定匹配后的目的地址对应的第一端口。同理,互联芯片具体用于将第二地址译码器中记录的目的地址的基地址和长度与第二目的地址的基地址和长度进行匹配,确定匹配后的目的地址对应的第一高速互联端口。这里不再展开赘述。

20、可选地,可根据第一目的地址的高位地址确定第一端口。计算芯片具体用于将第一地址译码器中记录的目的地址的高位地址与第一目的地址的高位地址进行匹配,确定匹配后的目的地址对应的第一端口,其中,高位地址的位数是根据第二节点的内存大小确定的。同理,互联芯片具体用于将第二地址译码器中记录的目的地址的高位地址与第一目的地址的高位地址进行匹配,确定匹配后的目的地址对应的第一高速互联端口。这里不再展开赘述。

21、举例来说,假设目的地址总长度为64bit,若一个高速互联端口对应的第二节点120的内存为1t,那么这1t内存的目的地址中,后30bit的地址不同,那么高位地址的位数可以是64-30=34bit,简单来说,位于同一个内存的目的地址前34bit是相同的,后面30bit不同,因此,根据高速互联端口所连接的第二节点120的拓展内存大小,可以确定高位地址的位数。

22、应理解,由于第二节点提供的拓展内存对应的物理地址数量为多个,因此第一、第二译码器中记录的部分目的地址对应的端口可能会是同一个,对应相同端口的目的地址位于同一个内存中,这些对应相同端口的目的地址,其基地址和长度是相同的,或者,其高位地址是相同的,因此可以通过匹配基地址和长度,或者匹配高位地址来确定第一目的地址对应的端口。

23、实施上述实现方式,将部分第一目的地址与译码器中的地址进行匹配,可以提高匹配效率,提高第一端口和第一高速互联端口的确定效率,进而提高数据访问的效率。

24、需要说明的,若数据访问请求是向第二节点读取内存中的数据,第二节点对数据访问请求进行处理后,可以根据数据访问请求中的源地址,结合第一、第二和第三地址译码器,将读取到的数据原路返回至第一节点中,这里不在重复再开赘述。

25、需要说明的,在一些实施例中,第一节点也可以不包括互联芯片,计算芯片上的高速互联端口与第二节点上的高速互联端口通过线缆连接,计算芯片也可通过上述地址译码器实现数据访问请求的路由寻址。具体地,计算芯片可部署有第二地址译码器,第二节点部署有第三地址译码器230,计算芯片生成的数据访问请求可根据第二地址译码器中记录的高速互联端口和目的地址之间的对应关系,确定第一目的地址对应的第一高速互联端口,然后通过第一高速互联端口向第二节点发送该数据访问请求,这里不展开赘述。

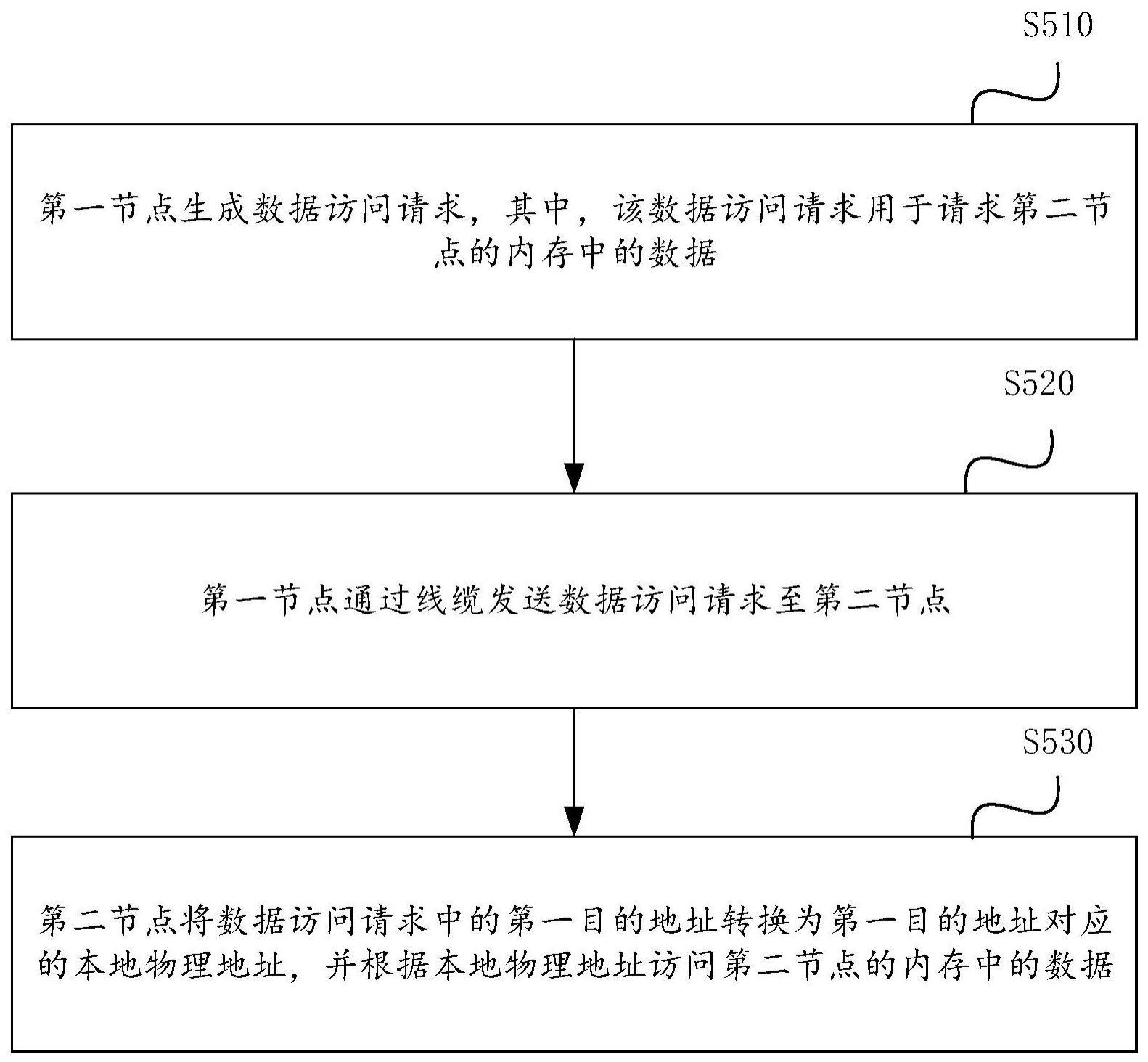

26、第二方面,提供了一种数据访问方法,该方法应用于数据访问系统,该数据访问系统包括第一节点和第二节点,第一节点与第二节点通过线缆连接,该方法包括以下步骤:第一节点生成数据访问请求,其中,数据访问请求用于请求第二节点的内存中的数据,第一节点通过线缆发送数据访问请求至第二节点,第二节点将数据访问请求中的第一目的地址转换为第一目的地址对应的本地物理地址,并根据本地物理地址访问第二节点的内存中的数据。

27、实施第二方面描述的方法,第一节点和第二节点通过线缆连接,二者之间的通信交互无需通过网卡或路由设备,使得第一节点访问第二节点内存时无需额外等待网卡队列单元的准备时间,从而提高第一节点访问第二节点内存的效率,降低访问时延。

28、在一可能的实现方式中,第一节点包括计算芯片和互联芯片,其中,互联芯片的第一高速互联端口与第二节点中的处理器的第二高速互联端口通过线缆连接,计算芯片可以生成数据访问请求,并将数据访问请求发送至互联芯片,互联芯片通过线缆发送数据访问请求至第二节点。

29、在一可能的实现方式中,计算芯片通过端口与互联芯片相连,计算芯片中包括第一地址译码器,计算芯片可生成数据访问请求,根据数据访问请求中的第一目的地址和第一地址译码器确定第一端口,通过第一端口向互联芯片发送数据访问请求,其中,第一地址译码器用于记录目的地址与计算芯片的端口之间的对应关系。

30、在一可能的实现方式中,互联芯片中包括第二地址译码器,互联芯片根据第一目的地址和第二地址译码器确定第一高速互联端口,通过第一高速互联端口向第二节点发送数据访问请求,其中,第二地址译码器用于记录目的地址与高速互联端口之间的对应关系。

31、在一可能的实现方式中,第二节点包括第三地址译码器,第二节点根据第一目的地址和第三地址译码器,确定第一目的地址对应的本地物理地址,其中,第三地址译码器用于记录目的地址和本地物理地址之间的对应关系。

32、在一可能的实现方式中,数据访问系统还包括配置节点,上述方法还包括以下步骤:配置节点向第二节点获取第二节点的内存的至少一个本地物理地址,配置节点根据至少一个本地物理地址确定对应的至少一个目的地址,对第三地址译码器进行配置,配置节点根据至少一个目的地址,结合第二节点与互联芯片之间的高速互联端口,对第二地址译码器进行配置,配置节点据至少一个目的地址,结合互联芯片与计算芯片之间的芯片端口,对第一地址译码器进行配置。

33、在一可能的实现方式中,计算芯片将第一地址译码器中记录的目的地址的基地址和长度与第一目的地址的基地址和长度进行匹配,确定匹配后的目的地址对应的第一端口,互联芯片将第二地址译码器中记录的目的地址的基地址和长度与第一目的地址的基地址和长度进行匹配,确定匹配后的目的地址对应的第一高速互联端口。

34、在一可能的实现方式中,计算芯片将第一地址译码器中记录的目的地址的高位地址与第一目的地址的高位地址进行匹配,确定匹配后的目的地址对应的第一端口,其中,高位地址的位数是根据第二节点的内存大小确定的,互联芯片将第二地址译码器中记录的目的地址的基地址和长度与第一目的地址的基地址和长度进行匹配,确定匹配后的目的地址对应的第一高速互联端口。

35、在一可能的实现方式中,第一高速互联端口和第二高速互联端口为高速串行总线端口,第一端口为高速串行总线端口。

36、第三方面,提供了一种计算节点,该计算节点可以是第一方面和第二方面描述的第一节点,该计算节点应用于数据访问系统,数据访问系统还包括存储节点,计算节点包括:计算芯片和互联芯片,其中,计算芯片的通过高速互联端口与互联芯片连接,互联芯片通过高速互联端口和线缆与其他节点连接;计算芯片用于生成数据访问请求,并将数据访问请求发送至互联芯片,其中,数据访问请求包括第一目的地址,第一目的地址指示存储节点中的内存的位置;互联芯片用于根据第一目的地址将数据访问请求发送至存储节点。

37、第四方面,提供了一种存储节点,该存储节点可以是第一方面和第二方面描述的第二节点,该存储节点应用于数据访问系统,数据访问系统还包括计算节点,存储节点包括处理器和内存,存储节点通过处理器的高速互联端口和线缆与计算节点连接;处理器用于通过高速互联端口接收计算节点发送的数据访问请求,将数据访问请求中的携带的第一目的地址转换为第一目的地址对应的存储节点的本地物理地址,并根据本地物理地址访问内存中的数据。

38、第五方面,提供了一种计算设备,该计算设备包括处理器和存储器,存储器存储有代码,处理器包括用于执行第一方面或第一方面任一种可能实现方式中第一节点或第二节点实现的各个模块的功能。

39、第六方面,提供了一种计算机可读存储介质,所述计算机可读存储介质中存储有指令,当其在计算机上运行时,使得计算机执行上述各方面所述的方法。

40、本技术在上述各方面提供的实现方式的基础上,还可以进行进一步组合以提供更多实现方式。

- 还没有人留言评论。精彩留言会获得点赞!