高效双路径浮点算术运算符的制作方法

1.本公开涉及被设计为执行浮点算术的集成电路。更具体地,本公开涉及产生高效的双路径浮点运算符和/或在浮点运算符中的高效的计数前导零电路。

背景技术:

2.集成电路设备可以利用基于硬化电路的浮点运算符来对浮点数执行浮点运算。随着集成电路设备内浮点运算符的数量的增加,对实现浮点运算符的效率的需求可能会增加。例如,先前的集成电路设备可能包括数十到数百个浮点运算符,而即将到来的集成电路设备设计可能包括数千或数万个浮点运算符。因此,由于浮点运算符的数量的增加,适用于先前的集成电路设备的效率水平可能不那么适用于即将到来的设备。

3.本节旨在向读者介绍可能与本公开的各种方面相关的本领域的各种方面,这些方面在下面描述和/或要求保护。该讨论被认为有助于向读者提供背景信息以促进更好地理解本公开的各种方面。因此,这些陈述将根据这一点阅读,而不是作为对现有技术的承认。

附图说明

4.在阅读以下详细描述并且参考附图之后,可以更好地理解本公开的各种方面,在附图中:

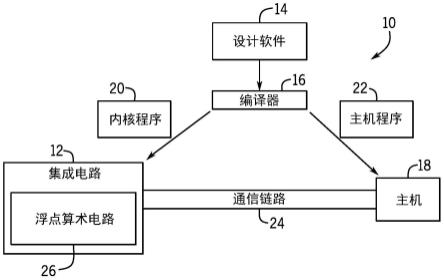

5.图1是根据本公开实施例的用于实现浮点加法的系统的框图;

6.图2是根据本公开的实施例的其中可以实现浮点加法器的集成电路的框图;

7.图3是根据本公开的实施例的可以在集成电路中实现的单路径浮点加法器的框图;

8.图4是根据本公开的实施例的可以在集成电路中实现的使用用于一条路径的专用减法器的双路径浮点加法器的框图;

9.图5是根据本公开的实施例的可以在图3或图4的浮点加法器中实现的加法和舍入电路(adding and rounding circuitry)的框图;

10.图6是根据本公开的实施例的可以在图3或图4的浮点加法器中实现的具有单位移位器的加法和舍入电路的框图;

11.图7是根据本公开的实施例的对输入值进行加法和舍入的复合加法器的框图;

12.图8是根据本公开实施例的高效地实现加法和舍入的加法器和舍入电路的框图;

13.图9是根据本公开的实施例的双路径加法器的框图,该双路径加法器使双路径汇合以针对两条路径使用相同的加法器/减法器,而不包括用于任一路径的专用加法器或减法器;

14.图10是根据本公开的实施例的图9的双路径加法器的框图,其中用组合电路代替图9的双路径加法器中的计数前导零电路和归一化移位器;

15.图11是根据本公开的实施例的图10的组合电路的对数结构;以及

16.图12是根据实施例的其中可以实现一个或多个浮点运算符的数据处理系统的图。

具体实施方式

17.下面将描述一个或多个具体实施例。为了提供对这些实施例的简明描述,在说明书中并未描述实际实现方式的所有特征。可以认识到的是,在任何此类实际实现方式的开发中,就像在任何工程或设计项目中一样,必须做出许多特定于实现方式的决策来实现开发者的特定目标,例如,遵守系统相关和业务相关的约束,这些约束可能从一个实现方式到另一实现方式而变化。此外,可以认识到的是,这样的开发工作可能是复杂且耗时的,但是对于受益于本公开的普通技术人员而言,这不过是设计、制造和生产的常规任务。

18.当介绍本公开的各种实施例的元素时,冠词“一(a)”、“一(an)”和“该(the)”旨在表示存在元素中的一个或多个。术语“包括”和“具有”旨在是包含性的并且意味着除了所列元素之外可能还存在附加元素。另外地,应当理解,对本公开的“一些实施例”、“多个实施例”、“一个实施例”或“实施例”的引用并不旨在被解释为排除也并入引述的特征的附加实施例的存在。此外,短语a“基于”b旨在表示a至少部分地基于b。此外,术语“或”旨在包含性的(例如,逻辑or)而不是排除性的(例如,逻辑xor)。换言之,短语a“或”b旨在表示a,b,或a和b两者。

19.如下文进一步详细讨论的,本公开的实施例总体上涉及具有浮点运算符的逻辑电路。随着集成电路(ic)设备内浮点运算符的数量的增加,由浮点运算符消耗的资源可能增加对实现浮点运算符的效率的需求。例如,先前的ic设备可能包括数十到数百个浮点运算符,而即将到来的ic设备设计可能包括数千或数万个浮点运算符。用于改进这种效率的一种机制可以包括使用用于合成电路的设计工具,该电路可以包括多个(例如,10,000个)个浮点算术逻辑单元(alu),这些alu包括远路径和近路径,该远路径用于对其进行运算的数字的指数相距很远的情况,该近路径用于数字的指数彼此接近的情况。alu可以使用应用于远路径加法器的舍入方法,该方法将加法器/减法器与舍入操作分开。远路径加法器/减法器也可以用作近路径减法器,从而实现两条路径之间的电路的重用。此外,近路径可包括合成电路,该合成电路将计数前导零函数与移位(例如,向左移位)组合以创建更简单、更快且更小的电路。

20.考虑到上述情况,图1示出了可以实现高效的尾数舍入技术的系统10的框图。设计者可能期望在集成电路设备12(ic,例如,现场可编程门阵列(fpga))上实现涉及浮点数运算的功能。设计者可以指定要实现的高级程序(例如,opencl程序),这可以使设计者能够更高效且更容易地提供编程指令来配置集成电路设备12的可编程逻辑单元的集合,而不要求低级硬件描述语言(例如,verilog或vhdl)的特定知识。例如,因为opencl与其他高级编程语言(例如,c++)非常相似,所以熟悉这种编程语言的可编程逻辑的设计者可能比要求学习不熟悉的低级硬件描述语言来实现ic中的新功能的设计者具有减少的学习曲线。

21.设计者可以使用设计软件14(例如,intel公司的的版本)来实现他们的高级设计。设计软件14可以使用编译器16将高级程序转换为低级描述。设计软件14还可以用于优化和/或提高设计效率。编译器16可以向主机18和集成电路设备12提供代表高级程序的机器可读指令。主机18可以接收可以由内核程序20实现的主机程序22。为了实现主机程序22,主机18可以经由通信链路24将来自主机程序22的指令传送到集成电路设备12,该通信链路24可以是例如直接存储器访问(dma)通信或快速外围组件互连(pcie)通信。在一些实施例中,内核程序20和主机18可以启用集成电路设备12上的浮点算术电路26

的配置。浮点算术电路26可以包括电路和/或其他逻辑元件,并且可以被配置为例如在被配置为执行浮点乘法、浮点加法、舍入等的硬化电路中实现浮点算术逻辑。

22.现在转向集成电路设备12的更详细的讨论,图2示出了可以是可编程逻辑器件(例如,现场可编程门阵列(fpga))的集成电路设备12。此外,应当理解,集成电路设备12可以是任何其他合适类型的集成电路设备(例如,专用集成电路和/或专用标准产品)。如所示的,集成电路设备12可以具有输入/输出电路42,该输入/输出电路42用于驱动信号关闭设备并用于经由输入/输出引脚44从其他设备接收信号。互连资源46(例如,全局和局部垂直和水平导线和总线)可以用于在集成电路设备12上路由信号。另外地,互连资源46可以包括固定互连(导线)和可编程互连(即,在相应的固定互连之间的可编程连接)。可编程逻辑48可以包括组合逻辑电路和顺序逻辑电路。例如,可编程逻辑48可以包括查找表、寄存器和复用器。在各种实施例中,可编程逻辑48可以被配置为执行定制的逻辑功能。与互连资源相关联的可编程互连可以被认为是可编程逻辑48的一部分。可编程逻辑可以包括不同可编程性层的多种不同类型的可编程逻辑48。例如,可编程逻辑48可以包括各种数学逻辑单元,例如,算术逻辑单元(alu),每个alu被配置为执行各种数学函数(例如,浮点算术计算)。

23.如先前所讨论的,可编程逻辑可以包括相对大量(例如,数百、数千、数万等)的alu,例如,浮点alu(fp alu)。fp alu可以使用具有不同效率水平的不同技术来实现。通过使用本文公开的合成方法,fp加法器可以在物理上更小的空间中以更低的时延实现。具体地,本文公开的fp加法器可以利用分开的近路径和远路径,这些路径分开然后汇合以共享一些电路,然后再次分开。另外地或可替代地,可以使用合成方法来清除前导零并将其移位到组合的移位前导零电路。

24.考虑到这种情况,图3是fp加法器100的实施例的简化框图。fp加法器100接收两个或更多个浮点数并且组合浮点数(例如,进行加法或减法)以获得结果。每个浮点数包括符号、指数和尾数。例如,在fp32数字中,fp32数包括单个符号位、八位指数和二十三位尾数。在fp加法器100中,在fp加法器100中接收浮点数的这些单独的分量。例如,fp加法器100在复用器106和108处接收尾数102和104。

25.基于在比较器114中在指数110与指数112之间的比较的结果来控制复用器106和108。由于两个浮点数被接收为具有前导1的经归一化的浮点数,因此数字中的一个(例如,较小的数字)可以被非归一化以将两个浮点数与相同的指数对齐。因此,比较器114选择具有较高指数的数字并将对应的控制信号116发送到复用器118。比较器114还将控制信号120和122发送到复用器106和108。使用这些控制信号120和122,复用器106和108使fp加法器100能够确保从复用器108发送对应于较小数字(例如,较小指数)的尾数124并且从复用器106发送对应于较大数字的尾数126。因此,可以选择较大数字的指数作为基指数。由于较小的数字可能需要与较大数字的指数对齐,因此尾数124可以在移位器128中向右移位与相应的指数的差异相对应的位置数。移位的尾数130从移位器128输出。移位的尾数130和尾数126被发送到加法器/减法器132,该加法器/减法器132可以基于输入的浮点数的符号和针对fp加法器100的选定的运算(例如,加法或减法)来对值进行加法或减法。在进行加法或减法之后,可以对结果134进行非归一化。因此,计数前导零电路(clz)136可以用于对第一个1之前的零的数量进行计数以输出控制138,该控制138指示结果134将被移位多远从而以隐含的前导1格式(例如,ieee754 fp)进行归一化。在这样的移位中,fp加法器100使用加法

器/减法器142从基指数140(例如,较大数字的指数)进行加法或减法以生成输出指数144。在加法器/减法器142中加或减的数字也指示移位器146要向结果134应用多少移位以生成经归一化的结果148。

26.如先前所指出的,图3示出了fp加法器100的实施例的简化框图。实际上,fp加法器100中可以包括附加电路,为了简洁起见可以从图3中省略该附加电路。例如,fp加法器100可以利用对输入和/或输出的异常处理。fp加法器100还可以利用内部函数,例如,对加法器/减法器132中的和或差的舍入。舍入可能很复杂并且可能显著影响fp加法器100的实际实现方式。

27.fp加法器100可以使用双路径实现方式来实现,该双路径实现方式可以使fp加法器100更快且更高效地执行。具体地,fp加法器100的关键路径可以包括移位器128、加法器/减法器132、clz 136和移位器146。移位器128可以具有与加法器/减法器132以及clz 136和移位器146的组合大致相同的大小和速度。

28.在浮点加法/减法中,存在两种常见情况:近情况和远情况。在近情况下,两个输入数字几乎相同,因为指数110和112彼此相等或相差的数字等于或低于阈值(例如,1)。因此,移位器128可以在一个方向上(例如,向右)移位最大阈值数字(例如,1)的位。如果对这些接近的数字进行减法,则结果将可能非常小,这意味着可能使用大的移位。例如,如果从1.5中减去1.4999,则0.0001的结果需要进行向右的多次移位以进行归一化。

29.在远情况下,指数110和112相差超过阈值数字。例如,指数110和112可以相差二或更多。这里,移位器128中的向右移位可能较大,但是使用归一化中的较少移位,减法的结果接近经归一化的范围。例如,归一化移位(例如,向左移位)可以限制为一位或更少。

30.在远情况和近情况这两种情况下,加法将导致最大1位向右移位以进行归一化。使用这些特性,fp加法器可以被拆分为用于近情况减法的近路径和用于远情况加法和减法的远路径。远路径也可以用于服务近情况加法,因为近情况加法和远情况加法两者都利用小型后加法移位器。

31.图4示出了包括远路径164和近路径166的fp加法器160的实施例的简化框图。远路径164和近路径166两者都接收尾数124、126并生成相应的输出,这些输出被发送到输出复用器167,该输出复用器167被配置为在近路径输出与远路径输出之间进行选择,以作为fp加法器160的输出。如所示的,如先前关于图3的fp加法器100所讨论的那样生成尾数124、126。类似地,除了移位器128和加法器/减法器132在fp加法器160的远路径164中之外,移位器128和加法器/减法器132两者如先前关于图3的fp加法器100所讨论的那样起作用。然而,来自加法器/减法器132的结果134被发送到单位移位器168,该单位移位器168向右或向左移位以生成远路径输出170,该远路径输出170被发送到输出复用器167。单位移位器168中移位的大小(例如,0或1)和方向被发送到加法器/减法器172以根据基指数140生成远指数174。当输出复用器167选择远路径输出170时,使用远指数和远路径输出17以形成浮点输出。

32.近路径166在移位器176处接收尾数124,该移位器176将尾数124移位阈值数字(例如,1位)或更少,以将尾数124与较大的数字对齐作为移位后的尾数177。在减法器178中从尾数126减去移位后的尾数177以生成输出180。输出180被发送到clz 136和移位器146以生成经归一化的结果148和输出指数144。clz 136和移位器146如关于图3的fp加法器100所描

述的那样起作用。输出复用器167选择经归一化的结果148和输出指数144以用于近情况减法。

33.与fp加法器100相比,近路径166和远路径164两者将利用fp加法器160中的附加的移位器(例如,单位移位器168和移位器176)。然而,与全精度移位器(例如,移位器128和146)相比,这些移位器可以具有小的面积和时延。因此,关键路径简化为大的移位器(例如,移位器128和146)、加法器和较小的移位器。在近路径166中,加法器仅用作不利用舍入的减法器178。因此,减法器178在远路径164中小于加法器/减法器132。虽然fp加法器160的各个组件的大小可能大于fp加法器100,但在现实世界中,在要达到时序收敛(timing closure)的情况下,fp加法器160可以更小,因为可以很容易地合成两个单独的路径以加快速度。

34.如先前所指出的,由于减法的性质,减法器178可能不利用舍入。然而,远路径164中的加法器/减法器132可以利用舍入来适应加法之后的舍入。图5是加法和舍入电路200的简化框图。加法和舍入电路200包括加法器/减法器132,该加法器/减法器132接收尾数126和移位后的尾数130以生成结果134。加法和舍入电路200还包括处理电路202,该处理电路202接收一个或多个输入203以计算/生成控制如何舍入结果134的舍入值204。可以从移位器128、单位移位器168和/或集成电路设备12中的其他位置接收输入203,从而选择是否舍入以及在哪里应用舍入。舍入值204在加法器206中与结果134相加,该加法器206生成经舍入的结果208,该经舍入的结果208被发送到单位移位器168作为结果134。

35.在实际实现方式中,将多个进位传播加法器(例如,加法器/减法器132和加法器206)链接在一起在面积和时延方面可能是昂贵的。如图6中示出的,在加法和舍入电路210中,该成本可能由于在加法器/减法器132与加法器206之间的移位器212中被实现为向左移位或向右移位的舍入点(round point)而进一步复杂化。可以将该加法和舍入电路210组合到单个复合加法器中,该单个复合加法器将加法器/减法器132、移位器212中的舍入点选择、处理电路202中的舍入值计算和加法器206组合到单个级别的逻辑中。

36.图7是复合加法器218的实施例的简化框图。在复合加法器218中,输入操作数(例如,具有尾数126和130的位)被发送到相应的xor门220以计算中间信号222。输入操作数也被发送到相应的and门224以计算相应的生成信号226。输入操作数也被发送到相应的or门228以计算传播信号230。生成信号226和传播信号230被发送到并行前缀电路232,该并行前缀电路232使用生成信号226和传播信号230来计算相应的进位信号236。可以使用舍入电路节点234来执行对进位信号的计算。在一些实施例中,并行前缀电路232的前缀树可以包括诸如brent-kung网络或kogge-stone网络之类的拓扑。在一些实施例中,附加层可以跟随前缀网络以实现称为标记的前缀加法器的结构。换言之,舍入电路节点234向并行前缀电路232的多个层添加一定数量的层以产生计算出的进位信号237。计算出的进位信号237和相应的中间信号222被发送到相应的xor门238以生成输出信号240。

37.在复杂的网络中,前述电路的组合可以解决问题。如下面所讨论的,近路径166和远路径164的重叠部分可以组合以简化这种网络,以获得增加的效率和/或更低的时延。

38.图8示出了用于在加法和舍入电路250中植入舍入功能的替代实施例。加法和舍入电路250包括加法器/减法器132、处理电路202、并行前缀电路232和xor门238。然而,与对并行前缀电路232的输出进行移位相反,复用器252可以用于对舍入位(例如,舍入值204)与高于并行前缀电路232的一个或多个最低有效位的结果134进行复用,该并行前缀电路232使

用一个或多个or门254将传播位强制为高,这些or门254对结果134与舍入值204进行or运算。被强制为高的传播位对应于从结果134中舍入的位。

39.加法和舍入电路250相对便宜,因为舍入仅针对并行前缀电路232的特定数量(例如,3个)最低有效位执行。如果位从并行前缀电路232中传播出去,则已经发生了来自该舍入的溢出256,并且基指数被调整1。因此,如果需要,在不损失性能或增加面积的情况下,移位器212可以位于xor门238之后。关于复用器和使用并行前缀电路232的基于or门的舍入的附加细节可以在于2020年12月24日提交的、题为“rounding circuitry for floating-point mantissas”的美国专利申请第17/133,861号中找到,该美国专利申请以其整体出于所有目的并入。

40.如先前所指出的,移位器212中的舍入移位可以在加法和舍入电路250中的加法结束时和/或在加法之后在远路径164中执行。这允许构建图9中示出的fp加法器270,其中远路径272和近路径274具有分开的部分但是以单个2:1复用器276为代价共享加法器/减法器132。因为可以在其中远路径272与近路径274分开且与加法器/减法器132分开的情况下在一部分中实现舍入电路277,所以加法器/减法器132可以在远路径272与近路径274之间共享,因为可以在不使用全部复合加法器218的情况下直接访问简单的加法器功能。加法器/减法器132与舍入电路277的这种分开可以在不增加复合加法器218的面积或时延的情况下实现。唯一的增加包括单个2:1复用器276。然而,由于单个2:1复用器276导致的增加仍然可以通过省略在近路径166中使用的单独减法器178来节省面积。

41.fp加法器270使用与fp加法器100和160相关使用的相同技术得出尾数126和尾数124。当接收到两个近情况浮点数时,在近路径272中,对应于较小的数字的尾数124可以在移位器278中移位。移位器278将尾数124移位阈值数字(例如,1位)或更少,以使尾数124归一化为较大的数字作为移位的尾数280。例如,当近情况包括对应于相同指数的尾数124和126时,移位的尾数280可以不从尾数124移位。移位的尾数280连同用于远路径274的移位的尾数130一起被发送到单个2:1复用器276。单个2:1复用器276在移位的尾数130与移位的尾数280之间进行选择,以作为选定的尾数282。无论传入数据是近情况还是远情况,选定的尾数282都在加法器/减法器132中与尾数126进行加法或从尾数126进行减法。

42.在近情况下,来自加法器/减法器132的结果284被发送到clz 136,并且近路径274包括对结果284的处理,以与fp加法器100如何根据结果134生成经归一化的结果148类似地生成经归一化的结果148。可以认识到的是,clz 136和移位器146可以是学究式的实现方式。现实世界的实现方式可能具有复杂得多的设计,以通过分解该计算来优化延迟。例如,clz 136可以由两部分组成:前导零预期器(其基于对加法器/减法器132的两个输入来对移位进行相当准确的猜测),然后是微调,其中对clz 136进行微调。这使得clz 136的复杂计算部分能够与加法器并行运行,同时微调比clz 136的其他部分小得多(并且更快)。

43.在利用舍入的远情况下,结果284被发送到舍入电路277以进行舍入和/或归一化以生成远路径输出170。如果不利用舍入,则远路径输出170与在舍入电路277中进行或没有进行归一化的情况下的结果284都相同。

44.如所示的,使用移位器146针对近路径274的归一化移位比针对移位器128中的远路径272的非归一化移位更复杂。这是真的,因为clz 136用于确定归一化移位量。可以在fp加法器270中使用任何合适的clz 136实现方式。然而,在一些实施例中,clz 136和移位器

146可以被组合到单个逻辑单元中。例如,图10示出了与fp加法器260相同的fp加法器300,除了可以使用组合电路302来代替clz 136和移位器146以生成经归一化的结果148之外。与单独使用单独的clz 136和移位器146相反,可以通过整体检查两个电路的结果来确定经归一化的结果148。例如,clz 136和移位器146的操作可以被描述为if-then-else链。如果clz 136确定第一位具有1,则不会发生移位,并且不在随后的位位置处进行移位确定。如果clz 136确定第二位具有在第一位中的0之后的1,则将发生单个向左移位,并且不在随后的位位置处进行移位确定。if-then-else链可以类似地继续通过这些位,直到找到前导1为止。针对具有23位尾数的fp32数字使用这样的语句,条件可以描述为:

45.near(23)=!near(23)and near(22)=!near(23)and!near(22)and near(21)=!near(23)and!near(22)and!near(21)and!near(20)and!near(19)and!near(18)and near(17)

ꢀꢀ

(等式1)

46.其中,near(i)指示要移位多少和要执行多少移位,and是布尔and,并且!near(i)指示near(i)的补码。使用等式1,可以递归地提取出每个条件。例如,递归条件可以包括:

47.f_a=!near(23)and!near(22)and!near(21)and!near(20)and!near(19)

48.ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(等式2)

49.near(17)=f_a and near(18)

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(等式3)

50.near(16)=f_a and!near(18)and near(17)

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

(等式4)

51.near(15)=f_a and!near(18)and!near(17)and near(16)

ꢀꢀꢀꢀꢀꢀꢀꢀ

(等式5)

52.使用这些函数,可以以相同的幅度处理移位中的每个级别,其中输出中的每一位可能具有不同的复杂度。可以使用or门和/或and门来实现这样的等式。然而,这些结构可以通过使用电子设计辅助工具的逻辑重构来转换为更快的对数结构,以在组合电路302内形成电路。逻辑重构的结果可以包括:

[0053][0054]

图11是合并clz和归一化移位的结构310的实施例,该结构310可以在逻辑重构之后针对fp32加法器中的位21在组合电路302中实现。如所示的,结构310接收输入位312并且在所示的级别314、316、318、320、322和324中组合输入位312以生成包括clz和归一化移位的输出326。结构的描述可能会手动递归,这可能会在合成期间给出不同的结果,尤其是作为大型系统的一部分时。此外,虽然上述内容指代具有23位尾数的fp32,但类似的技术可以应用于具有不同大小的尾数的其他浮点格式。因此,使用该组合电路302可以减小clz 136和移位器146的大小,并且与具有单独的clz 136和移位器136的实现方式相比提高了效率。

[0055]

此外,尽管fp加法器300的所示实施例包括具有共享的加法器/减法器132和组合电路302的双路径技术,但浮点运算符的一些实施例可以部署本文使用的双路径技术,而其他实施例可以在没有双路径技术的情况下部署组合电路302。

[0056]

集成电路设备12可以是数据处理系统(例如,图12中示出的数据处理系统350)或

可以是数据处理系统的组件。数据处理系统350可以包括主机处理器352、存储器和/或存储电路354以及网络接口356。数据处理系统350可以包括更多或更少的组件(例如,电子显示器、用户接口结构或asic)。主机处理器352可以包括任何合适的处理器,例如,处理器或精简指令处理器(例如,精简指令集计算机(risc)、高级risc机器(arm)处理器),其可以管理针对数据处理系统350的数据处理请求(例如,以执行机器学习、视频处理、语音识别、图像识别、数据压缩、数据库搜索排名、生物信息学、网络安全模式识别、空间导航等)。存储器和/或存储电路354可以包括随机存取存储器(ram)、只读存储器(rom)、一个或多个硬盘驱动器、闪速存储器等。存储器和/或存储电路354可以保存要由数据处理系统350处理的数据。在一些情况下,存储器和/或存储电路354还可以存储用于对集成电路设备12进行编程的配置程序(位流)。网络接口356可以允许数据处理系统350与其他电子设备通信。数据处理系统350可以包括若干不同的封装,或者可以被包含在单个封装衬底上的单个封装内。

[0057]

在一个示例中,数据处理系统350可以是处理各种不同请求的数据中心的一部分。例如,数据处理系统350可以经由网络接口356接收数据处理请求以执行机器学习、视频处理、语音识别、图像识别、数据压缩、数据库搜索排名、生物信息学、网络安全模式识别、空间导航或某种其他专门任务。主机处理器352可以使得集成电路设备12的可编程逻辑结构能够利用适合于实现所请求的任务的乘法器编程。例如,主机处理器352可以指示存储在存储器和/或存储电路354上的配置数据(位流)被编程到集成电路设备12的可编程逻辑结构中。配置数据(位流)可以表示用于一组一个或多个浮点乘法器的电路设计,这些乘法器可以根据本文所描述的技术映射到可编程逻辑并一起打包在其中。

[0058]

本文呈现和要求保护的技术被引用并应用于实体对象和具有实际性质的具体示例,它们明确地改进了当前技术领域,并因此不是抽象的、无形的或纯理论的。此外,如果附加到本说明书末尾的任何权利要求包含被指定为“用于[执行][功能]

……

的单元”或“用于[执行][功能]

……

的步骤”一个或多个元素,则旨在根据35u.s.c.112(f)来解释这种元素。然而,对于包含以任何其他方式指定的元素的任何权利要求,旨在不根据35u.s.c.112(f)解释这种元素。

[0059]

虽然本公开中阐述的实施例可能易于受到各种修改和替代形式的影响,但已经通过示例的方式在附图中示出并且已经在本文中详细描述了具体实施例。然而,应当理解,本公开并不旨在限于所公开的特定形式。本公开将涵盖落入由以下所附示例实施例限定的本公开的精神和范围内的所有修改、等效物和替代方案。

[0060]

本公开的示例实施例

[0061]

以下编号的条款定义了本公开的某些示例实施例。

[0062]

示例实施例1、一种系统,包括:

[0063]

浮点算术电路,该浮点算术电路接收两个浮点数,其中,该浮点算术电路包括:

[0064]

第一路径,该第一路径至少部分地基于两个浮点数之间的大小的差来对两个浮点数执行第一运算;以及

[0065]

第二路径,该第二路径至少部分地基于两个浮点数之间的大小的差来对两个浮点数执行第二运算,其中,第一路径和第二路径彼此分开,然后在用于第一运算和第二运算的共享加法器上汇合,之后第一路径和第二路径再次分开。

[0066]

示例实施例2、示例实施例1的系统,包括:比较器,该比较器确定两个浮点数的指数之间的指数差,其中,当差小于阈值时,第一路径对两个浮点数执行第二运算。

[0067]

示例实施例3、示例实施例2的系统,其中,当差大于或等于阈值时,第一运算包括减法。

[0068]

示例实施例4、示例实施例2的系统,其中,当差大于或等于阈值时,第一运算包括加法。

[0069]

示例实施例5、示例实施例2的系统,其中,当差小于阈值时,第一运算包括加法。

[0070]

示例实施例6、示例实施例2的系统,其中,当差小于阈值时,第二运算包括减法。

[0071]

示例实施例7、示例实施例2的系统,其中,阈值包括2。

[0072]

示例实施例8、示例实施例1的系统,包括:复用器,该复用器在从第一路径向共享加法器发送第一移位的尾数与从第二路径向共享加法器发送第二移位的尾数之间进行选择。

[0073]

示例实施例9、示例实施例8的系统,其中,第一路径包括多位移位器,该多位移位器生成第一移位的尾数。

[0074]

示例实施例10、示例实施例8的系统,其中,第二路径包括单位移位器,该单位移位器生成第二移位的尾数。

[0075]

示例实施例11、示例实施例1的系统,其中,第二路径包括:

[0076]

计数前导零电路,该计数前导零电路从共享加法器接收结果,并且对结果中的前导零的数量进行计数;以及

[0077]

归一化移位器,该归一化移位器至少部分地基于前导零的数量来对结果进行移位以生成经归一化的输出。

[0078]

示例实施例12、示例实施例1的系统,其中,第二路径包括组合电路,该组合电路执行移位检测,并且通过对来自共享加法器的结果中的输入位进行组合来应用移位,应用移位是使用根据对数结构对输入位进行组合的多个级别的。

[0079]

示例实施例13、示例实施例1的系统,其中,第一路径包括舍入和加法电路,该舍入和加法电路从共享加法器接收结果,并且对结果进行舍入。

[0080]

示例实施例14、示例实施例13的系统,其中,舍入和加法电路包括:

[0081]

并行前缀电路,该并行前缀电路接收结果;

[0082]

复用器,该复用器控制并行前缀电路在舍入位处的舍入;

[0083]

or门,该or门基于舍入位的位置来将并行前缀电路的传播位驱动为高;以及

[0084]

输出复用器,该输出复用器将并行前缀电路的输出向左或向右移位一个位。

[0085]

示例实施例15、一种方法,包括:

[0086]

接收第一浮点数;

[0087]

接收第二浮点数;

[0088]

将第一浮点数的第一尾数拆分到第一路径和第二路径中;

[0089]

在第一路径中的第一移位器中移位第一尾数以生成第一移位的尾数;

[0090]

在第二路径中的第二移位器中移位第一尾数以生成第二移位的尾数,其中,第一移位器大于第二移位器;

[0091]

从第一移位的尾数和第二移位的尾数中选择选定的尾数;

[0092]

在加法器/减法器中将选定的尾数与第二浮点数的第二尾数相加或从第二浮点数的第二尾数中减去选定的尾数;

[0093]

将来自加法器/减法器的结果发送到第三路径和第四路径;以及

[0094]

在第三路径与第四路径之间选择输出。

[0095]

示例实施例16、示例实施例15的方法,其中,第一浮点数具有比第二浮点数的指数小的指数。

[0096]

示例实施例17、示例实施例15的方法,包括:确定要移位多远以进行归一化,并且对第三路径中的结果进行归一化。

[0097]

示例实施例18、示例实施例15的方法,包括:在第四路径中的舍入电路中对结果进行舍入,其中,舍入电路包括单位移位器,该单位移位器被配置为在对结果进行舍入之后对结果进行归一化。

[0098]

示例实施例19、一种系统,包括:

[0099]

第一输入端,该第一输入端被配置为接收第一浮点数的第一尾数;

[0100]

第二输入端,该第二输入端被配置为接收第二浮点数的第二尾数;

[0101]

第一路径,该第一路径具有第一移位器,该第一移位器被配置为对第一尾数进行移位以作为第一移位的尾数;

[0102]

第二路径,该第二路径具有第二移位器,该第二移位器被配置为对第一尾数进行移位以作为第二移位的尾数,其中,第二移位器小于第一移位器,并且第二移位器包括单位移位器;

[0103]

复用器,该复用器被配置为在第一移位的尾数与第二移位的尾数之间进行选择,并且输出选定的尾数;

[0104]

加法器/减法器,该加法器/减法器被配置为从加法器/减法器接收选定的尾数;

[0105]

第三路径,该第三路径被配置为基于结果中的位值来确定要将来自加法器/减法器的结果移位多远,并且执行移位;

[0106]

第四路径,该第四路径被配置为对来自加法器/减法器的结果进行舍入;以及

[0107]

输出复用器,该输出复用器被配置为从第三路径中的结果和第四路径中的结果中选择用于系统的输出。

[0108]

示例实施例20、示例实施例19的系统,其中,第三路径包括组合电路,该组合电路被配置为使用逻辑树结构来执行移位和确定,该逻辑树结构被配置为以多个级别对结果中的输入进行组合以生成输出位。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1