芯片上电控制方法、控制装置及存储介质与流程

1.本技术涉及芯片控制领域,尤其是涉及一种芯片上电控制方法、控制装置及存储介质。

背景技术:

2.相关技术中,部分存储芯片不是直接焊接在电路板上,而是通过底座固定。在需要更换芯片时,只需要手动打开底座更换芯片即可。但由于是人工更换,有时会出现芯片放置方向错误的情况。而根据芯片引脚定义可知,芯片放置方向错误可能导致电路短路,引起安全问题。

技术实现要素:

3.本技术旨在至少解决现有技术中存在的技术问题之一。为此,本技术提出一种芯片上电控制方法,能够及时检测到芯片放置方向的异常,提高芯片上电时的安全性。

4.本技术还提出一种运用上述芯片上电控制方法的芯片上电控制装置和一种计算机可读存储介质。

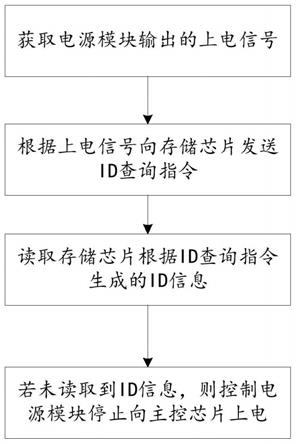

5.根据本技术的第一方面实施例的芯片上电控制方法,包括:获取电源模块输出的上电信号;根据所述上电信号向存储芯片发送id查询指令;读取所述存储芯片根据所述id查询指令生成的id信息;若未读取到所述id信息,则控制所述电源模块停止向主控芯片上电。

6.根据本技术实施例的芯片上电控制方法,至少具有如下有益效果:接通电源时,通过读取存储芯片id的方式检测存储芯片放置是否正常,若存储芯片的放置位置不正常,则无法读取到存储芯片的id信息,此时停止向主控芯片上电,避免因芯片放置错误引起的电路安全问题,减少元器件的损失。

7.根据本技术的一些实施例,所述读取所述存储芯片根据所述id查询指令生成的id信息的步骤之后,还包括:若读取到所述id信息,则控制所述电源模块开始向所述主控芯片上电。

8.根据本技术的一些实施例,所述若未读取到所述id信息,则控制所述电源模块停止向主控芯片上电的步骤,还包括:若未读取到所述id信息,则输出报警信号。

9.根据本技术的第二方面实施例的芯片上电控制装置,包括:上电控制单元,所述上电控制单元用于获取电源模块输出的上电信号;id检测单元,所述id检测单元用于根据所述上电信号向存储芯片发送id查询指令,并读取所述存储芯片根据所述id查询指令生成的id信息;所述上电控制单元还用于在所述id检测单元未读取到所述id信息的情况下,停止向主控芯片上电。

10.根据本技术的一些实施例,所述上电控制单元还用于在所述id检测单元读取到所述id信息的情况下,控制所述电源模块开始向所述主控芯片上电。

11.根据本技术的一些实施例,还包括报警单元,所述报警单元用于在所述id检测单

元未读取到所述id信息的情况下,输出报警信号。

12.根据本技术的一些实施例,所述报警信号包括:指示灯信号、声效信号、合成语音信号、图像信号中的至少一种。

13.根据本技术的一些实施例,还包括传输单元,所述传输单元用于在所述主控芯片上电后,传输所述主控芯片和所述存储芯片之间的通信信号。

14.根据本技术的一些实施例,所述传输单元传输所述通信信号的方式包括spi通信或qspi通信。

15.根据本技术的第三方面实施例的计算机可读存储介质,所述计算机可读存储介质存储有计算机可执行指令,所述计算机可执行指令用于使计算机执行上述第一方面实施例的芯片上电控制方法。

16.本技术的附加方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本技术的实践了解到。

附图说明

17.下面结合附图和实施例对本技术做进一步的说明,其中:

18.图1为本技术芯片上电控制方法的一种实施例的流程图;

19.图2为本技术芯片上电控制方法的另一种实施例的流程图;

20.图3为本技术芯片上电控制装置的一种实施例的模块图。

21.附图标记:

22.电源模块100、检测控制模块200、上电控制单元201、id检测单元202;

23.报警单元203、传输单元204、主控芯片300、存储芯片400。

具体实施方式

24.下面详细描述本技术的实施例,所述实施例的示例在附图中示出,其中自始至终相同或类似的标号表示相同或类似的元件或具有相同或类似功能的元件。下面通过参考附图描述的实施例是示例性的,仅用于解释本技术,而不能理解为对本技术的限制。

25.本技术的描述中,除非另有明确的限定,设置、安装、连接等词语应做广义理解,所属技术领域技术人员可以结合技术方案的具体内容合理确定上述词语在本技术中的具体含义。

26.一些实施例,参照图1,芯片上电控制方法包括:获取电源模块输出的上电信号;根据上电信号向存储芯片发送id查询指令;读取存储芯片根据id查询指令生成的id信息;若未读取到id信息,则控制电源模块停止向主控芯片上电。

27.示例,本技术的芯片上电控制方法应用于主板上时,当电源模块开始工作,主板接通电源时,即可以获取到电源模块输出的上电信号,主板在获取到电源模块的上电信号后,会进行上电进程。先不给cpu(主控芯片)上电,而是向存储芯片发送id查询指令,以读取存储芯片的id信息。可以理解的是,在获取到上电信号后,会向存储芯片正常上电。若读取存储芯片的id信息失败,则说明存储芯片的放置方向错误,此时存储芯片无法正常工作并根据id查询指令输出自身的id信息。此时停止后续的对cpu的上电进程,避免cpu上电后与存储芯片通信时,由于存储芯片对应引脚的错误导致的电路安全问题,降低存储芯片及cpu损

坏的可能性。

28.本实施例的芯片上电控制方法至少具有如下有益效果:接通电源时,通过读取存储芯片id的方式检测存储芯片放置是否正常,若存储芯片的放置位置不正常,则无法读取到存储芯片的id信息,此时停止向主控芯片上电,避免因芯片放置错误引起的电路安全问题,减少元器件的损失。

29.一些实施例,参照图2,读取存储芯片根据id查询指令生成的id信息的步骤之后,还包括:若读取到id信息,则控制电源模块开始向主控芯片上电。如果读取存储芯片的id信息成功,则说明存储芯片放置正确,存储芯片可以正常工作,此时控制电源模块开始向主控芯片上电,电路开始进入正常工作状态。

30.一些实施例,参照图2,若未读取到id信息,则控制电源模块停止向主控芯片上电的步骤还包括:若未读取到id信息,则输出报警信号。如果读取id信息失败,则说明存储芯片放置错误,在停止电源模块继续上电的同时,输出报警信号提示操作人员重新放置芯片。

31.一些实施例,参照图3,芯片上电控制装置包括:电源模块100、检测控制模块200、主控芯片300和存储芯片400,检测控制模块200包括上电控制单元201和id检测单元202,上电控制单元201用于获取电源模块100输出的上电信号;id检测单元202用于根据上电信号向存储芯片400发送id查询指令,并读取存储芯片400根据id查询指令生成的id信息;上电控制单元201还用于在id检测单元202未读取到id信息的情况下,停止向主控芯片300上电。

32.本实施例的芯片上电控制装置,至少具有如下有益效果:接通电源时,通过读取存储芯片id的方式检测芯片放置是否正常,若异常则停止上电,避免芯片放置错误引起的电路安全问题,减少元器件的损失。

33.一些实施例,上电控制单元201还用于在id检测单元202读取到id信息的情况下,控制电源模块100开始向主控芯片300上电。如果读取id信息成功,则说明存储芯片放置正确,电源模块100开始给主控芯片300上电,电路开始进入正常工作状态。

34.一些实施例,参照图3,检测控制模块200还包括报警单元203,报警单元203用于在id检测单元202未读取到id信息的情况下,输出报警信号。如果读取id信息失败,则说明存储芯片放置错误,检测控制模块200在停止电源模块100继续供电的同时,输出报警信号提示操作人员重新放置芯片。

35.一些实施例,报警信号包括:指示灯信号、声效信号、合成语音信号、图像信号中的至少一种。报警信号被发送至报警装置后,报警装置将发出报警提示。报警信号的类型取决于采用的报警装置的类型。例如,报警装置为led灯时,报警单元203输出的报警信号即为指示灯信号,led灯根据指示灯信号点亮或闪烁以向操作人员发出报警。

36.一些实施例,参照图3,检测控制模块200还包括传输单元204,传输单元204用于在主控芯片300上电后,传输主控芯片300和存储芯片400之间的通信信号。在另一些实施例中,主控芯片300和存储芯片400之间的通信通道可单独设置。

37.一些实施例,传输单元204传输通信信号的方式包括spi(serial peripheral interface,串行外设接口)通信或qspi(quad spi,队列串行外设接口)通信。在另一些实施例中,传输单元204传输通信信号的方式也包括iic(inter-integrated circuit,集成电路总线)通信。

38.下面以一个具体实施例,详细描述本技术的芯片上电控制装置,在部分服务器主

板方案中,存储bios(basic input output system,基本输入输出系统)的flash芯片不是直接焊接在主板上,而是通过底座固定。在服务器主板中,可使用cpld(complex programmable logic device,复杂可编程逻辑器件)作为检测控制模块200。在本实施例中,主板电源即为电源模块100,cpu即为主控芯片300,flash芯片即为存储芯片400,报警装置为led灯。cpu通过spi协议与flash芯片通信。在连接时,将cpu的spi相关信号线接入cpld,同时也从flash芯片将spi相关信号线接入cpld。主板正常工作的情况下,cpld对spi相关信号不做处理,直接将信号传输出去,cpu与flash芯片正常通信。在主板上电开机时,cpld将执行检测过程,检测过程分为三个阶段:

39.第一阶段,主板只接入电源,但未开机,此时只有cpld处于工作状态。

40.第二阶段,主板开机后,cpld接管电源进行上电控制并给flash芯片上电。在这个阶段,cpld先不进行cpu上电等后续上电操作,而是暂时接管spi信号线,对flash芯片进行读取芯片id的操作。如果读取芯片id成功,则进入第三阶段。如果读取芯片id失败,则停止上电操作,返回第一阶段并向外部报警装置发送报警信号。

41.第三阶段,cpld按照正常时序上电,直到主板正常工作。

42.其中,用户可根据需要自定义设置cpld尝试读取flash芯片id的次数。

43.一些实施例,计算机可读存储介质存储有计算机可执行指令,用于使计算机执行上述实施例的芯片上电控制方法。

44.本技术的描述中,参考术语“一些实施例”、“示例”或“具体实施例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本技术的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不一定指的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任何的一个或多个实施例或示例中以合适的方式结合。

45.上面结合附图对本技术实施例作了详细说明,但是本技术不限于上述实施例,在所属技术领域普通技术人员所具备的知识范围内,还可以在不脱离本技术宗旨的前提下作出各种变化。此外,在不冲突的情况下,本技术的实施例及实施例中的特征可以相互组合。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1