一种处理器的制作方法

本发明实施例涉及通信,尤其涉及一种处理器。

背景技术:

1、目前处于统治地位的嵌入式处理器是一种通用性处理器,随着其架构技术的发展成熟,为了兼容通用性以及继承性,其具有较多的冗余设计,甚至具有一些过时的定义。导致目前嵌入式处理器的架构定义内容繁多,架构过于复杂,设计实现复杂度高,且需占用的面积较大。当对嵌入式处理器存在特定需求时,难以做到最优化设计。

2、发明人在对通信系统进行研究时,发现基于通用性处理器进行技术实现时,难以在通信领域进行很好的设计。因此,对现有的基于risc-v指令集的处理器进行剪裁与改进,提供了一种专用处理器,摒弃了繁多的通用性架构,达到简化、面积小且低功耗的目的。

技术实现思路

1、本发明实施例提供了一种处理器,可以摒弃繁多的通用性架构,使处理器的实现简单化、面积小型化,达到低功耗且性能高的效果。

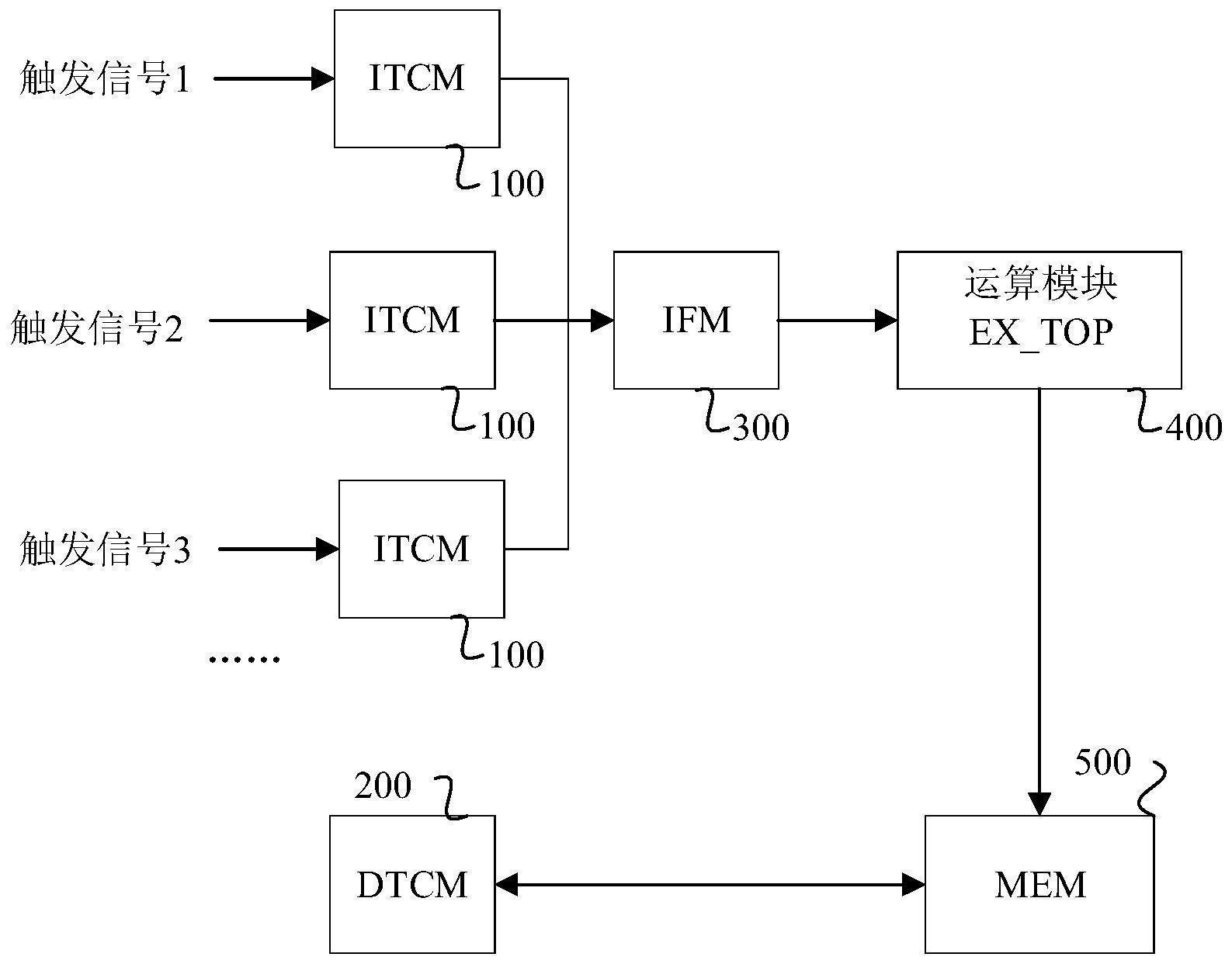

2、本发明实施例提供了一种处理器,应用于通信系统中,该处理器包括:指令缓存itcm、数据缓存dtcm、取指模块ifm、运算模块以及访存模块mem;其中:

3、itcm,用于根据接收的不同触发信号确定匹配的目标指令集,并将所述目标指令集传输至ifm;

4、ifm,用于根据所述目标指令集确定待运算指令,并将所述目标指令集以及待运算指令传输至运算模块,以指示运算模块进行工作;

5、运算模块,用于对所述目标指令集进行译码,确定目标逻辑运算,并根据所述待运算指令指示mem访问存储器获取待运算数据;

6、dtcm,用于根据mem的指示,提供待运算数据;

7、运算模块,还用于将待运算数据按照目标逻辑运算进行运算,得到运算结果。

8、可选的,运算模块包括:译码模块idm、计算单元alu和数据选择器mux;其中:

9、idm,用于对所述目标指令集进行译码,确定目标逻辑运算,并将所述目标逻辑运算以及所述待运算指令传输至alu;

10、alu,用于根据所述待运算指令,确定待运算数据的存储地址,并将所述存储地址传输至mem;

11、mem,用于根据所述存储地址访问存储器,获取dtcm提供的待运算数据;

12、alu,还用于将mem获取的待运算数据按照目标逻辑运算进行运算,得到运算结果;

13、mux,用于获取alu的运算结果和mem读取的待运算数据,进行选择性输出,以驱动数据的业务处理操作。

14、可选的,运算模块,还包括:写回模块wbm;

15、wbm,用于在mux获取运算结果后,根据写回操作指令将所述运算结果写回至ifm;

16、ifm,还用于根据wbm的写回操作,指示itcm根据下一触发信号确定匹配的目标指令集。

17、可选的,wbm,还用于在mux获取运算结果后,不存在写回操作指令时,执行为空的写回操作。

18、可选的,wbm,还用于根据写回操作确定反压信号,并将所述反压信号传输至ifm;

19、ifm,还用于根据所述反压信号确定待运算指令保持不变,以使运算模块在当前处理流程中仅存在一个待运算指令进行执行。

20、可选的,ifm,包括:待运算指令生成单元、简单译码单元、数据触发器、指针寄存器和指令寄存器;其中:

21、数据触发器和指针寄存器相连,用于获取itcm根据触发信号确定的指针初始值,并将所述指针初始值经由指针寄存器传输至所述待运算指令生成单元;

22、简单译码单元,用于接收itcm确定的目标指令集,并确定所述目标指令集的指令类型;

23、所述待运算指令生成单元,用于根据数据触发器和指针寄存器输入的指针初始值生成待运算指令;或者,根据简单译码单元确定的指令类型生成待运算指令;

24、数据触发器,还用于获取所述待运算指令生成单元生成的待运算指令,并经由指针寄存器传输至mem,以获取待运算数据;

25、指令寄存器,用于获取接收itcm确定的目标指令集,以及所述待运算指令生成单元生成的待运算指令,并将目标指令集和待运算指令传输至运算模块。

26、可选的,所述待运算指令生成单元,还用于根据运算模块的运算指令修改请求,生成待运算指令。

27、可选的,简单译码单元,具体用于接收itcm确定的目标指令集,并确定所述目标指令集的指令类型是否为分支跳转指令,以及所述目标指令集的位宽信息。

28、可选的,所述待运算指令生成单元,具体用于当简单译码单元确定指令类型为分支跳转指令时,根据数据触发器和指针寄存器输入的指针初始值生成待运算指令;或者,当简单译码单元确定指令类型不为分支跳转指令时,根据所述目标指令集的位宽信息生成待运算指令。

29、本发明实施例的技术方案,通过设置包含itcm、dtcm、ifm、运算模块以及mem的处理器,其中:itcm,用于根据接收的不同触发信号确定匹配的目标指令集,并将目标指令集传输至ifm;ifm,用于根据目标指令集确定待运算指令,并将目标指令集以及待运算指令传输至运算模块,以指示运算模块进行工作;运算模块,用于对目标指令集进行译码,确定目标逻辑运算,并根据待运算指令指示mem访问存储器获取待运算数据;dtcm,用于根据mem的指示,提供待运算数据;运算模块,还用于将待运算数据按照目标逻辑运算进行运算,得到运算结果,解决了现有技术通用性处理器设计繁琐且架构冗余的问题,实现了摒弃繁多的通用性架构,使处理器结构简单、面积小、低功耗且性能高的效果。

技术特征:

1.一种处理器,应用于通信系统中,其特征在于,所述处理器包括:指令缓存itcm、数据缓存dtcm、取指模块ifm、运算模块以及访存模块mem;其中:

2.根据权利要求1所述的处理器,其特征在于,运算模块包括:译码模块idm、计算单元alu和数据选择器mux;其中:

3.根据权利要求2所述的处理器,其特征在于,运算模块,还包括:写回模块wbm;

4.根据权利要求3所述的处理器,其特征在于,

5.根据权利要求4所述的处理器,其特征在于,

6.根据权利要求1-5任一项所述的处理器,其特征在于,ifm,包括:待运算指令生成单元、简单译码单元、数据触发器、指针寄存器和指令寄存器;其中:

7.根据权利要求6所述的处理器,其特征在于,

8.根据权利要求6所述的处理器,其特征在于,

9.根据权利要求8所述的处理器,其特征在于,

技术总结

本发明实施例公开了一种处理器。该处理器包括:ITCM、DTCM、IFM、运算模块以及MEM;其中:ITCM,用于根据接收的不同触发信号确定匹配的目标指令集,并将目标指令集传输至IFM;IFM,用于根据目标指令集确定待运算指令,并将目标指令集以及待运算指令传输至运算模块,以指示运算模块进行工作;运算模块,用于对目标指令集进行译码,确定目标逻辑运算,并根据待运算指令指示MEM访问存储器获取待运算数据;DTCM,用于根据MEM的指示,提供待运算数据;运算模块,还用于将待运算数据按照目标逻辑运算进行运算,得到运算结果。该处理器定义内容简单,摒弃了繁多的通用性架构,实现简单、面积小、低功耗且性能高。

技术研发人员:冯笑天,黄俊桦,葛文洁

受保护的技术使用者:宸芯科技股份有限公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!