针对多FPGA芯片电路系统实现下载调试控制的电路结构的制作方法

针对多fpga芯片电路系统实现下载调试控制的电路结构

技术领域

1.本发明涉及可编程逻辑器件开发领域,尤其涉及多fpga芯片系统的下载调试领域,具体是指一种针对多fpga芯片电路系统实现下载调试控制的电路结构。

背景技术:

2.在可编程逻辑器件开发过程中,经常要使用到jtag接口对fpga芯片进行配置或者对逻辑进行调试。对于含有较多数量fpga芯片的系统或产品,传统的做法是采用串行链式jtag或者并联式jtag电路作为调试接口电路,如附图1与附图2所示。然而,串行链式或并联式jtag电路有如下缺点:

3.1、对于串行链式jtag电路,当fpga芯片数量过多的时候,tdi至tdo时延加大,导致jtag接口速率快速降低。这时,对于容量比较大的高端fpga芯片而言,其配置时长将变得不可接受,极大的增加了调试成本。

4.2、对于并联式jtag电路,当fpga芯片数量过多的时候,一方面要考虑jtag host的驱动能力,另一方面要考虑分支走线导致的信号反射引起信号完整性问题。这对电路与pcb设计有较高要求,在多板卡系统中,通常难以兼顾,严重时会引起电路故障,无法使用。

技术实现要素:

5.本发明的目的是克服了上述现有技术的缺点,提供了一种满足可靠性高、速率高、耗时低的针对多fpga芯片电路系统实现下载调试控制的电路结构。

6.为了实现上述目的,本发明的针对多fpga芯片电路系统实现下载调试控制的电路结构如下:

7.该针对多fpga芯片电路系统实现下载调试控制的电路结构,其主要特点是,所述的电路结构包括usb hub电路、usb转jtag模块、usb mux芯片、滑动开关、反相缓冲器芯片、电阻器和usb接口,所述的usb接口的输出端与滑动开关和usb mux芯片相连,所述的usb mux芯片的输出端与usb hub电路相连,所述的usb hub电路的输出端与多个usb转jtag模块相连,所述的滑动开关还与电阻器和外部的vbus电压相连,所述的电阻器的一端与反相缓冲器芯片的输入端相连,另一端接地,所述的反相缓冲器芯片的输出端分别与usb mux芯片和外部待调试目标fpga电路系统相连;

8.所述的电路结构通过滑动开关来选择vbus电压或usb信号,所述的usb hub电路用于连接不同的usb转jtag模块,所述的usb转jtag模块用于配合上位机软件进行fpga芯片的下载与调试;所述的usb mux芯片用于切换usb信号,所述的滑动开关用于切换连接电路的连接通路,所述的电阻器用于分压至合适电压值,并驱动反相缓冲器芯片产生控制信号。

9.较佳地,所述的电阻器包括第一电阻和第二电阻,所述的第一电阻的一端与滑动开关相连,另一端与反相缓冲器芯片的输入端相连,所述的第二电阻的一端与反相缓冲器芯片的输入端相连,另一端接地。

10.较佳地,所述的usb hub电路包括多个usb下行端口,每个usb下行端口均与usb转

jtag模块相连接。

11.较佳地,所述的拨动滑动开关,使usb接口上的vbus信号通过电阻器的两个分压电阻接地,所述的电路结构通过控制usb mux芯片来联通usb接口与usb hub电路。

12.采用了本发明的针对多fpga芯片电路系统实现下载调试控制的电路结构,通过适当设置usb hub电路下行端口数量,可在大规模数量fpga芯片系统中,通过单一usb接口,实现整个系统jtag调试电路的可靠连接,并保证连接速率最大化。同时电路应用于整机产品时,可使该调试usb接口与普通usb端口复用,不需要额外设计的调试接口。

附图说明

13.图1为现有技术的串行链式jtag电路示意图。

14.图2为现有技术的并联式jtag电路示意图。

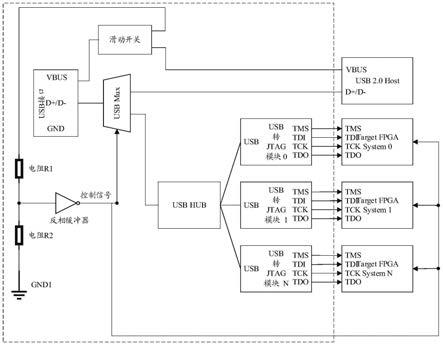

15.图3为本发明的针对多fpga芯片电路系统实现下载调试控制的电路结构的电路框图。

具体实施方式

16.为了能够更清楚地描述本发明的技术内容,下面结合具体实施例来进行进一步的描述。

17.本发明的该针对多fpga芯片电路系统实现下载调试控制的电路结构,其中包括usb hub电路、usb转jtag模块、usb mux芯片、滑动开关、反相缓冲器芯片、电阻器和usb接口,所述的usb接口的输出端与滑动开关和usb mux芯片相连,所述的usb mux芯片的输出端与usb hub电路相连,所述的usb hub电路的输出端与多个usb转jtag模块相连,所述的滑动开关还与电阻器和外部的vbus电压相连,所述的电阻器的一端与反相缓冲器芯片的输入端相连,另一端接地,所述的反相缓冲器芯片的输出端分别与usb mux芯片和外部待调试目标fpga电路系统相连;

18.所述的电路结构通过滑动开关来选择vbus电压或usb信号,所述的usb hub电路用于连接不同的usb转jtag模块,所述的usb转jtag模块用于配合上位机软件进行fpga芯片的下载与调试;所述的usb mux芯片用于切换usb信号,所述的滑动开关用于切换连接电路的连接通路,所述的电阻器用于分压至合适电压值,并驱动反相缓冲器芯片产生控制信号。

19.作为本发明的优选实施方式,所述的电阻器包括第一电阻和第二电阻,所述的第一电阻的一端与滑动开关相连,另一端与反相缓冲器芯片的输入端相连,所述的第二电阻的一端与反相缓冲器芯片的输入端相连,另一端接地。

20.作为本发明的优选实施方式,所述的usb hub电路包括多个usb下行端口,每个usb下行端口均与usb转jtag模块相连接。

21.作为本发明的优选实施方式,所述的拨动滑动开关,使usb接口上的vbus信号通过电阻器的两个分压电阻接地,所述的电路结构通过控制usb mux芯片来联通usb接口与usb hub电路。

22.本发明的具体实施方式中,在多fpga芯片系统中,保证jtag接口可靠的工作,且速率不随着fpga芯片数量增加而降低,节省宝贵的调试时间。

23.一种适用于多fpga芯片系统的下载调试电路,其系统框图如附图3虚线框部分所

示,包含usb hub电路,usb转jtag模块,usb mux芯片,滑动开关,反相缓冲器芯片,电阻器以及usb接口。

24.该电路通过滑动开关来决定usb接口是用于正常的usb host接口功能或者用于fpga调试下载功能;电阻器分压至合适电压值,驱动反向缓冲芯片产生控制信号;usb mux芯片用来切换usb信号;usb hub电路连接位于不同fpga目标系统上的usb转jtag模块;usb转jtag模块配合上位机软件完成fpga芯片的下载与调试功能。

25.当产品开发调试完成后,可通过切换滑动开关,切换vbus电压与usb信号通路至正常usb host电路,使本电路的usb接口作为产品上正常的usb host接口使用。

26.在本发明的具体实施例中,usb接口采用usb 2.0type a型连接器,usb mux芯片采用ti公司的hd3ss3411trwarq1,usb hub芯片采用cypress公司的cy7c65630-56ltxc,反相缓冲器采用ti公司的sn74lvc1g04dbvr,滑动开关采用c&k公司的1201m2s3abe2,usb转jtag模块采用digilent公司的410-308-b,电阻阻值采用10k欧姆。

27.该实例电路通过4片cy7c65630-56ltxc级联构成1分10的usb hub电路,共产生10个usb下行端口,每个usb下行端口连接至1个位于独立的fpga目标系统上的usb转jtag模块。

28.拨动滑动开关,使usb接口上的vbus信号通过两颗分压电阻r1、r2接地,此时将上位机pc usb host端口通过usb公对公的线缆与本实例电路usb接口连接,则来自上位机usb端口的5v vbus电压将在分压电阻之间产生一个2.5v的电压,该电压驱动反相缓冲器芯片产生低电平控制信号,该控制信号通过控制usb mux芯片使本实例电路usb接口与usb hub电路联通,从而pc上位机可以通过usb接口访问位于每一fpga目标系统上的usb转jtag模块,进而通过该模块完成fpga芯片的配置与调试工作。

29.当产品开发调试完成后,可通过切换滑动开关,反相器输入信号变为低电平,控制信号变为高电平,从而本实例电路usb接口与系统中正常的usb host端口联通,实现了该本实例电路usb接口与普通usb端口复用,同时切断了对外调试接口,增强了产品的技术保密性。

30.采用了本发明的针对多fpga芯片电路系统实现下载调试控制的电路结构,通过适当设置usb hub电路下行端口数量,可在大规模数量fpga芯片系统中,通过单一usb接口,实现整个系统jtag调试电路的可靠连接,并保证连接速率最大化。同时电路应用于整机产品时,可使该调试usb接口与普通usb端口复用,不需要额外设计的调试接口。

31.在此说明书中,本发明已参照其特定的实施例作了描述。但是,很显然仍可以作出各种修改和变换而不背离本发明的精神和范围。因此,说明书和附图应被认为是说明性的而非限制性的。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1