一种应用于处理器的I2C电平转换装置及其方法与流程

一种应用于处理器的i2c电平转换装置及其方法

技术领域

1.本发明属于电子技术领域,尤其涉及一种应用于处理器的i2c电平转换装置及其方法。

背景技术:

2.处理器ft-2000/4的i2c接口为1.8v的io电平类型,i2c外设多是3.3v电平类型,解决这一不兼容问题,传统方案是使用i2c专用电平转换芯片进行电平转换。针对当前的社会需求,国产化要求越来越高,核心板越做越小,国产化芯片可选择性小,传统方案不能满足当前的社会需求。

技术实现要素:

3.本发明的目的是提供一种应用于处理器的i2c电平转换装置及其方法,解决了ft-2000/4处理器不兼容不同电平标准的i2c外设的技术问题。

4.为实现上述目的,本发明采用如下技术方案:

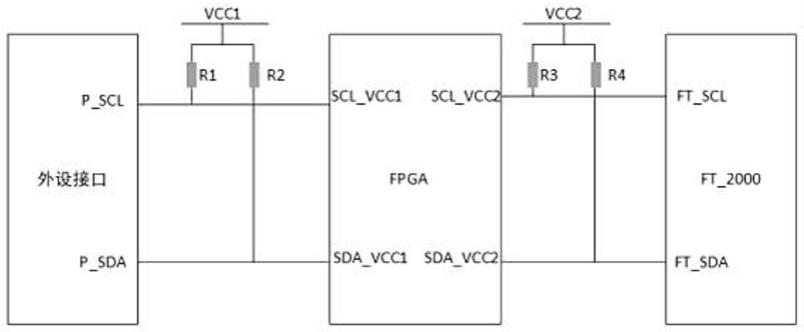

5.一种应用于处理器的i2c电平转换装置,包括外设接口、电阻r1、电阻r2、fpga控制器、电阻r3、电阻r4和处理器ft_2000,外设接口的i2c通信端包括p_scl接口和p_sda接口,fpga控制器的第一i2c接口包括scl_vcc1接口和sda_vcc1接口,fpga控制器的第二i2c接口包括scl_vcc2接口和sda_vcc2接口,处理器ft_2000的i2c接口包括ft_scl接口和ft_sda接口,接口p_scl接口连接scl_vcc1接口,电阻r1为scl_vcc1接口的上拉电阻,接口p_sda接口连接sda_vcc1接口,电阻r2为sda_vcc1接口的上拉电阻,接口ft_scl接口连接scl_vcc2接口,电阻r3为scl_vcc2接口的上拉电阻,接口ft_sda接口连接sda_vcc2接口,电阻r4为sda_vcc2接口的上拉电阻。

6.优选的,所述外设接口用于连接外部兼容i2c接口的芯片,所述fpga控制器的的型号为gw1n-9型fpga处理器,所述处理器ft_2000的型号为ft-2000/4。

7.优选的,所述电阻r1和电阻r2连接的电源为电源vcc1,所述电阻r3和电阻r4连接的电源为电源vcc2。

8.优选的,所述电源vcc1的电压为3.3v或5v,所述电源vcc2的电压为所述处理器ft_2000的工作电压。

9.一种应用于处理器的i2c电平转换方法,包括如下步骤:

10.步骤1:建立一种应用于处理器的i2c电平转换装置;

11.步骤2:将外设接口的p_scl接口和处理器ft_2000的ft_scl接口都分别置为高阻状态,跳转到步骤3;

12.步骤3:fpga处理器检测scl_vcc1接口和scl_vcc2接口的电平是否都为高电平:是,跳转到步骤4;否,执行步骤3;

13.步骤4:fpga处理器检测scl_vcc2接口是否为高,是,跳转到步骤10;否,跳转到步骤5;

14.步骤5:fpga控制器置scl_vcc1接口为低电平,跳转到步骤6;

15.步骤6:fpga控制检测scl_vcc2接口是否为高电平:是,跳转到步骤7;否,跳转到步骤6;

16.步骤7:fpga控制器置scl_vcc1接口为高电平,跳转到步骤8;

17.步骤8:fpga控制器检测scl_vcc1接口是否为高电平:是,跳转到步骤9;否,跳转到步骤8;

18.步骤9:fpga控制器置scl_vcc1接口为高阻状态,跳转到步骤4;

19.步骤10:fpga控制器检测scl_vcc1接口是否为高电平:是,跳转到步骤4;否,跳转到步骤11;

20.步骤11:fpga控制器置scl_vcc2接口为低电平,跳转到步骤12;

21.步骤12:fpga控制器检测scl_vcc1接口是否为高电平:是,跳转到步骤13;否,跳转到步骤12;

22.步骤13:fpga控制器置scl_vcc2接口为高电平,跳转到步骤14;

23.步骤14:fpga控制器检测scl_vcc2接口是否为高,是,跳转到步骤15;否,跳转到步骤14;

24.步骤15:fpga控制器置scl_vcc2接口为高阻状态,跳转到步骤4。

25.本发明所述的一种应用于处理器的i2c电平转换装置及其方法,解决了ft-2000/4处理器不兼容不同电平标准的i2c外设的技术问题,本发明实现信号的上升沿不依赖上拉电阻、电路容抗、芯片驱动能力的因素,提升i2c通信速度;适用于不同电平标准的飞腾i2c外设;满足当前国产化要求越来越高的社会需求。

附图说明

26.图1是本发明的硬件结构示意图;

27.图2是本发明的处理器ft_2000的电路图;

28.图3是本发明的fpga控制器的电路图;

29.图4是本发明的外设接口的电路图;

30.图5是本发明的流程图。

具体实施方式

31.实施例1:

32.由图1-图4所示的一种应用于处理器的i2c电平转换装置,包括外设接口、电阻r1、电阻r2、fpga控制器、电阻r3、电阻r4和处理器ft_2000,外设接口的i2c通信端包括p_scl接口和p_sda接口,fpga控制器的第一i2c接口包括scl_vcc1接口和sda_vcc1接口,fpga控制器的第二i2c接口包括scl_vcc2接口和sda_vcc2接口,处理器ft_2000的i2c接口包括ft_scl接口和ft_sda接口,接口p_scl接口连接scl_vcc1接口,电阻r1为scl_vcc1接口的上拉电阻,接口p_sda接口连接sda_vcc1接口,电阻r2为sda_vcc1接口的上拉电阻,接口ft_scl接口连接scl_vcc2接口,电阻r3为scl_vcc2接口的上拉电阻,接口ft_sda接口连接sda_vcc2接口,电阻r4为sda_vcc2接口的上拉电阻。

33.本实施例中,i2c接口是开漏结构,fpga控制器管脚工作频率远高于i2c正常通信

速率,在电平转换的过程中,fpga控制器先驱动信号线从低电平到高电平跳变,当i2c信号线上的电平满足高电平判断门限时,fpga控制器释放i2c信号线,即管脚置高阻状态,电阻r1、电阻r2、电阻r3和电阻r4用于实现端口的上拉过程。

34.如图1所示,ft_scl、ft_sda通过2kω的上拉电阻连接到电源vdd_io,同时,该信号连接了ft2000-4和gw1n-9(国产fpga)的芯片管脚,vdd_io是1.8v电源。p_scl、p_sda通过2kω的上拉电阻连接到电源p3v3_aux,同时,该信号连接了rjgt102wdt6和gw1n-9(国产fpga)的芯片管脚,p3v3_aux是3.3v电源。

35.优选的,所述外设接口用于连接外部兼容i2c接口的芯片,所述fpga控制器的的型号为gw1n-9型fpga处理器,本实施例中,具体采用的型号为gw1n-uv9ug169i5型。所述处理器ft_2000的型号为ft-2000/4。

36.如图4所示,本实施例中,外设接口连接了一个加密芯片u26,其型号为rjgt102wdt6,可作为看门狗使用。

37.优选的,所述电阻r1和电阻r2连接的电源为电源vcc1,所述电阻r3和电阻r4连接的电源为电源vcc2。

38.优选的,所述电源vcc1的电压为3.3v或5v,所述电源vcc2的电压为所述处理器ft_2000的工作电压。

39.实施例2:

40.如图5所示,实施例2所述的一种应用于处理器的i2c电平转换方法是在实施例1所述的一种应用于处理器的i2c电平转换装置的基础上实现的,包括如下步骤:

41.步骤1:建立一种应用于处理器的i2c电平转换装置;

42.步骤2:将外设接口的p_scl接口和处理器ft_2000的ft_scl接口都分别置为高阻状态,跳转到步骤3;

43.在以下步骤中,fpga处理器检测scl_vcc1接口和scl_vcc2接口在硬件上相当于fpga处理器检测了p_scl接口和ft_scl接口,即fpga处理器对scl_vcc1接口和scl_vcc2接口的检测均相当于是对p_scl接口和ft_scl接口的检测。

44.而fpga处理器对scl_vcc1接口和scl_vcc2接口的置高电平的操作,也相当于对p_scl接口和ft_scl接口进行了一次高电平置位操作。

45.步骤3:fpga处理器检测scl_vcc1接口和scl_vcc2接口的电平是否都为高电平:是,跳转到步骤4;否,执行步骤3;

46.步骤4:fpga处理器检测scl_vcc2接口是否为高,是,跳转到步骤10;否,跳转到步骤5;

47.步骤5:fpga控制器置scl_vcc1接口为低电平,跳转到步骤6;

48.步骤6:fpga控制检测scl_vcc2接口是否为高电平:是,跳转到步骤7;否,跳转到步骤6;

49.步骤7:fpga控制器置scl_vcc1接口为高电平,跳转到步骤8;

50.步骤8:fpga控制器检测scl_vcc1接口是否为高电平:是,跳转到步骤9;否,跳转到步骤8;

51.步骤9:fpga控制器置scl_vcc1接口为高阻状态,跳转到步骤4;

52.步骤10:fpga控制器检测scl_vcc1接口是否为高电平:是,跳转到步骤4;否,跳转

到步骤11;

53.步骤11:fpga控制器置scl_vcc2接口为低电平,跳转到步骤12;

54.步骤12:fpga控制器检测scl_vcc1接口是否为高电平:是,跳转到步骤13;否,跳转到步骤12;

55.步骤13:fpga控制器置scl_vcc2接口为高电平,跳转到步骤14;

56.步骤14:fpga控制器检测scl_vcc2接口是否为高,是,跳转到步骤15;否,跳转到步骤14;

57.步骤15:fpga控制器置scl_vcc2接口为高阻状态,跳转到步骤4。

58.本发明首先将fpga的两路i2c信号都输出高阻,再采样飞腾处理器端和外设端的i2c信号,任何一端出现低电平时(假设a端),fpga将该低电平传递给另一端(假设b端),最后当a端低电平释放时,fpga先在b端输出高电平,同时检测b端实际电路电平,当b端实际电路电平为高,则fpga将b端i2c信号置高阻。

59.本发明所述的一种应用于处理器的i2c电平转换装置及其方法,解决了ft-2000/4处理器不兼容不同电平标准的i2c外设的技术问题,本发明实现信号的上升沿不依赖上拉电阻、电路容抗、芯片驱动能力的因素,提升i2c通信速度;适用于不同电平标准的飞腾i2c外设;满足当前国产化要求越来越高的社会需求。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1