一种版图对比中验证单位版图的排序方法与流程

1.本发明涉及集成电路pdk验证领域,具体地,涉及版图对比中验证单位版图的排序方法。

背景技术:

2.集成电路工艺设计包(process design kit,pdk)是连接ic工艺制造和ic设计的数据平台,实现了ic工艺数据/模型与ic设计环境/工具的无缝集成,所以确保pdk的质量至关重要。

3.随着集成电路的发展,pdk中包含的元器件数目越来越多,器件也越来越复杂,其中的cdf参数也是越来越多。一个器件往往需要生成成千上万的测试版图来进行pdk后端的验证,但是画布的面积是有限的,如果不进行优秀的版图排序方法,则会产生版图的重叠甚至超出画布面积的情况。

技术实现要素:

4.为了解决现有技术存在的不足,本发明的目的在于提供一种版图对比中验证单位版图的排序方法,根据不同器件版图的形状,数量进行验证单位版图和版图行列数的设定,使最终版图的画布利用率大大提高,且提高了用户对特定版图的查找效率。

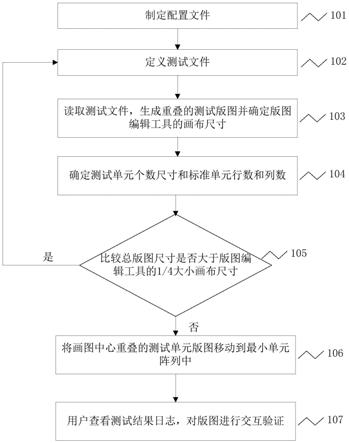

5.为实现上述目的,本发明提供的一种版图对比中验证单位版图的排序方法,包括以下步骤:

6.1)制定配置文件;

7.2)定义测试文件;

8.3)读取测试文件,生成重叠的测试版图并确定版图编辑工具的画布尺寸;

9.4)确定测试单元个数尺寸和标准单元行数和列数;

10.5)比较总版图尺寸是否大于版图编辑工具的1/4大小画布尺寸;

11.6)将画图中心重叠的测试单元版图移动到标准单元阵列中;

12.7)用户查看测试结果日志,对版图进行交互验证。

13.进一步地,所述步骤1)中需要制定的配置文件包括需要比较的两种或两种以上的集成电路工艺设计包文件、文件路径以及工作区路径。

14.进一步地,所述步骤2)中需定义的测试文件内容包括被测器件的类型、名字、器件描述格式参数、测试单元个数。

15.进一步地,所述步骤3)通过eda软件来读取步骤2)中定义的测试文件,版图编辑工具画布中心生成重叠的测试单元版图,通过eda软件来获取版图编辑工具的画布尺寸。

16.进一步地,所述步骤4)进一步包括以下步骤:

17.确定标准单元尺寸:通过eda软件获取测试单元版图中最大的尺寸,具体为宽度和长度,并将此最大尺寸作为标准单元尺寸;

18.通过eda软件读取测试文件获取测试单元数量,标准单元数量等于测试单元数量,

根据确保总版图长宽尽可能相等的原则以及根据标准单元宽长比例确定标准单元排列的行数和列数。

19.进一步地,所述步骤5)通过eda软件对总版图尺寸与版图编辑工具的1/4大小画布尺寸进行比较:

20.如果总版图尺寸小于或等于版图编辑工具的1/4大小画布尺寸,则进行步骤6);

21.如果总版图尺寸大于版图编辑工具的1/4大小画布尺寸,则返回步骤2),修改测试文件,并重复步骤2)-步骤5)。

22.更进一步地,在所述步骤6),通过eda软件来调用版图编辑工具,将画布中心重叠的测试单元版图移动到最小单元阵列中,以供用户进行版图比较。

23.为实现上述目的,本发明还提供一种版图对比中验证单位版图的排序的装置,包括存储器和处理器,所述存储器上储存有在所述处理器上运行的程序,所述处理器运行所述程序时执行上述的一种版图对比中验证单位版图的排序方法的步骤。

24.为实现上述目的,本发明还提供一种计算机可读存储介质,其上存储有计算机指令,所述计算机指令运行时执行上述的一种版图对比中验证单位版图的排序方法的步骤。

25.有益效果:通过本发明的方法,版图编辑工具的画布利用率提高了,对于具有很多独立cdf参数的器件,可以设置大量的pattern进行测试。对于相邻测试单元版图与测试单元版图之间的x轴方向距离和y轴方向距离均可以通过程序分析配置文件而生成一个默认值,避免测试单元版图重叠的情况,且无需用户自行判断间距。测试单元版图按照pattern的顺序进行棋盘状排序,避免结果验证中pattern设置参数和测试单元版图不一致,却很难定位错误的问题。

26.本发明的其它特征和优点将在随后的说明书中阐述,并且,部分地从说明书中变得显而易见,或者通过实施本发明而了解。

附图说明

27.附图用来提供对本发明的进一步理解,并且构成说明书的一部分,并与本发明的实施例一起,用于解释本发明,并不构成对本发明的限制。在附图中:

28.图1为根据本发明的一种版图对比中验证单位版图的排序方法流程图。

具体实施方式

29.以下结合附图对本发明的优选实施例进行说明,应当理解,此处所描述的优选实施例仅用于说明和解释本发明,并不用于限定本发明。

30.图1为根据本发明的一种版图对比中验证单位版图的排序方法流程图,下面将参考图1,对本发明的一种版图对比中验证单位版图的排序方法进行详细描述。

31.在步骤101,制定配置文件。

32.在该步骤中需要制定配置文件,具体包括准备需要比较的两种或两种以上的集成电路工艺设计包(process design kit,pdk)文件、文件路径以及工作区路径。

33.在步骤102,定义测试文件。

34.在该步骤中,需定义的测试文件内容包括被测器件的类型、名字、器件描述格式(component description format,cdf)参数、测试单元(pattern)个数等。

35.在步骤103,读取测试文件,生成重叠的测试版图并确定版图编辑工具的画布尺寸。

36.在该步骤中,通过eda软件来读取步骤102中定义的测试文件,版图编辑工具画布中心生成重叠的测试单元版图,同时也通过eda软件来获取版图编辑工具的画布尺寸。

37.在步骤104,确定测试单元个数尺寸和标准单元行数和列数。

38.在该步骤中,首先需要确定标准单元尺寸,在本发明中,将通过eda软件获取的测试单元版图中最大的尺寸定义为标准单元尺寸,即通过eda软件获取测试单元版图中最大的尺寸,并将此最大尺寸作为标准单元尺寸。

39.然后,通过eda软件读取测试文件获取测试单元(pattern)数量。标准单元数量等于测试单元数量,根据确保总版图长宽尽可能相等的原则以及根据标准单元宽长比例确定其排列的行数和列数。

40.画布和绝大部分器件都是矩形的而画布是正方形,也就是说,在排布标准单元时需要尽可能使得最终排布版图总和趋近于正方形。因而,根据标准单元的长宽比例以及其数量并且在确保总版图长宽尽可能相等的原则下可以确定标准单元排列的行数和列数。

41.在步骤105,比较总版图尺寸是否大于版图编辑工具的1/4大小画布尺寸。

42.在该步骤中,通过eda软件对总版图尺寸与版图编辑工具的1/4大小画布尺寸进行比较:

43.如果总版图尺寸小于或等于版图编辑工具的1/4大小画布尺寸,则进行步骤106;

44.如果总版图尺寸大于版图编辑工具的1/4大小画布尺寸,则返回步骤102,修改测试文件,并重复步骤102-105。

45.对测试文件的修改是指修改cdf参数使得最大的被测器件尺寸缩小或者减少测试器件的数量,最终使得最后的总版图小于画布1/4。

46.在步骤106,将画图中心重叠的测试单元版图移动到最小单元阵列中。

47.在该步骤中,通过eda软件来调用版图编辑工具,将画布中心重叠的测试单元版图移动到最小单元阵列中,以供用户进行版图比较。

48.在步骤107,用户查看测试结果日志,对版图进行交互验证。

49.本发明还提供版图对比中验证单位版图的排序的装置,包括存储器和处理器,存储器上储存有在处理器上运行的程序,处理器运行所述程序时执行上述一种版图对比中验证单位版图的排序方法的步骤。

50.本发明还提供了一种计算机可读存储介质,其上存储有计算机指令,所述计算机指令运行时执行上述的一种版图对比中验证单位版图的排序方法的步骤,所述一种版图对比中验证单位版图的排序方法参见前述部分的介绍,不再赘述。

51.本领域普通技术人员可以理解:以上所述仅为本发明的优选实施例而已,并不用于限制本发明,尽管参照前述实施例对本发明进行了详细的说明,对于本领域的技术人员来说,其依然可以对前述各实施例记载的技术方案进行修改,或者对其中部分技术特征进行等同替换。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1