三光子深层组织成像方法及装置与流程

1.本发明涉及计算机技术领域,尤其是涉及一种三光子深层组织成像方法及装置。

背景技术:

2.光学成像在基础生物学研究和临床诊断中都发挥着重要作用,它为研究生物组织提供了一种非侵入性、微创的显微成像的方法。而进行生物深层组织成像一直以来是一项较大的科学挑战,组织的密度分布极其不均匀以及组织成分的强烈散射限制了成像的分辨率。

3.多光子显微镜是一种强大的功能成像技术,它已经被广泛应用于深层组织生命现象的观测。传统的单光子荧光显微镜在观测时,一个分子或者原子每次只能吸收一个光子,从基态跃迁到激发态。而当光强足够高时,就会产生多光子跃迁,即一次可以吸收多个光子。以荧光物质的双光子吸收为例:荧光分子同时吸收两个相同频率的光子,被激发跃升至高能级,经过一个弛豫过程后发生自发跃迁回到低能级,辐射出一个频率略小于两倍入射光频率的荧光光子。由此可知,荧光分子的多光子激发需要的激光波长比单光子长,且多光子激发只能产生在焦点附近的一个极小区域中。这给多光子显微镜带来了诸多优势,如对生物样品的光损伤小,有效观测时间长,穿透深度深,荧光收集率高等。在过去的30年里,双光子显微镜使体内功能成像发生了革命性的变化,使高空间分辨率、神经生理学记录在散射脑内达到前所未有的规模和深度。尽管双光子激发可以有效减少焦面外的荧光,但随成像深度呈指数增长,噪声强度最终变得与非稀疏标记样品中的信号相当,从而不可逆转地降低了成像质量。而且脑深部成像的最佳激发波长在1300纳米和1700纳米左右,长于大多数现有荧光探针的双光子激发光的波长。

4.近年来,三光子显微技术应运而生。在三光子成像过程中,荧光分子同时吸收三个相同频率的光子后辐射出荧光光子。跟双光子技术相比,成像过程中其激发光波长更长,并且需要更高阶非线性激发,这带来了以下两个优势:(1)三光子显微镜具有更高的深度成像信号生成效率。随着激发光波长增加,光在穿越组织过程中的信号衰减减少。(2)三光子显微镜对于深度成像具有更高的信背比(想探测的信号和背景的比值)。多光子成像中的失焦背景由本体背景和离焦背景两个主要组成部分。本体背景是指远离焦点的光锥中产生的荧光,离焦背景是指畸变点扩散函数的旁瓣产生的荧光。这两种背景都会导致图像对比度的降低,并导致衍射有限焦体积以外的荧光生成。而三光子显微镜更长的波长和更高阶的非线性激发有利于抑制这两种背景。

5.但是纵观各种荧光显微成像技术,它们都面临一个共同的难题,那就是成像信噪比(信号和噪声的比值)的限制。图像信噪比过低严重限制着显微系统的性能。由于只有当数据具有足够的信噪比时,才能进行下游分析并得出可靠的结论,因此生物学家进行实验时,往往不得不牺牲成像速度、成像深度、成像时长、甚至组织活性以提升成像信噪比。特别是在三光子的深层组织成像过程中,发出的荧光光子在穿越组织过程中会有不可避免的衰减,这样会导致成像信噪比降低,影响图像质量。

技术实现要素:

6.本发明的目的在于提供一种三光子深层组织成像方法及装置,旨在解决现有技术中的上述问题。

7.本发明提供一种三光子深层组织成像方法,包括:

8.从三光子显微镜捕获低信噪比图像,将所述低信噪比图像以连续数据流的方式输入高性能运算单元;

9.通过所述高性能运算单元上部署的预先训练好的数据增强网络对所述连续数据流进行处理,得到增强后的高信噪比数据流;

10.将所述高信噪比数据流在显示器上进行同步显示。

11.本发明提供一种三光子深层组织成像装置,包括:

12.捕获模块,用于从三光子显微镜捕获低信噪比图像,将所述低信噪比图像以连续数据流的方式输入高性能运算单元;

13.处理模块,用于通过所述高性能运算单元上部署的预先训练好的数据增强网络对所述连续数据流进行处理,得到增强后的高信噪比数据流;

14.显示模块,用于将所述高信噪比数据流在显示器上进行同步显示。

15.采用本发明实施例,在不影响成像时空分辨率的前提下,提高三光子深层组织成像信噪比,并且实现算法嵌入显微硬件装置,实现实时去噪。

16.上述说明仅是本发明技术方案的概述,为了能够更清楚了解本发明的技术手段,而可依照说明书的内容予以实施,并且为了让本发明的上述和其它目的、特征和优点能够更明显易懂,以下特举本发明的具体实施方式。

附图说明

17.为了更清楚地说明本发明具体实施方式或现有技术中的技术方案,下面将对具体实施方式或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图是本发明的一些实施方式,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

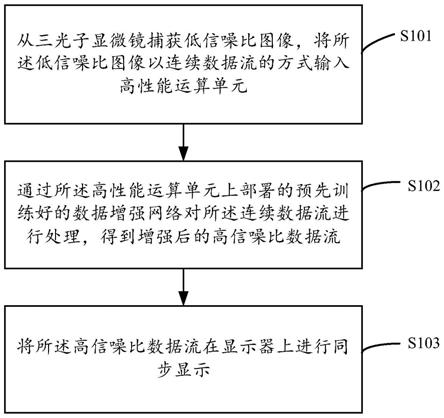

18.图1是本发明实施例的三光子深层组织成像方法的流程图;

19.图2是本发明实施例的三光子深层组织成像智能增强方法的原理图以及数据处理流程;

20.图3是本发明实施例的用于训练增强网络的自监督训练方法的示意图;

21.图4是本发明实施例的训练后的增强网络的数据处理方法的示意图;

22.图5是本发明实施例的基于批处理的实时数据处理时序图;

23.图6是本发明实施例的三光子深层组织成像装置的示意图。

具体实施方式

24.下面将结合实施例对本发明的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

25.在本发明的描述中,需要理解的是,术语“中心”、“纵向”、“横向”、“长度”、“宽度”、“厚度”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”、“内”、“外”、“顺时针”、“逆时针”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。

26.此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个所述特征。在本发明的描述中,“多个”的含义是两个或两个以上,除非另有明确具体的限定。此外,术语“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通。对于本领域的普通技术人员而言,可以具体情况理解上述术语在本发明中的具体含义。

27.方法实施例

28.根据本发明实施例,提供了一种三光子深层组织成像方法,图1是本发明实施例的三光子深层组织成像方法的流程图,如图1所示,根据本发明实施例的三光子深层组织成像方法具体包括:

29.步骤101,从三光子显微镜捕获低信噪比图像,将所述低信噪比图像以连续数据流的方式输入高性能运算单元;在步骤101中,从三光子显微镜捕获低信噪比图像具体包括:

30.通过三光子显微镜对样本进行持续拍摄得到低信噪比图像,通用成像接口将所述低信噪比图像转换为连续数据流,其中,所述连续数据流中包含不同的数据批次,每一批数据是时间上相邻的若干帧。

31.步骤102,通过所述高性能运算单元上部署的预先训练好的数据增强网络对所述连续数据流进行处理,得到增强后的高信噪比数据流;步骤102具体包括:

32.通过所述高性能运算单元上部署的预先训练好的数据增强网络以特定数据处理时序对所述连续数据流进行处理,其中,所述特定数据处理时序为包含六个数据批次的时序,其中任意两个相邻的数据批次之间有第一预定百分比的预留重叠;

33.处理之后的每个数据批次,丢弃其前后第二预定百分比的帧,仅保存和显示每个批次中间第三预定百分比的数据。

34.步骤103,将所述高信噪比数据流在显示器上进行同步显示。

35.在本发明实施例中,在使用数据增强网络之前,需要对其进行训练,具体地:

36.采用自监督学习方式训练用于数据增强的数据增强网络,其中,所述数据增强网络的网络架构采用三维“u形”卷积神经网络;

37.根据网络定义和使用的运算平台,对所述数据增强网络执行特定于网络和平台的推理优化算法,将所述数据增强网络中的层和张量进行融合,并生成推理引擎,通过消除冗余运算、重新排序和组合操作对所述数据增强网络的神经网络层级结构进行优化。其中,所述对所述数据增强网络执行特定于网络和平台的推理优化算法进一步包括:

38.1、在所述推理优化算法中提供将32位浮点运算减少到16位浮点数或8位整数的参数选项;

39.2、根据需求选择所述推理优化算法的浮点运算精度,在所述推理优化算法构建阶

段遍历多个操作符,找到与精度转换和网络结构转换组合在一起时速度最快的操作符;

40.3、根据不同的显卡构架和内核频率,选择不同的优化策略以及计算方式,确定最合适当前构架的计算方式;

41.4、指定每次推理优化的显存,并进行多线程操作,并行计算各种网络参数,降低模型编码器每一层的特征向量数量,对所述数据增强网络进行压缩。

42.综上所述,本发明实施例使用了无监督去噪网络和高性能的深度学习推理优化算法。所使用的基于深度学习的去噪网络是一种自监督学习算法,无需真值(不含噪声的图像)即可对网络进行训练。通过实验表明,显微成像过程中拍摄的视频具有时间冗余性,即任何两个连续帧都可以被视为同一图像的两种噪声采样。通过神经网络的损失函数,当网络的输入和输出分别为这两种噪声采样后的图片时,深度神经网络也可以通过训练收敛到噪声的均值,即实现图像增强的效果。此外,输入和输出数据被设计为三维而不是二维帧,以充分利用时空堆栈中的时空信息。

43.为了实现实时拍摄,实时处理的过程,本发明实施例还提供了一种高性能的深度学习推理优化算法,它可以为深度学习应用提供低延迟、高吞吐率的部署推理。该算法为提升模型推理速度实现了以下几个改进:(1)将神经网络中的层和张量(指多维数组,深度学习网络的数据单位)融合,以优化gpu(图形处理器的简称,指电脑中做图像和图形相关运算工作的微处理器)的显存(指gpu内存,它的作用是用来存储gpu芯片处理过或者即将提取的渲染数据)和带宽(指gpu与显存之间的数据传输速率)。在部署模型推理时,网络中每一层的运算操作都是由gpu完成的,但实际上是gpu通过启动不同的运算核心来完成计算的。该核心能对张量进行快速运算,但是大量时间往往会花费在运算核心的启动和对每一层输入或输出张量的读写操作上面,这造成了内存带宽的瓶颈和gpu资源的浪费。该算法通过对网络层间的横向或纵向合并,使得层的数量和占用的运算核心数大大减少,因此整个模型结构会更小,更快,更高效。(2)进行模型的精度压缩。大部分深度学习框架在训练神经网络时使用的张量都是32位浮点数的精度,将模型参数从常规精度压缩到8位整型或者16位浮点数的精度,可以显著提升模型执行速度,且实践表明这个操作对模型的推理效果影响较小。(3)进行网络内核自动调整。根据不同的显卡构架、内核频率等,选择不同的优化策略以及计算方式,寻找最合适当前构架的计算方式。(4)该算法会为每次推理指定显存,避免显存重复申请,以减少内存占用及提高内存重复使用效率。(5)实现多线程操作,最大化并行各种网络参数计算。(6)通过降低模型编码器每一层的特征向量数量,对网络进行了压缩,降低了显存。

44.在进行模型推理提速后,本发明实施例通过适合实时推理的工作流,采用多线程并行的设计思想,使得采集数据、读入数据、去噪、结果显示与存储多个任务同时高效进行。

45.与现有技术相比,本发明具有以下优点:(1)所述实时荧光成像智能增强方法能与三光子成像系统结合,能够进行深层组织成像。三光子显微镜的激发光波长更长,实验表明,三光子信号的有效衰减长度(反应光信号穿越组织的衰减程度,有效衰减长度越长,穿过组织衰减的越少)比双光子长两倍左右,所以与常用的共聚焦、双光子显微镜相比,三光子成像系统具有成像深度深,信号生成效率高,信背比高等特点。(2)为了采集高信噪比的图像,最直接的方法是使用高激发剂量的光进行照射,但其引发的光漂白,光毒性,和使组织局部温度升高等问题会对观测样品产生不可逆转的伤害,这限制了对组织的长时间成

像。还有人使用更加明亮的荧光指示剂和更敏感的光电检测器,但在光子受限的条件下(例如树突成像和深层组织成像),它们的性能仍然受到很大限制。除了这些物理或生物的方法,近年来数据驱动的深度学习方法成为人们研究的热点。但是现有模型往往需要花费大量的人力物力完成真值采集工作,而本发明实施例设计的自监督训练方法,即使没有真值,依然可以训练出性能优良的去噪模型。最终达到的效果是在不牺牲时空分辨率的前提下,将成像信噪比了提高十倍以上。为对其性能进行验证,该方法被使用在钙成像数据上,实验事实表明,增强算法可以提高神经元定位和迹线提取的准确性,并在很大程度上促进了对神经回路的分析。(3)现有图像增强的算法常常是和硬件系统分离的,需要先进行图像采集,再将保存下来的数据输入模型进行推理,这样的去噪效果不具有实时观测性。而本发明实施例通过合理地设计处理时序,所述方法能够实时显示增强的图像,增强后的图像不受噪声干扰,生物结构和生命过程变得清晰可见。实验结果表明,在进行优化部署后,模型参数和占用现存降低为原来的6%和30%,推理速度提升了10倍,且效果和提速前图像的相似度为0.998,说明该优化过程对图像推理效果是几乎没有影响的。

46.为使本发明的上述目的、特征和优点能够更加明显易懂,下面对照附图并结合优选的实施方式对本发明做进一步说明。本发明实施例提出一种实时的三光子成像智能增强方法,其原理及数据处理流程如图2所示:从荧光显微镜捕获的低信噪比图像以连续数据流的方式流入高性能运算单元,该单元上部署有训练好的数据增强网络,经过网络的处理,增强后的高信噪比数据流出高性能运算单元,在显示器上进行同步的显示。具体的方法包括:

47.1)所述实施例首先采用自监督学习方式预先训练用于数据增强的神经网络模型,如图3所示。本实施例中的网络架构采用三维“u形”卷积神经网络,它采用三维卷积核来提取特征,能够聚合时空信息,由于荧光显微成像的结构具有时间和空间上的相关性,充分聚合时空信息可以有效提升去噪的性能。针对实际应用中的真值缺乏的问题,本发明开发一种自监督的训练方法,无需训练真值,自动将原始的图像时间序列中的奇数帧和偶数帧分别作为输入和输出,即可使网络收敛到和用真值训练相当的性能。

48.2)下一步,训练后的模型经过自主设计的推理优化算法处理。该算法根据网络定义和使用的运算平台,执行特定于网络和平台的优化,并生成推理引擎。此阶段通过消除冗余运算、重新排序和组合操作来优化神经网络层级结构,从而使模型推理过程在gpu上更高效地运行。使用者还可以根据需求选择推理计算的精度,该算法提供将32位浮点运算减少到16位浮点数或8位整数的参数选项。构建阶段还会遍历多个操作符,以找到与精度转换和网络结构转换组合在一起时能够实现速度最快的操作符。在后续阶段的推理过程中,直接使用优化后的推理引擎对显微镜拍摄的数据进行增强。

49.3)三光子显微镜对样本进行持续拍摄,所拍摄的低信噪比图像经过通用成像接口被转换为连续数据流,其中包含不同的数据批次,每一批数据是时间上相邻的若干帧。连续数据流持续流入高性能运算单元,其上部署的预先训练好的模型按照图4所示的方法对流入数据进行处理,增强后的数据同样以连续数据流的形式流出,在显示器上进行同步的显示。

50.4)为实现实时的数据处理和显示,本发明对数据处理时序进行了严格的设计,一个包含六个数据批次的时序图如图5所示,任意两个相邻的数据批次之间有40%的预留重叠,处理之后的每个数据批次,其前后20%的帧将被丢弃,仅保存和显示每个批次中间60%

的数据。使用者也可根据自己的需求改变每个数据批次的帧数和不同数据批次之间重叠帧数。

51.装置实施例

52.根据本发明实施例,提供了一种三光子深层组织成像装置,图6是本发明实施例的三光子深层组织成像装置的示意图,如图6所示,根据本发明实施例的三光子深层组织成像装置具体包括:

53.捕获模块60,用于从三光子显微镜捕获低信噪比图像,将所述低信噪比图像以连续数据流的方式输入高性能运算单元;所述捕获模块60具体用于:

54.通过三光子显微镜对样本进行持续拍摄得到低信噪比图像,通用成像接口将所述低信噪比图像转换为连续数据流,其中,所述连续数据流中包含不同的数据批次,每一批数据是时间上相邻的若干帧。

55.处理模块62,用于通过所述高性能运算单元上部署的预先训练好的数据增强网络对所述连续数据流进行处理,得到增强后的高信噪比数据流;所述处理模块62具体用于:

56.通过所述高性能运算单元上部署的预先训练好的数据增强网络以特定数据处理时序对所述连续数据流进行处理,其中,所述特定数据处理时序为包含六个数据批次的时序,其中任意两个相邻的数据批次之间有第一预定百分比的预留重叠;

57.处理之后的每个数据批次,丢弃其前后第二预定百分比的帧,仅保存和显示每个批次中间第三预定百分比的数据。显示模块64,用于将所述高信噪比数据流在显示器上进行同步显示。

58.上述装置进一步包括:

59.训练模块,用于采用自监督学习方式训练用于数据增强的数据增强网络,其中,所述数据增强网络的网络架构采用三维“u形”卷积神经网络;

60.优化模块,用于根据网络定义和使用的运算平台,对所述数据增强网络执行特定于网络和平台的推理优化算法,将所述数据增强网络中的层和张量进行融合,并生成推理引擎,通过消除冗余运算、重新排序和组合操作对所述数据增强网络的神经网络层级结构进行优化。所述优化模块具体用于:在所述推理优化算法中提供将32位浮点运算减少到16位浮点数或8位整数的参数选项;根据需求选择所述推理优化算法的浮点运算精度,在所述推理优化算法构建阶段遍历多个操作符,找到与精度转换和网络结构转换组合在一起时速度最快的操作符;根据不同的显卡构架和内核频率,选择不同的优化策略以及计算方式,确定最合适当前构架的计算方式;指定每次推理优化的显存,并进行多线程操作,并行计算各种网络参数,降低模型编码器每一层的特征向量数量,对所述数据增强网络进行压缩。

61.本发明实施例是与上述方法实施例对应的装置实施例,各个模块的具体操作可以参照方法实施例的描述进行理解,在此不再赘述。

62.上述对本说明书特定实施例进行了描述。其它实施例在所附权利要求书的范围内。在一些情况下,在权利要求书中记载的动作或步骤可以按照不同于实施例中的顺序来执行并且仍然可以实现期望的结果。另外,在附图中描绘的过程不一定要求示出的特定顺序或者连续顺序才能实现期望的结果。在某些实施方式中,多任务处理和并行处理也是可以的或者可能是有利的。

63.在20世纪30年代,对于一个技术的改进可以很明显地区分是硬件上的改进(例如,

对二极管、晶体管、开关等电路结构的改进)还是软件上的改进(对于方法流程的改进)。然而,随着技术的发展,当今的很多方法流程的改进已经可以视为硬件电路结构的直接改进。设计人员几乎都通过将改进的方法流程编程到硬件电路中来得到相应的硬件电路结构。因此,不能说一个方法流程的改进就不能用硬件实体模块来实现。例如,可编程逻辑器件(programmable logic device,pld)(例如现场可编程门阵列(field programmable gate array,fpga))就是这样一种集成电路,其逻辑功能由用户对器件编程来确定。由设计人员自行编程来把一个数字系统“集成”在一片pld上,而不需要请芯片制造厂商来设计和制作专用的集成电路芯片。而且,如今,取代手工地制作集成电路芯片,这种编程也多半改用“逻辑编译器(logic compiler)”软件来实现,它与程序开发撰写时所用的软件编译器相类似,而要编译之前的原始代码也得用特定的编程语言来撰写,此称之为硬件描述语言(hardware description language,hdl),而hdl也并非仅有一种,而是有许多种,如abel(advanced boolean expression language)、ahdl(altera hardware description language)、confluence、cupl(cornell university programming language)、hdcal、jhdl(java hardware description language)、lava、lola、myhdl、palasm、rhdl(ruby hardware description language)等,目前最普遍使用的是vhdl(very-high-speed integrated circuit hardware description language)与verilog。本领域技术人员也应该清楚,只需要将方法流程用上述几种硬件描述语言稍作逻辑编程并编程到集成电路中,就可以很容易得到实现该逻辑方法流程的硬件电路。

64.控制器可以按任何适当的方式实现,例如,控制器可以采取例如微处理器或处理器以及存储可由该(微)处理器执行的计算机可读程序代码(例如软件或固件)的计算机可读介质、逻辑门、开关、专用集成电路(application specific integrated circuit,asic)、可编程逻辑控制器和嵌入微控制器的形式,控制器的例子包括但不限于以下微控制器:arc 625d、atmel at91sam、microchip pic18f26k20以及silicone labs c8051f320,存储器控制器还可以被实现为存储器的控制逻辑的一部分。本领域技术人员也知道,除了以纯计算机可读程序代码方式实现控制器以外,完全可以通过将方法步骤进行逻辑编程来使得控制器以逻辑门、开关、专用集成电路、可编程逻辑控制器和嵌入微控制器等的形式来实现相同功能。因此这种控制器可以被认为是一种硬件部件,而对其内包括的用于实现各种功能的装置也可以视为硬件部件内的结构。或者甚至,可以将用于实现各种功能的装置视为既可以是实现方法的软件模块又可以是硬件部件内的结构。

65.上述实施例阐明的系统、装置、模块或单元,具体可以由计算机芯片或实体实现,或者由具有某种功能的产品来实现。一种典型的实现设备为计算机。具体的,计算机例如可以为个人计算机、膝上型计算机、蜂窝电话、相机电话、智能电话、个人数字助理、媒体播放器、导航设备、电子邮件设备、游戏控制台、平板计算机、可穿戴设备或者这些设备中的任何设备的组合。

66.为了描述的方便,描述以上装置时以功能分为各种单元分别描述。当然,在实施本说明书实施例时可以把各单元的功能在同一个或多个软件和/或硬件中实现。

67.本领域内的技术人员应明白,本说明书一个或多个实施例可提供为方法、系统或计算机程序产品。因此,本说明书一个或多个实施例可采用完全硬件实施例、完全软件实施例、或结合软件和硬件方面的实施例的形式。而且,本说明书可采用在一个或多个其中包含

有计算机可用程序代码的计算机可用存储介质(包括但不限于磁盘存储器、cd-rom、光学存储器等)上实施的计算机程序产品的形式。

68.本说明书是参照根据本说明书实施例的方法、设备(系统)、和计算机程序产品的流程图和/或方框图来描述的。应理解可由计算机程序指令实现流程图和/或方框图中的每一流程和/或方框、以及流程图和/或方框图中的流程和/或方框的结合。可提供这些计算机程序指令到通用计算机、专用计算机、嵌入式处理机或其他可编程数据处理设备的处理器以产生一个机器,使得通过计算机或其他可编程数据处理设备的处理器执行的指令产生用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的装置。

69.这些计算机程序指令也可存储在能引导计算机或其他可编程数据处理设备以特定方式工作的计算机可读存储器中,使得存储在该计算机可读存储器中的指令产生包括指令装置的制造品,该指令装置实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能。

70.这些计算机程序指令也可装载到计算机或其他可编程数据处理设备上,使得在计算机或其他可编程设备上执行一系列操作步骤以产生计算机实现的处理,从而在计算机或其他可编程设备上执行的指令提供用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的步骤。

71.在一个典型的配置中,计算设备包括一个或多个处理器(cpu)、输入/输出接口、网络接口和内存。

72.内存可能包括计算机可读介质中的非永久性存储器,随机存取存储器(ram)和/或非易失性内存等形式,如只读存储器(rom)或闪存(flash ram)。内存是计算机可读介质的示例。

73.计算机可读介质包括永久性和非永久性、可移动和非可移动媒体可以由任何方法或技术来实现信息存储。信息可以是计算机可读指令、数据结构、程序的模块或其他数据。计算机的存储介质的例子包括,但不限于相变内存(pram)、静态随机存取存储器(sram)、动态随机存取存储器(dram)、其他类型的随机存取存储器(ram)、只读存储器(rom)、电可擦除可编程只读存储器(eeprom)、快闪记忆体或其他内存技术、只读光盘只读存储器(cd-rom)、数字多功能光盘(dvd)或其他光学存储、磁盒式磁带,磁带磁磁盘存储或其他磁性存储设备或任何其他非传输介质,可用于存储可以被计算设备访问的信息。按照本文中的界定,计算机可读介质不包括暂存电脑可读媒体(transitory media),如调制的数据信号和载波。

74.还需要说明的是,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、商品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、商品或者设备所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括所述要素的过程、方法、商品或者设备中还存在另外的相同要素。

75.本说明书一个或多个实施例可以在由计算机执行的计算机可执行指令的一般上下文中描述,例如程序模块。一般地,程序模块包括执行特定任务或实现特定抽象数据类型的例程、程序、对象、组件、数据结构等等。也可以在分布式计算环境中实践本说明书的一个或多个实施例,在这些分布式计算环境中,由通过通信网络而被连接的远程处理设备来执

行任务。在分布式计算环境中,程序模块可以位于包括存储设备在内的本地和远程计算机存储介质中。

76.本说明书中的各个实施例均采用递进的方式描述,各个实施例之间相同相似的部分互相参见即可,每个实施例重点说明的都是与其他实施例的不同之处。尤其,对于系统实施例而言,由于其基本相似于方法实施例,所以描述的比较简单,相关之处参见方法实施例的部分说明即可。

77.以上所述仅为本文件的实施例而已,并不用于限制本文件。对于本领域技术人员来说,本文件可以有各种更改和变化。凡在本文件的精神和原理之内所作的任何修改、等同替换、改进等,均应包含在本文件的权利要求范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1