一种基于单线的SWD调试系统及方法与流程

本发明涉及一种调试系统及方法,特别是涉及一种基于单线的swd调试系统及方法。

背景技术:

1、(serial wire debug,swd)是arm公司的一种双线同步调试接口。其中,adi5.0 toadi5.2的swd调试协议描述swd为一根数据线(swdio)和一根时钟线(swclk)组成的同步通讯接口,此接口可以对以arm为核心的微控制单元(microcontroller unit,mcu)进行调试。

2、swd调试协议规定swd的数据帧都由主机发起,从机被动响应,主机发起的通讯行为只有读、写两种。所述swd的数据帧由3个部分组成,读写数据帧分别如图1和图2所示。其中,header为数据帧头,ack为从机给主机的响应,wdata为主机对从机写数据,rdata为主机对从机读数据。header共包含8个bit,结构如图3所示,各个bit位的含义如表1所示。

3、表1、swd协议的基本操作说明

4、

5、swd调试协议规定header中的start、stop和park的取值固定为1、0和1。ack响应为3个bit,真值表如表2所示。

6、表2、ack响应的真值表

7、

8、

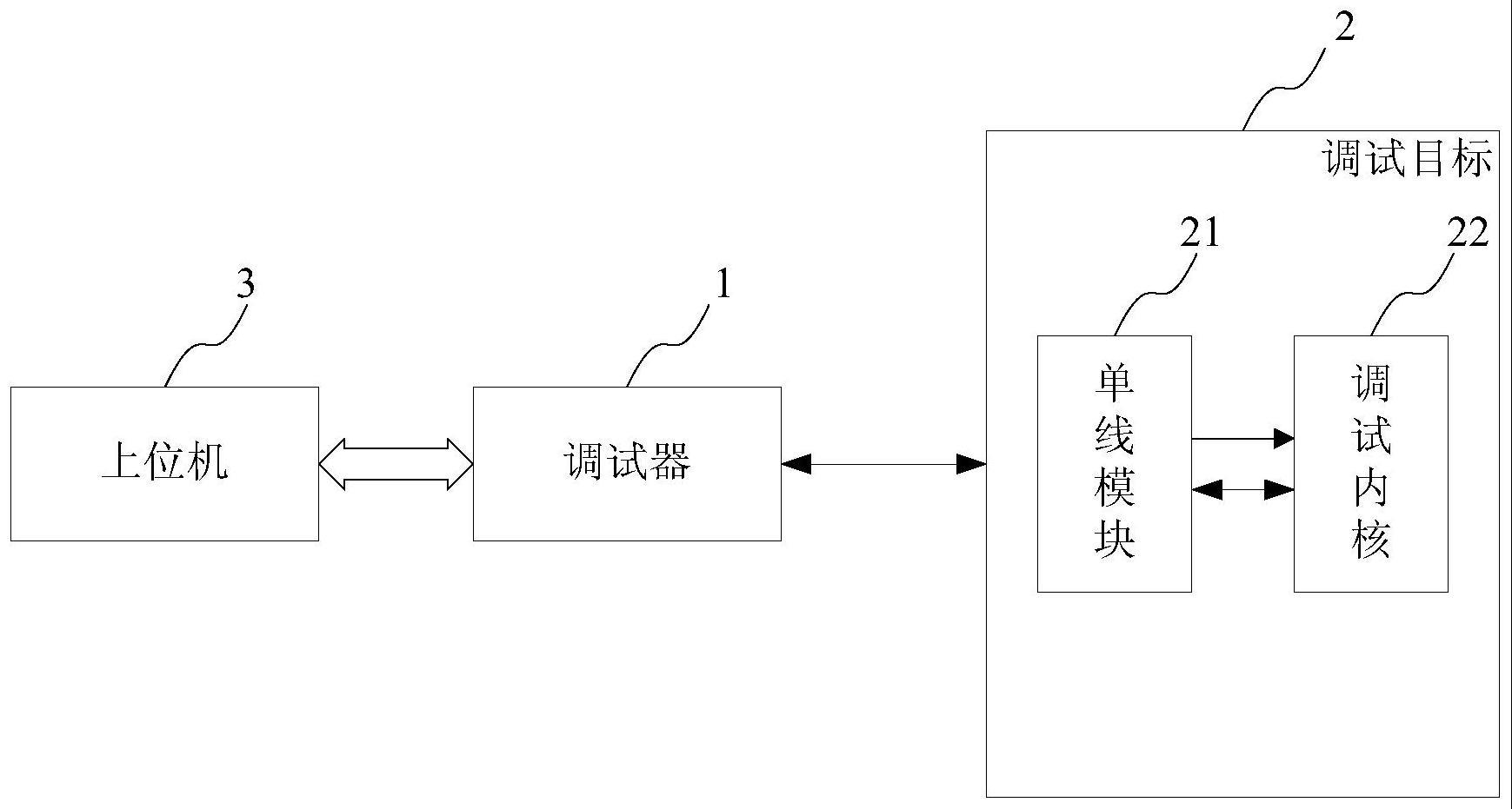

9、如图4所示,现有技术中基于arm swd协议的调试系统通常由调试目标、调试器和上位机组成。通常调试目标为mcu;调试器采用通用调试器,如jlink、ulink、dp-link等。其中,上位机作为主机,调试目标作为从机。在调试时,调试器是主机和从机之间的软件协议桥梁。优选地,上位机和调试器之间采用usb通讯,调试器解析上位机通过usb发送的满足usb协议的数据,将解析得到的数据基于swd调试协议通过swclk和swdio对从机进行调试控制、状态监测以及程序下载等操作。

10、上述的基于swd调试协议的调试方法采用mcu的两个管脚作为调试接口。对于mcu通常采用,尤其是小封装的mcu,其管脚数目非常少,而用户对mcu的gpio和功能管脚数量要求又很高。因此,基于swd调试协议进行调试时,挤占了用户可使用的管脚资源,影响了mcu的有效运行。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明的目的在于提供一种基于单线的swd调试系统及方法,能够基于一个管脚实现调试器与调试目标之间的单线调试,从而减少调试期间对管脚资源的占用。

2、为实现上述目的及其他相关目的,本发明提供一种基于单线的swd调试系统,包括调试器和调试目标;所述调试目标包括单线模块和调试内核;所述调试器用于基于接收到的调试指令生成基于swd调试协议的数据帧,并基于单线发送至所述单线模块;所述数据帧的帧头的start、stop和park取值为101时,表示所述数据帧为调试数据帧;当所述帧头的start、stop和park取值为010时,表示所述数据帧为单线模块数据帧;所述单线模块用于在接收到的数据帧为所述调试数据帧时,将所述数据帧发送至所述调试内核;在接收到的数据帧为单线模块数据帧时,对所述数据帧进行读写处理;所述调试内核用于基于接收到的数据帧进行调试处理。

3、于本发明一实施例中,所述数据帧的帧头包括8个bit,分别为start、rnw、a[0:2]、partiy、stop和park;其中rnw为读写识别位,a[0:2]为单线模块寄存器地址位,parity为rnw和a[0:2]的奇偶校验位。

4、于本发明一实施例中,所述单线模块还用于在接收到所述数据帧的帧头后,发送ack响应至所述调试器;当所述ack响应为100时,表示接收正确;当所述ack响应为011时,表示奇偶校验位错误。

5、于本发明一实施例中,所述数据帧的读数据和写数据满足swd调试协议。

6、于本发明一实施例中,还包括上位机,所述上位机用于发送所述调试指令至所述调试器。

7、本发明提供一种基于单线的swd调试方法,包括以下步骤:

8、调试器基于接收到的调试指令生成基于swd调试协议的数据帧,并基于单线发送至调试目标的单线模块;所述数据帧的帧头的start、stop和park取值为101时,表示所述数据帧为调试数据帧;当所述帧头的start、stop和park取值为010时,表示所述数据帧为单线模块数据帧;

9、所述单线模块在接收到的数据帧为所述调试数据帧时,将所述数据帧发送至所述调试目标的调试内核,以使所述调试内核基于接收到的数据帧进行调试处理;在接收到的数据帧为单线模块数据帧时,对所述数据帧进行读写处理。

10、于本发明一实施例中,所述数据帧的帧头包括8个bit,分别为start、rnw、a[0:2]、partiy、stop和park;其中rnw为读写识别位,a[0:2]为单线模块寄存器地址位,parity为rnw和a[0:2]的奇偶校验位。

11、于本发明一实施例中,所述单线模块还用于在接收到所述数据帧的帧头后,发送ack响应至所述调试器;当所述ack响应为100时,表示接收正确;当所述ack响应为011时,表示奇偶校验位错误。

12、于本发明一实施例中,所述数据帧的读数据和写数据满足swd调试协议。

13、于本发明一实施例中,还包括上位机用于发送调试指令至所述调试器。

14、如上所述,本发明的基于单线的swd调试系统及方法,具有以下有益效果:

15、(1)能够基于一个管脚实现调试器与调试目标之间的单线调试,从而减少调试期间对管脚资源的占用;

16、(2)调试管脚还可以提供测试、通讯等功能,提升了调试目标的管脚资源的利用率,极大地提升了调试目标的应用灵活性。

技术特征:

1.一种基于单线的swd调试系统,包括调试器和调试目标;所述调试目标包括单线模块和调试内核;

2.根据权利要求1所述的基于单线的swd调试系统,其特征在于:所述数据帧的帧头包括8个bit,分别为start、rnw、a[0:2]、partiy、stop和park;其中rnw为读写识别位,a[0:2]为单线模块寄存器地址位,parity为rnw和a[0:2]的奇偶校验位。

3.根据权利要求1所述的基于单线的swd调试系统,其特征在于:所述单线模块还用于在接收到所述数据帧的帧头后,发送ack响应至所述调试器;当所述ack响应为100时,表示接收正确;当所述ack响应为011时,表示奇偶校验位错误。

4.根据权利要求1所述的基于单线的swd调试系统,其特征在于:所述数据帧的读数据和写数据满足swd调试协议。

5.根据权利要求1所述的基于单线的swd调试系统,其特征在于:还包括上位机,所述上位机用于发送所述调试指令至所述调试器。

6.一种基于单线的swd调试方法,包括以下步骤:

7.根据权利要求6所述的基于单线的swd调试方法,其特征在于:所述数据帧的帧头包括8个bit,分别为start、rnw、a[0:2]、partiy、stop和park;其中rnw为读写识别位,a[0:2]为单线模块寄存器地址位,parity为rnw和a[0:2]的奇偶校验位。

8.根据权利要求6所述的基于单线的swd调试方法,其特征在于:所述单线模块还用于在接收到所述数据帧的帧头后,发送ack响应至所述调试器;当所述ack响应为100时,表示接收正确;当所述ack响应为011时,表示奇偶校验位错误。

9.根据权利要求6所述的基于单线的swd调试方法,其特征在于:所述数据帧的读数据和写数据满足swd调试协议。

10.根据权利要求6所述的基于单线的swd调试方法,其特征在于:还包括上位机用于发送调试指令至所述调试器。

技术总结

本发明提供一种基于单线的SWD调试系统及方法,包括调试器和调试目标;调试目标包括单线模块和调试内核;调试器用于基于接收到的调试指令生成基于SWD调试协议的数据帧,并基于单线发送至单线模块;数据帧的帧头的start、stop和park取值为101时,表示所述数据帧为调试数据帧;当帧头的start、stop和park取值为010时,表示数据帧为单线模块数据帧;单线模块用于在接收到的数据帧为调试数据帧时,将数据帧发送至调试内核;在接收到的数据帧为单线模块数据帧时,对数据帧进行读写处理;调试内核用于基于接收到的数据帧进行调试处理。本发明的基于单线的SWD调试系统及方法能够基于一个管脚实现调试器与调试目标之间的单线调试,从而减少调试期间对管脚资源的占用。

技术研发人员:肖安兵

受保护的技术使用者:华大半导体有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!