用于目标检测的后处理加速装置及方法、数据处理系统与流程

本发明涉及数据处理,具体涉及一种用于目标检测的后处理加速装置及方法,还涉及一种数据处理系统。

背景技术:

1、通常神经网络预处理后的数据经过人工智能加速器后,结果会存到加速器的存储器中,当主机得到计算完成的信号后,从加速器的存储器中读取计算结果后调用cpu去进行后处理。一般在cpu上完成的后处理操作包括:数据排布格式转换、数据类型转换以及比较筛选得到有效框数据,进而完成目标检测。其具体结构和流程如图1和图2所示。

2、ssd(single shot multibox detector,单激发多盒探测器)是一种one-stage(一级)的通用物体检测算法,ssd利用一个cnn(convolutional neural networks,卷积神经网络)预测出一系列的bbox(bounding boxes,边界框)以及相应的物体类别,然后利用nms(non-maximum suppression,非极大值抑制)算法得到最终的检测结果。一般ssd网络后处理数据大都以一个锚框(anchor_box)为基本单元进行排布,其数据格式如图3所示,其中每个锚框中包括其所在的坐标信息(x,y,w,h)、背景置信度数据(p0)、及各类别置信度数据(p1,p2…pn)。其特点在于需要找出p0-pn的最大值,如果最大值是p0,那么这是一个背景框,否则这是一个潜在的目标框(需要后续进一步判断)。经大量统计,对于ssd网络,进行后处理的95%以上的数据都为无效数据(也就是背景框),这大大浪费了后处理的时间,进而导致整个ssd网络检测时间增加。另外,现有方案将所有的数据都从人工智能加速器的存储器传输到主机存储器,会造成接口带宽浪费,降低加速器工作效率。

技术实现思路

1、本发明实施例一方面提供一种用于目标检测的后处理加速装置及方法,以减少后处理的时间,并节省接口带宽。

2、本发明实施例另一方面提供一种数据处理系统,以提高数据处理效率,节省处理时间。

3、为解决上述技术问题,本发明实施例提供如下技术方案:

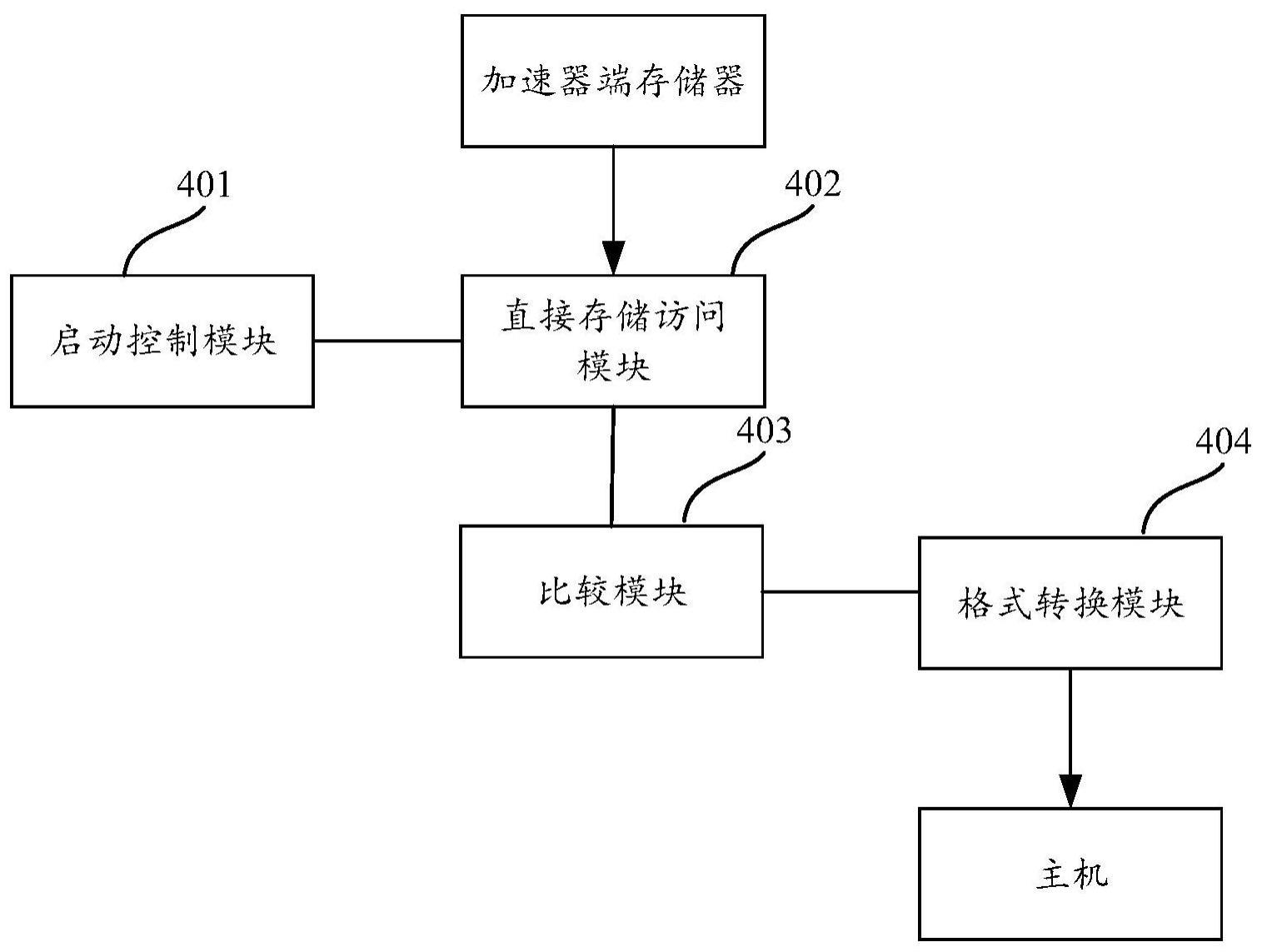

4、一方面,本发明实施例提供一种用于目标检测的后处理加速装置,所述装置包括:

5、启动控制模块,用于接收主机发送的启动信号,并在接收到所述启动信号后,将所述主机设置的配置参数发送给直接存储访问模块;

6、所述直接存储访问模块,用于根据所述配置参数进行寻址,向加速器端存储器发送读数据请求,并将每个地址对应的坐标信息进行缓存,与读返回的数据一一对应作为框数据输出给比较模块;

7、所述比较模块,用于对一个锚框中的数据进行筛选,得到有效框数据,一个锚框中包括多个所述框数据;

8、格式转换模块,用于对所述有效框数据进行格式转换,并将格式转换后的数据传送给所述主机。

9、可选地,所述启动控制模块中设置有启动寄存器和参数寄存器;所述启动寄存器,用于写入所述启动信号;所述参数寄存器,用于写入所述配置参数。

10、可选地,所述配置参数包括:特征图参数及锚框参数。

11、可选地,所述比较模块并行输入多路框数据。

12、可选地,所述比较模块包括:一个或多个二分比较器、以及判断单元;所述二分比较器,用于对本轮并行输入的多路框数据进行比较,得到比较结果;所述判断单元,用于根据所述比较结果确定所述框数据是否为背景框数据,如果否,则将所述框数据作为有效框数据输出给所述格式转换模块。

13、可选地,每路框数据具有独立的使能位。

14、可选地,所述比较模块还包括:缓存单元,用于保存上一轮得到的比较结果;记忆比较单元,用于对本轮得到的比较结果与所述缓存单元保存的上一轮得到的比较结果进行比较,得到最终比较结果。

15、另一方面,本发明实施例还提供一种用于目标检测的后处理加速方法,所述方法包括:

16、接收到主机发送的启动信号后,根据所述主机设置的配置参数进行寻址,并将每个地址对应的坐标信息进行缓存;

17、通过读取所述加速器端存储器获取与所述地址对应的数据,并将缓存的地址与所述数据一一对应作为框数据;

18、对一个锚框中的数据进行筛选,得到有效框数据,一个锚框中包括多个所述框数据;

19、对所述有效框数据进行格式转换,并将格式转换后的数据传送给所述主机。

20、可选地,所述方法还包括:通过启动寄存器接收所述启动信号;通过参数寄存器获取所述配置参数。

21、可选地,所述对一个锚框中的数据进行筛选,得到有效框数据包括:

22、利用多个二分比较器对本轮一个锚框中的多路框数据同时进行比较,得到比较结果;

23、根据所述比较结果确定所述框数据是否为背景框数据,如果否,则将所述框数据作为有效框数据。

24、可选地,每路框数据具有独立的使能位。

25、可选地,所述对一个锚框中的数据进行筛选,得到有效框数据还包括:

26、缓存上一轮得到的比较结果;

27、对本轮得到的比较结果与缓存的上一轮得到的比较结果进行比较,得到最终比较结果。

28、另一方面,本发明实施例还提供一种数据处理系统,所述系统包括:主机、加速器、cpu、以及如前面所述的用于目标检测的后处理加速装置;

29、所述主机,用于向所述目标检测的后处理加速装置发送启动信号,并设置配置参数;

30、所述用于目标检测的后处理加速装置,用于接收所述主机发送的启动信号,并在接收到所述启动信号后,

31、根据所述主机设置的配置参数进行寻址,从所述加速器端存储器获取数据,并对所述数据进行筛选,向所述主机输出特定格式的有效框数据;

32、所述主机,还用于调用所述cpu对所述有效框数据进行目标检测。

33、另一方面,本发明实施例还提供一种芯片,包括如前面所述的用于目标检测的后处理加速装置。

34、另一方面,本发明实施例还提供一种计算机可读存储介质,所述计算机可读存储介质为非易失性存储介质或非瞬态存储介质,其上存储有计算机程序,所述计算机程序被处理器运行时使得上述方法被执行。

35、另一方面,本发明实施例还提供一种用于目标检测的后处理加速装置,包括存储器和处理器,所述存储器上存储有可在所述处理器上处理的源数据,所述处理器处理源数据时使得上述被执行。

36、本发明实施例提供的用于目标检测的后处理加速装置及方法,在主机需要对存储在加速器端存储器中的数据进行后续处理时,不同于现有技术从加速器端存储器中读取数据后直接调用cpu去进行后处理,而是先通过硬件完成大部分无效数据的筛选,得到有效框数据,并将有效框数据的位置坐标信息输出,从而可使cpu处理数据量大大减少,大大减少后处理的时间,使ssd类型后处理的网络检测速度显著提高。而且,由于从加速器存储器传输到主机存储器的数据大大减少,因而有效节省了接口带宽。

37、相应地,本发明实施例提供的数据处理系统,可以大大提高数据处理效率,节省处理时间。

- 还没有人留言评论。精彩留言会获得点赞!