预测存储设备的可靠性信息的方法和操作存储设备的方法与流程

预测存储设备的可靠性信息的方法和操作存储设备的方法

1.相关申请的交叉引用

2.本技术要求于2021年2月5日在韩国知识产权局(kipio)提交的韩国专利申请no.10-2021-0016498的优先权,该韩国专利申请的公开内容通过引用整体合并于此。

技术领域

3.本公开总体上涉及半导体集成电路,并且更具体地,涉及预测存储设备的可靠性信息的方法和操作存储设备的方法。

背景技术:

4.存储设备可以被分类为包括易失性存储器的易失性存储设备或包括非易失性存储器的非易失性存储设备。该分类可以基于在电力被切断或撤销时存储在存储设备中的数据是否丢失。易失性存储器可以更快地读取和写入,然而,当电力被切断或撤销时,存储在易失性存储器中的数据丢失。相比之下,当电力被切断或撤销时,存储在非易失性存储器中的数据被保持。因此,非易失性存储器可以用于存储稍后在所供应的电力被切断或撤销时可以被获取的持久数据。随着非易失性存储器的广泛应用,使用机器学习模型预测存储设备的可靠性信息的各种方法已经被研究和正在研究中。然而,在预测存储设备的可靠性信息时,如果不考虑包括在存储设备中的非易失性存储器的劣化程度,则根据预测的结果数据的可靠性会降低。

技术实现要素:

5.一些示例实施例可以提供用于能够预测包括在存储设备中的非易失性存储器的可靠性信息的存储设备的方法。

6.根据一些示例实施例,在预测包括多个非易失性存储器的存储设备的可靠性的方法中,可以通过选择多个机器学习模型中的一者作为最佳机器学习模型来输出模型请求信号,其中,所述多个机器学习模型中的每一者被配置为生成与所述多个非易失性存储器相关的可靠性信息,并且所述的选择多个机器学习模型中的一者基于劣化特性信息和劣化阶段信息,所述劣化特性信息通过累计与所述多个非易失性存储器相关的劣化信息被获得,所述劣化阶段信息表示所述多个非易失性存储器的劣化程度。基于所述模型请求信号来接收所述最佳机器学习模型的参数。基于所述劣化特性信息和所述参数来生成所述可靠性信息。

7.根据示例实施例,在操作包括多个非易失性存储器的存储设备的方法中,所述存储设备的可靠性信息被预测。基于预测所述可靠性信息的结果对所述存储设备执行读取操作。在预测所述存储设备的可靠性信息中,通过选择多个机器学习模型中的一者作为最佳机器学习模型来输出模型请求信号,其中,所述多个机器学习模型中的每一者被配置为生成与所述多个非易失性存储器相关的可靠性信息,并且所述的选择多个机器学习模型中的一者基于劣化特性信息和劣化阶段信息,所述劣化特性信息通过累计与所述多个非易失性

存储器相关的劣化信息被获得,所述劣化阶段信息表示所述多个非易失性存储器的劣化程度。基于所述模型请求信号来接收所述最佳机器学习模型的参数。基于所述劣化特性信息和所述参数来生成所述可靠性信息。

8.根据示例实施例,在预测包括多个非易失性存储器的存储设备的可靠性的方法中,劣化特性信息被收集。通过累计所述多个非易失性存储器的劣化来获得所述劣化特性信息。基于所述劣化特性信息来生成劣化阶段信息。所述劣化阶段信息将所述多个非易失性存储器的劣化程度表示为多个劣化阶段。基于所述劣化特性信息和所述劣化阶段信息,选择多个机器学习模型中的一者作为最佳机器学习模型。通过基于所述劣化特性信息和所述劣化阶段信息选择所述多个机器学习模型中的一者作为所述最佳机器学习模型来输出模型请求信号。所述模型请求信号对应于所述最佳机器学习模型。所述多个机器学习模型用于生成与所述多个非易失性存储器相关的可靠性信息。通过累计所述多个非易失性存储器的劣化来获得所述劣化特性信息。所述劣化阶段信息表示所述多个非易失性存储器的劣化程度。基于所述模型请求信号来接收所述最佳机器学习模型的参数。基于所述劣化特性信息和所述参数来生成所述可靠性信息。当所述劣化阶段信息对应于早期劣化阶段时,从所述多个机器学习模型当中选择第一机器学习模型作为所述最佳机器学习模型,以及当所述劣化阶段信息对应于继所述早期劣化阶段之后的中期劣化阶段时,从所述多个机器学习模型当中选择不同于所述第一机器学习模型的第二机器学习模型作为所述最佳机器学习模型。

9.如上所述,在预测存储设备的可靠性信息的方法中,可以基于劣化特性信息和劣化阶段信息来输出模型请求信号。可以通过基于模型请求信号自适应选择最佳机器学习模型来预测非易失性存储器的可靠性信息,其中,最佳机器学习模型是从多个机器学习模型中选择的。本文中描述的其他示例实施例中的预测存储设备的可靠性信息的方法可以通过在考虑非易失性存储器的劣化程度的情况下自适应读取最佳机器学习模型的参数来更有效地预测非易失性存储器的可靠性信息。

附图说明

10.根据下面结合附图进行的详细描述,将更清楚理解本公开的示例实施例。

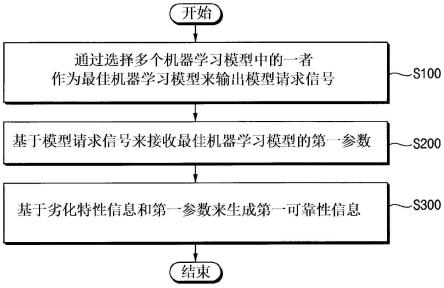

11.图1是示出根据一些示例实施例的预测存储设备的可靠性信息的方法的流程图。

12.图2是示出根据一些示例实施例的存储设备和包括存储设备的存储系统(storage system)的框图。

13.图3是示出包括在图2中的存储设备中的存储控制器的示例的框图。

14.图4是示出包括在图2中的存储设备中的非易失性存储器的示例的框图。

15.图5是示出根据一些示例实施例的非易失性存储器和包括非易失性存储器的存储器系统(memory system)的框图。

16.图6是示出图1中的输出模型请求信号的示例的流程图。

17.图7是示出图6中的收集劣化特性信息的示例的流程图。

18.图8、图9和图10是用于描述图6中的收集劣化特性信息的处理的示图。

19.图11是示出图6中的生成劣化阶段信息的示例的流程图。

20.图12是示出表示劣化特性信息与多个劣化阶段之间的关系的查找表的示例的示

图。

21.图13是示出图1中的输出模型请求信号的示例的流程图。

22.图14是示出通过根据多个模型评价标准评价多个机器学习模型而获得的评价结果的示例的示图。

23.图15是用于描述将包括在多个机器学习模型中的多个参数存储在包括在存储设备中的多个易失性存储器的不同区域中的处理的示图。

24.图16是示出图1中的接收最佳机器学习模型的第一参数的示例的流程图。

25.图17和图18是用于描述根据一些示例实施例的包括在存储设备中的非易失性存储器的阈值电压和读取电压的示图。

26.图19、图20和图21是用于描述根据一些示例实施例的作为用于预测存储设备的可靠性信息的多个机器学习模型的示例的人工神经网络的示图。

27.图22是示出根据一些示例实施例的操作存储设备的方法的流程图。

28.图23是根据一些示例实施例的存储设备和存储系统的框图。

具体实施方式

29.下文中,将参照附图更充分地描述各种示例实施例,在附图中示出了一些示例实施例。在附图中,相似的标号始终是指相似的元件。可以省略重复描述。

30.图1是示出根据一些示例实施例的预测存储设备的可靠性信息的方法的流程图。

31.参照图1,预测存储设备的可靠性信息的方法可以由配置为控制多个非易失性存储器和缓冲存储器的存储控制器执行。将参照图2至图5描述包括存储控制器、多个非易失性存储器和缓冲存储器的存储设备的配置。

32.在预测可靠性信息的方法中,可以通过选择多个机器学习模型中的一者作为最佳机器学习模型来输出模型请求信号,其中,所述的选择多个机器学习模型中的一者基于劣化特性信息和劣化阶段信息(s100)。

33.在一些实施例中,模型请求信号可以对应于最佳机器学习模型。多个机器学习模型可以用于生成与多个非易失性存储器相关的第一可靠性信息。可以通过累计多个非易失性存储器的劣化来获得劣化特性信息。劣化阶段信息可以表示多个非易失性存储器的劣化程度。

34.在一些实施例中,劣化特性信息可以包括直接劣化信息和间接劣化信息。例如,直接劣化信息可以包括多个非易失性存储器的编程/擦除(p/e)周期、读取计数和/或保持时间。间接劣化信息可以包括多个非易失性存储器的导通单元(on-cell)的数目和错误位的数目。将参照图8描述直接劣化信息和间接劣化信息。

35.在一些实施例中,劣化阶段信息可以将多个非易失性存储器的劣化程度表示为多个劣化阶段。在这种情况下,多个劣化阶段可以表示多个非易失性存储器对应于早期劣化阶段、中期劣化阶段和晚期劣化阶段中的一者,但这仅仅是示例。将参照图12描述劣化阶段信息。

36.在一些实施例中,多个机器学习模型可以用于生成与多个非易失性存储器相关的第一可靠性信息。可以基于相同的训练数据集、相同的验证数据集和相同的测试数据集来训练多个机器学习模型,以生成与多个非易失性存储器相关的各种可靠性信息。

37.可以选择多个机器学习模型中的一者作为最佳机器学习模型。在这种情况下,可以将多个机器学习模型存储在单独的易失性存储器中,并且可以基于模型请求信号从易失性存储器中获取最佳机器学习模型的多个参数。

38.在一些实施例中,多个机器学习模型可以包括多个参数,并且包括在多个机器学习模型中的多个参数的大小或数目可以彼此不同。多个机器学习模型可以基于与多个机器学习模型中的每一者对应的参数的大小或数目进行分类,并且多个机器学习模型中的每一者的参数可以基于分类的结果存储在多个易失性存储器的不同区域中。将参照图15和图16描述多个机器学习模型和最佳机器学习模型。

39.可以基于模型请求信号来接收最佳机器学习模型的第一参数(s200)。

40.在一些实施例中,最佳机器学习模型可以作为从多个机器学习模型当中选择的机器学习模型存储在一个易失性存储器中。

41.可以基于劣化特性信息和第一参数来生成第一可靠性信息(s300)。

42.在一些实施例中,可以基于最佳机器学习模型来生成第一可靠性信息。

43.在一些实施例中,劣化特性信息可以作为最佳机器学习模型的输入数据输入,并且第一参数可以配置描述最佳机器学习模型的各种参数。

44.在根据示例实施例的预测存储设备的可靠性信息的方法中,可以执行图1的操作s100、s200和s300,以更有效地预测包括在存储设备中的非易失性存储器的可靠性信息。预测存储设备的可靠性信息的方法基于劣化特性信息和劣化阶段信息来输出模型请求信号,并基于模型请求信号来自适应选择作为多个机器学习模型中的一者的最佳机器学习模型,因此可以更有效地预测非易失性存储器的可靠性信息。即,预测存储设备的可靠性信息的方法可以通过在考虑非易失性存储器的劣化程度的情况下自适应获取(retrieve)最佳机器学习模型的参数来更有效地预测非易失性存储器的可靠性信息。

45.图2是示出根据示例实施例的存储设备和包括存储设备的存储系统的框图。

46.参照图2,存储系统100可以包括主机设备200和存储设备300。主机设备200可以包括主机处理器210和主机存储器220。存储设备300可以包括存储控制器310、多个非易失性存储器320a、320b和320c和缓冲存储器330。

47.主机设备200可以控制存储系统100的总体操作,并且主机处理器210可以控制主机设备200的操作。

48.在一些实施例中,主机处理器210可以执行操作系统(os)。例如,os可以包括用于管理文件的文件系统以及用于在操作系统级控制包括存储设备300的外围设备的设备驱动器。例如,主机处理器210可以包括各种处理单元中的至少一者,例如,中央处理单元(cpu)等。

49.主机存储器220可以存储由主机处理器210执行和/或处理的指令和/或数据。例如,主机存储器220可以包括各种易失性存储器中的至少一者,例如,动态随机存取存储器(dram)等。

50.存储设备300可以由主机设备200访问,并且存储控制器310可以控制存储设备300的操作。

51.在一些实施例中,存储控制器310可以基于从主机设备200接收的请求和数据来控制多个非易失性存储器320a、320b和320c的操作。

52.根据一些示例实施例,存储控制器310可以包括用于预测存储设备300的可靠性信息的可靠性信息预测器312。可靠性信息预测器312可以执行以上参照图1描述的操作s100、s200和s300。

53.缓冲存储器330可以存储由存储控制器310执行和处理的命令和数据,并可以临时存储多个非易失性存储器320a、320b和320c中存储的或者将要存储的数据。

54.在一些实施例中,存储控制器310可以包括紧耦合存储器(tcm)314和第一静态随机存取存储器(sram)(sram1)316,并且缓冲存储器330可以包括第二sram(sram2)332和动态随机存取存储器(dram)334。

55.在一些实施例中,以上参照图1描述的多个机器学习模型350可以基于卷积神经网络(cnn)、递归神经网络(rnn)、支持向量机(svm)、线性回归、逻辑回归、朴素贝叶斯分类、随机森林、决策树和/或k-最近邻(knn)算法中的至少一种,本公开不限于此。

56.在一些实施例中,多个机器学习模型350的多个参数可以存储在tcm314、第一sram 316、第二sram 332和dram 334中。在一些实施例中,存储在tcm 314中的机器学习模型的处理速度可以高于存储在第一sram316、第二sram 332和dram 334中的一者中的机器学习模型的处理速度。存储在dram 334中的机器学习模型的准确度可以高于存储在tcm 314、第一sram 316和第二sram 332中的一者中的机器学习模型的准确度。

57.在一些实施例中,包括在多个机器学习模型350中的多个参数的大小可以彼此不同,并且多个机器学习模型350可以基于多个参数的大小被分类为第一机器学习模型、第二机器学习模型和第三机器学习模型。在一些实施例中,第一机器学习模型可以存储在tcm 314中,第二机器学习模型可以存储在第一sram 316和第二sram 332中的一者中,并且第三机器学习模型可以存储在dram 334中。

58.在一些实施例中,tcm 314、第一sram 316、第二sram 332和dram334可以被称为“学习模型存储存储器”。

59.在一些实施例中,多个非易失性存储器320a、320b和320c可以存储多个数据。例如,多个非易失性存储器320a、320b和320c可以存储元数据、其他用户数据等。

60.在一些实施例中,多个非易失性存储器320a、320b和320c中的每一者可以包括nand闪存。在其他示例实施例中,多个非易失性存储器320a、320b和320c中的每一者可以包括电可擦除可编程只读存储器(eeprom)、相变随机存取存储器(pram)、电阻式随机存取存储器(rram)、纳米浮栅存储器(nfgm)、聚合物随机存取存储器(poram)、磁随机存取存储器(mram)、铁电随机存取存储器(fram)等中的一种。

61.在一些示例实施例中,存储设备300可以是通用闪存(ufs)。在其他示例实施例中,存储设备300可以是固态驱动器(ssd)、多媒体卡(mmc)、嵌入式多媒体卡(emmc)等。在其他示例实施例中,存储设备300可以是安全数字(sd)卡、微型sd卡、记忆棒、芯片卡、通用串行总线(usb)卡、智能卡、紧凑型闪存(cf)卡等中的一种。

62.在一些示例实施例中,存储设备300可以经由块可访问接口连接到主机设备200,块可访问接口可以包括例如ufs、emmc、串行高级技术附件(sata)总线、快速非易失性存储器(nvme)总线、串行附加scsi(sas)总线等。存储设备300可以使用与多个非易失性存储器320a、320b和320c的访问大小对应的块可访问地址空间来向主机设备200提供块可访问接口,由此允许以存储块大小为单元(memory-block-sized units)对存储在多个非易失性存

储器320a、320b和320c中的数据进行访问。

63.在一些示例实施例中,存储系统100可以是诸如个人计算机(pc)、服务器计算机、数据中心、工作站、数字电视、机顶盒、导航系统等的任何计算系统。在其他示例实施例中,存储系统100可以是任何移动系统,诸如,移动电话、智能电话、平板计算机、膝上型计算机、个人数字助理(pda)、便携式多媒体播放器(pmp)、数字相机、便携式游戏控制台、音乐播放器、摄像机、视频播放器、导航设备、可穿戴设备、物联网(iot)设备、万物互联(ioe)设备、电子书阅读器、虚拟现实(vr)设备、增强现实(ar)设备、机器人设备、无人机等。

64.图3是示出诸如包括在图2中的存储设备中的存储控制器310的存储控制器的示例的框图。

65.参照图3,存储控制器400可以包括处理器410、tcm 412、纠错码(ecc)引擎420、可靠性信息预测器430、主机接口(i/f)440、缓冲存储器接口450和存储器接口460。

66.处理器410可以响应于通过主机接口440从主机设备(例如,图2中的200)接收的请求来控制存储控制器400的总体操作。

67.在一些实施例中,处理器410可以控制存储设备(例如,图2中的300)的操作,并可以通过采用配置为驱动存储设备300的固件来控制每个部件。

68.在一些实施例中,处理器410可以包括tcm 412。tcm 412可以对应于以上参照图2描述的tcm 314,并且tcm 412可以用作能够高速操作的高速缓存存储器。在这种情况下,当用作高速缓存存储器的单独的sram(例如,图2中的316)被提供时,tcm 412可以通过专用的tcm接口(未示出)与处理器410通信,该专用的tcm接口不同于用于执行与sram的通信的接口。

69.ecc引擎420可以被配置为执行纠错,并可以使用诸如bose-chaudhuri-hocquenghem(bch)码、低密度奇偶校验(ldpc)码、turbo码、reed-solomon码、卷积码、递归系统码(rsc)、网格编码调制(tcm)、块编码调制(bcm)或其他纠错码的编码调制,执行ecc编码和/或ecc解码。

70.可靠性信息预测器430可以执行以上参照图1描述的操作s100、s200和s300。

71.在一些实施例中,可靠性信息预测器430可以包括劣化特性信息收集电路(dccc)432、劣化阶段信息生成电路dsic 434、机器学习模型选择电路mlsc 436和可靠性信息生成电路(ric)438,并可以使用包括在可靠性信息预测器430中的部件432、434、436和438执行以上参照图1描述的操作s100、s200和s300。

72.主机接口440可以提供主机设备200与存储设备300之间的物理连接。主机接口440可以被配置为基于主机设备200的总线格式来提供与存储设备300的接口连接。

73.在一些实施例中,主机设备200的总线格式可以是scsi或sas。在其他示例实施例中,主机设备200的总线格式可以是usb、快速外围组件互连(pcie)、ata、pata、sata、nvme等。

74.存储器接口460可以与非易失性存储器(例如,图2中的320a、320b和320c)交换数据。存储器接口460可以向非易失性存储器320a、320b和320c发送数据,并可以接收从非易失性存储器320a、320b和320c读取的数据。例如,存储器接口460可以被实现为符合诸如toggle或onfi的标准协议。

75.尽管未示出,但存储控制器400还可以包括aes引擎。aes引擎可以使用对称密钥算

法对输入存储控制器400的数据执行加密操作和解密操作中的至少一者。尽管未详细示出,但aes引擎可以包括加密模块和解密模块。在一些实施例中,加密模块和解密模块可以被实现为单独的模块,或者可以被实现为单个模块。

76.图4是示出包括在图2中的存储设备中的非易失性存储器的示例的框图。

77.参照图4,非易失性存储器500包括存储单元阵列510、地址译码器520、页缓冲器电路530、数据i/o电路540、电压发生器550和控制电路560。

78.存储单元阵列510经由多条串选择线ssl、多条字线wl和多条接地选择线gsl连接到地址译码器520。存储单元阵列510经由多条位线bl连接到页缓冲器电路530。存储单元阵列510可以包括连接到多条字线wl和多条位线bl的多个存储单元(例如,多个非易失性存储单元)。存储单元阵列510可以被划分为均可以包括存储单元的多个存储块blk1、blk2、

…

、blkz。另外,多个存储块blk1、blk2、

…

、blkz中的每一者可以被划分为多个页。

79.在一些示例实施例中,包括在存储单元阵列510中的多个存储单元可以布置为二维(2d)阵列结构或三维(3d)垂直阵列结构。3d垂直阵列结构可以包括垂直定向使得至少一个存储单元位于另一存储单元上方的垂直单元串。至少一个存储单元可以包括电荷俘获层。通过引用整体合并于此的以下文献描述了用于包括3d垂直阵列结构的存储单元阵列的合适配置,在该配置中,三维存储阵列被配置为多个层级,字线和/或位线在各层级之间共享:美国专利no.7,679,133;no.8,553,466;no.8,654,587;no.8,559,235和us专利公开no.2011/0233648。

80.控制电路560可以被配置为从外部或外部源(例如,从图2中的存储控制器310)接收命令cmd和地址addr,并被配置为基于命令cmd和地址addr来控制非易失性存储器500的擦除、编程和读取操作。擦除操作可以包括执行一系列擦除循环,并且编程操作可以包括执行一系列编程循环。每个编程循环可以包括编程操作和编程验证操作。每个擦除循环可以包括擦除操作和擦除验证操作。读取操作可以包括正常读取操作和数据恢复读取操作。

81.例如,基于命令cmd,控制电路560可以生成用于控制电压发生器550的控制信号con,并可以生成用于控制页缓冲器电路530的控制信号pbc,并且可以基于地址addr来生成行地址r_addr和列地址c_addr。控制电路560可以将行地址r_addr提供给地址译码器520,并可以将列地址c_addr提供给数据i/o电路540。

82.地址译码器520可以经由多条串选择线ssl、多条字线wl和多条接地选择线gsl连接到存储单元阵列510。

83.在数据擦除/写入/读取操作中,基于行地址r_addr,地址译码器520可以确定或选择多条字线wl中的至少一条字线作为选定字线,并可以确定或指定多条字线wl中的除了选定字线外的其余或剩余字线作为未选字线。

84.此外,在数据擦除/写入/读取操作中,基于行地址r_addr,地址译码器520可以确定或选择多条串选择线ssl中的至少一条串选择线作为选定串选择线,并可以确定或指定多条串选择线ssl中的除了选定串选择线外的其余或剩余串选择线作为未选串选择线。

85.另外,在数据擦除/写入/读取操作中,基于行地址r_addr,地址译码器520可以确定或选择多条接地选择线gsl中的至少一条接地选择线作为选定接地选择线,并可以确定或指定多条接地选择线gsl中的除了选定接地选择线外的其余或剩余接地选择线作为未选接地选择线。

86.电压发生器550可以被配置为基于功率pwr和控制信号con来生成非易失性存储器500的操作所需的电压vs。电压vs可以经由地址译码器520施加到多条串选择线ssl、多条字线wl和多条接地选择线gsl。另外,电压发生器550可以基于电力pwr和控制信号con来生成数据擦除操作所需的擦除电压vers。擦除电压vers可以直接或经由位线bl施加到存储单元阵列510。

87.在擦除操作期间,电压发生器550可以将擦除电压vers施加到存储块(例如,选定存储块)的公共源极线和/或位线bl,并可以经由地址译码器520将擦除许可电压(例如,接地电压)施加到存储块的所有字线或字线的一部分。另外,在擦除验证操作期间,电压发生器550可以将擦除验证电压同时施加到存储块的所有字线或者逐个地顺序施加到字线。

88.在编程操作期间,电压发生器550经由地址译码器520可以将编程电压施加到选定字线并且可以将编程通过电压施加到未选字线。另外,在编程验证操作期间,电压发生器550经由地址译码器520可以将编程验证电压施加到选定字线并且可以将验证通过电压施加到未选字线。

89.另外,在正常读取操作期间,电压发生器550经由地址译码器520可以将读取电压施加到选定字线并且可以将读取通过电压施加到未选字线。在数据恢复读取操作期间,电压发生器550经由地址译码器520可以将读取电压施加到与选定字线相邻的字线并且可以将恢复读取电压施加到选定字线。

90.页缓冲器电路530可以经由多条位线bl连接到存储单元阵列510。页缓冲器电路530可以包括多个页缓冲器。在一些示例实施例中,每个页缓冲器可以连接到一条位线。在其他示例实施例中,每个页缓冲器可以连接到两条或更多条位线。

91.页缓冲器电路530可以存储要编程到存储单元阵列510中的数据dat和/或可以读取从存储单元阵列510感测到的数据dat。换句话说,页缓冲器电路530可以根据非易失性存储器500的操作模式作为写入驱动器和/或作为读出放大器操作。

92.数据i/o电路540可以经由数据线dl连接到页缓冲器电路530。数据i/o电路540基于列地址c_addr可以经由页缓冲器电路530将来自非易失性存储器500的外部源的数据dat提供到存储单元阵列510或者可以将来自存储单元阵列510的数据dat提供到非易失性存储器500的外部目的地。在一些实施例中,外部源和外部目的地可以是相同的位置或设备。

93.尽管根据一些示例实施例的非易失性存储器是基于nand闪存描述的,但根据示例实施例的非易失性存储器可以是任何非易失性存储器,例如,相位随机存取存储器(pram)、电阻式随机存取存储器(rram)、纳米浮栅存储器(nfgm)、聚合物随机存取存储器(poram)、磁随机存取存储器(mram)、铁电随机存取存储器(fram)、晶闸管随机存取存储器(tram)等。

94.图5是示出根据一些示例实施例的非易失性存储器和包括非易失性存储器的存储器系统的框图。

95.参照图5,存储器系统600可以包括存储器件610和存储器控制器(memory controller)620。存储器系统600可以支持多个通道ch1、ch2、

…

、chm,并且存储器件610可以通过多个通道ch1至chm连接到存储器控制器620。例如,存储器系统600可以被实现为诸如通用闪存(ufs)、固态驱动器(ssd)等的存储设备。

96.存储器件610可以包括多个非易失性存储器nvm11、nvm12、

…

、nvm1n、nvm21、nvm22、

…

、nvm2n、nvmm1、nvmm2、

…

、nvmmn。例如,非易失性存储器nvm11至nvmmn可以对应于

图2中的非易失性存储器320a、320b和320c。非易失性存储器nvm11至nvmmn中的每一者可以通过与其对应的路(way)连接到多个通道ch1至chm中的一者。例如,非易失性存储器nvm11至nvm1n可以通过路w11、w12、

…

、w1n连接到第一通道ch1,非易失性存储器nvm21至nvm2n可以通过路w21、w22、

…

、w2n连接到第二通道ch2,并且非易失性存储器nvmm1至nvmmn可以通过路wm1、wm2、

…

、wmmn连接到第m通道chm。在一些示例实施例中,非易失性存储器nvm11至nvmmn中的每一者可以被实现为可以根据来自存储器控制器620的单独命令操作的任意存储器单元(memory unit)。例如,非易失性存储器nvm11至nvmmn中的每一者可以被实现为芯片或裸片,但本公开不限于此。

97.存储器控制器620可以通过多个通道ch1至chm将信号发送到存储器件610以及从存储器件610接收信号。例如,存储器控制器620可以对应于图2中的存储控制器310。例如,存储器控制器620可以通过通道ch1至chm将命令cmda、cmdb、

…

、cmdm、地址addra、addrb、

…

、addrm和数据dataa、datab、

…

、datam发送到存储器件610,或者可以从存储器件610接收数据dataa至datam。

98.存储器控制器620可以通过使用通道ch1至chm中的对应通道来选择与通道ch1至chm中的每一者连接的非易失性存储器nvm11至nvmmn中的一者,并可以将信号发送到选择的非易失性存储器以及从选择的非易失性存储器接收信号。例如,存储器控制器620可以从连接到第一通道ch1的非易失性存储器nvm11至nvm1n当中选择非易失性存储器nvm11。存储器控制器620可以通过第一通道ch1将命令cmda、地址addra和数据dataa发送到选择的非易失性存储器nvm11,或者可以从选择的非易失性存储器nvm11接收数据dataa。

99.存储器控制器620可以通过不同的通道并行地将信号发送到存储器件610以及从存储器件610接收信号。例如,存储器控制器620可以通过第二通道ch2将命令cmdb发送到存储器件610,同时通过第一通道ch1将命令cmda发送到存储器件610。例如,存储器控制器620可以通过第二通道ch2从存储器件610接收数据datab,同时通过第一通道ch1从存储器件610接收数据dataa。

100.存储器控制器620可以控制存储器件610的总体操作。存储器控制器620可以将信号发送到通道ch1至chm,并可以控制连接到通道ch1至chm的非易失性存储器nvm11至nvmmn中的每一者。例如,存储器控制器620可以将命令cmda和地址addra发送到第一通道ch1,并可以控制从非易失性存储器nvm11到nvm1n当中选择的一者。

101.非易失性存储器nvm11至nvmmn中的每一者可以在存储器控制器620的控制下操作。例如,非易失性存储器nvm11可以基于通过第一通道ch1从存储器控制器620提供的命令cmda、地址addra和数据dataa对数据dataa进行编程。例如,非易失性存储器nvm21可以基于通过第二通道ch2从存储器控制器620提供的命令cmdb和地址addrb来读取数据datab,并可以通过第二通道ch2将读取的数据datab发送到存储器控制器620。

102.尽管图5示出了存储器件610通过m个信道与存储器控制器620通信并包括对应于每个通道的n个非易失性存储器的示例,但本公开不限于此,通道的数目和连接到一个通道的非易失性存储器的数目可以根据示例实施例进行各种改变。

103.图6是示出图1中的输出模型请求信号的示例的流程图。图7是示出图6中的收集劣化特性信息的示例的流程图。

104.参照图6,在输出模型请求信号时,可以收集劣化特性信息(s110)。可以基于劣化

特性信息来生成劣化阶段信息(s130)。在一些实施例中,劣化阶段信息可以将多个非易失性存储器的劣化程度表示为多个劣化阶段。

105.参照图7,在收集劣化特性信息中,基于由包括在存储设备中的存储控制器发出的命令中的至少一个命令来生成劣化特性信息(s111)。基于命令中的至少一个命令来更新劣化特性信息(s113)。

106.在一些实施例中,劣化特性信息可以包括直接劣化信息和间接劣化信息。下文中,将描述劣化特性信息。

107.图8、图9和图10是用于描述图6中的收集劣化特性信息的处理的示图。

108.在图8中,作为示例,示出了从存储控制器发出的命令、p/e周期、读取计数、保持时间、多个非易失性存储器的导通单元的数目和错误位的数目。

109.在一些实施例中,可以通过对p/e周期、读取计数、导通单元的数目和错误位的数目进行累计计数来生成p/e周期信息、读取计数信息、保持时间信息、关于导通单元的数目的信息和关于错误位的数目的信息。

110.在一些实施例中,p/e周期、读取计数和保持时间可以被包括在直接劣化信息中,并且导通单元的数目和错误位的数目可以被包括在间接劣化信息中。

111.参照图8,为了便于描述,假设顺序地发出编程命令pgm、第一读取命令rd1、第二读取命令rd2、擦除命令ers、保持时间生成命令rtic以及导通单元计数生成命令ocic。

112.在一些实施例中,可以基于编程命令pgm和擦除命令ers对p/e周期的数目进行累计计数。例如,每当发出编程命令pgm和对应于编程命令pgm的擦除命令时,编程/擦除周期的数目可以累计地增加。在这种情况下,可以根据编程命令pgm生成或读取用于存储p/e周期的数目的第一变量ci1,并且第一变量ci1的值可以基于擦除命令ers增加1或递增。

113.在一些实施例中,可以基于读取命令对读取计数的数目进行累计计数。例如,当发出第一读取命令rd1时,读取计数的数目可以累计地增加,而当发出第二读取命令rd2时,读取计数的数目可以累计地增加。在这种情况下,可以根据第一读取命令rd1和第二读取命令rd2生成或读取用于存储读取计数的第二变量ci2,并且第二变量ci2的值可以基于第一读取命令rd1和第二读取命令rd2增加1或递增。

114.在一些实施例中,可以基于编程命令pgm和保持时间生成命令rtic对保持时间进行累计计数。例如,当发出编程命令pgm时,可以对应于编程命令pgm生成用于存储保持时间的第三变量ci3。当发出保持时间生成命令rtic时,用于存储保持时间的第三变量ci3的值可以增加了从发出编程命令pgm时起直至发出保持时间生成命令rtic的时间。

115.在一些实施例中,可以基于导通单元计数生成命令ocic对导通单元的数目进行累计计数。例如,当发出导通单元计数生成命令ocic时,对包括在多个非易失性存储器中的存储单元当中的导通单元的数目进行计数,并且用于存储导通单元的数目的第四变量ci4的值可以增加了所计数的导通单元的数目。

116.在一些实施例中,可以基于编程命令pgm和读取命令rd1和rd2对错误位的数目进行累计计数。例如,每当发出编程命令pgm、第一读取命令rd1和第二读取命令rd2时,错误位的数目可以累计地增加。在这种情况下,用于存储错误位的数目的第五变量ci5可以被增加根据对分别与编程命令pgm、第一读取命令rd1和第二读取命令rd2对应的数据执行ecc编码或ecc解码的结果的错误位的数目。

117.在一些实施例中,可以基于第一变量ci1至第五变量ci5来生成p/e周期信息、读取计数信息、保持时间信息、关于导通单元的数目的信息和关于错误位的数目的信息。参照图6、图8和图9,在收集劣化特性信息(s110)时,可以基于编程命令pgm和擦除命令ers来更新p/e周期(s121),并且可以基于第一读取命令rd1和第二读取命令rd2来更新读取计数(s123)。可以基于编程命令pgm和保持时间生成命令rtic来更新保持时间(s125),可以基于导通单元计数生成命令ocic来更新导通单元的数目(s127),并且可以基于第一读取命令rd1、第二读取命令rd2和编程命令pgm中的至少一者来更新错误位的数目(s129)。

118.在图10中,作为示例示出了以上参照图2描述的多个非易失性存储器320a、320b和320c中的第一非易失性存储器320a。

119.第一非易失性存储器320a可以包括多个存储块321-1、321-2、321-3和321-4,并且多个存储块321-1、321-2、321-3和321-4可以分别包括多个存储单元323-1、323-2、323-3和323-4。为了便于示出,在图10中仅示出了一些存储块和其中的存储单元。

120.参照图10,可以针对第一非易失性存储器320a生成p/e周期、读取计数、保持时间、导通单元的数目和错误位的数目。在一些实施例中,可以针对多个存储块321-1、321-2、321-3和321-4的全部或一部分生成p/e周期、读取计数、保持时间、导通单元的数目和错误位的数目,而在其他示例实施例中,可以针对多个存储单元323-1、323-2、323-3和323-4的全部或一部分生成读取计数、保持时间、导通单元的数目和错误位的数目。

121.在一些实施例中,劣化特性信息可以存储在多个非易失性存储器320a、320b和320c中或者以上参照图2描述的缓冲存储器330中的dram 334中,但本公开不限于此。

122.图11是示出图6中的生成劣化阶段信息的示例的流程图。图12是示出表示劣化特性信息与多个劣化阶段之间的关系的查找表的示例的示图。

123.参照图11,可以获取劣化特性信息(s131),并且获取表示劣化特性信息与多个劣化阶段之间的关系的查找表(s133)。可以基于劣化特性信息和查找表来生成劣化阶段信息(s135)。

124.在图12中,示出了劣化特性信息dci_info和劣化阶段信息dsi_info。参照图12,可以通过基于预定系数对以上参照图8、图9和图10描述的第一变量ci1至第五变量ci5中累计的值进行内插来生成劣化特性信息dci_info。

125.在一些实施例中,可以基于内插结果由第一劣化特性信息dci_info_1至第十劣化特性信息dci_info_10中的一者表示劣化特性信息dci_info,并且第一劣化特性信息dci_info_1至第十劣化特性信息dci_info_10中的一者可以被表示为第一劣化阶段dsi_info_1至第十劣化阶段dsi_info_10中的一者。

126.在一些实施例中,劣化阶段信息可以将多个非易失性存储器的劣化程度表示为多个劣化阶段。例如,第一劣化阶段dsi_info_1可以表示多个非易失性存储器的劣化进展最小的情况,而第十劣化阶段dsi_info_10可以表示多个非易失性存储器的劣化进展最大的情况。本公开不限于此。

127.在一些实施例中,当多个非易失性存储器对应于第一劣化阶段dsi_info_1至第三劣化阶段dsi_info_3中的一者时,可以确定多个非易失性存储器对应于或处于早期劣化阶段。当多个非易失性存储器对应于第四劣化阶段dsi_info_4至第六劣化阶段dsi_info_6中的一者时,可以确定多个非易失性存储器对应于或处于中期劣化阶段。当多个非易失性存

储器对应于第七劣化阶段dsi_info_7至第十劣化阶段dsi_info_10中的一者时,可以确定多个非易失性存储器对应于或处于后期劣化阶段。然而,示例实施例不限于此。

128.图13是示出图1中的输出模型请求信号的示例的流程图。图14是示出通过根据多个模型评价标准评价多个机器学习模型而获得的评价结果的示例的示图。图15是用于描述将包括在多个机器学习模型中的多个参数存储在包括在存储设备中的多个易失性存储器的不同区域中的处理的示图。

129.参照图13,在图1中的输出模型请求信号中,可以根据多个模型评价标准评价多个机器学习模型(s141)。

130.在图14中,示出了通过根据多个模型评价标准评价多个机器学习模型mm1至mm10而获得的评价结果。在一些实施例中,多个模型评价标准可以包括处理速度、准确度(accuracy)、混淆矩阵、精确度(precision)、召回率(recall)和f1分数,本公开不限于此。

131.参照图14,可以根据多个模型评价标准中的至少一者来评价多个机器学习模型。

132.在一些实施例中,作为根据处理速度评价多个机器学习模型mm1至mm10的结果,机器学习模型mm1可以被识别为最佳或最理想,并且机器学习模型mm10可以被识别为最差或最不理想。

133.在一些实施例中,作为根据准确度评价多个机器学习模型mm1至mm10的结果,机器学习模型mm10可以被识别为最佳或最理想,并且机器学习模型mm1可以被识别为最差或最不理想。

134.在一些实施例中,作为根据混淆矩阵、精确度、召回率和f1分数评价多个机器学习模型mm1至mm10的结果,可以如图14中所示识别多个机器学习模型mm1至mm10。

135.在一些实施例中,多个模型评价标准可以包括第一模型评价标准至第x模型评价标准,其中,x是大于或等于2的整数。第一模型评价标准至第x模型评价标准中的每一者可以是用于基于多个机器学习模型的处理速度、准确度、混淆矩阵、精确度、召回率和f1分数中的至少一者对多个机器学习模型进行排序的标准。

136.返回参照图13,可以基于根据多个模型评价标准的评价结果,将包括在多个机器学习模型中的多个参数存储在包括在存储设备中的多个易失性存储器的不同区域中(s143)。基于劣化阶段信息来选择多个机器学习模型中的一者(s145)。

137.参照图15,多个机器学习模型mm1至mm10存储在包括在存储设备中的多个易失性存储器710、730和750中。

138.在一些实施例中,多个易失性存储器中的第一易失性存储器710可以对应于图2中的tcm 314。多个易失性存储器中的第二易失性存储器730可以对应于图2中的sram 316和sram 332中的一者。多个易失性存储器中的第三易失性存储器750可以对应于图2中的dram 334。

139.在一些实施例中,具有优异处理速度的一些或第一组机器学习模型(例如,mm1和mm2)可以存储在第一易失性存储器710中,具有次佳处理速度的一些或第二组机器学习模型(例如,mm3至mm5)可以存储在第二易失性存储器730中,并且具有较差处理速度的其余或第三组机器学习模型(例如,mm6至mm10)可以存储在第三易失性存储器750中。存储在第一易失性存储器710中的机器学习模型可以被称为第一机器学习模型,存储在第二易失性存储器730中的机器学习模型可以被称为第二机器学习模型,并且存储在第三易失性存储器

750中的机器学习模型可以被称为第三机器学习模型。在一些实施例中,包括在第一机器学习模型中的多个参数的大小或数目小于包括在第二机器学习模型中的多个参数的大小或数目,并且包括在第二机器学习模型中的多个参数的大小或数目小于包括在第三机器学习模型中的多个参数的大小或数目。

140.在一些实施例中,基于表示为一阶多项式的线性回归、线性svm、浅层决策树(shallow depth decision tree)和由少量层和节点构成的人工神经网络的机器学习模型可以存储在第一易失性存储器710中。基于表示为指数或对数的线性回归、基于径向基函数(rbf)核的svm、深度决策树(deep depth decision tree)和由大量层和节点构成的人工神经网络的机器学习模型可以存储在第三易失性存储器750中。

141.因此,当基于劣化阶段信息确定多个非易失性存储器对应于早期劣化阶段时,可以从多个机器学习模型当中选择第一机器学习模型作为最佳机器学习模型。当基于劣化阶段信息确定多个非易失性存储器对应于中期劣化阶段时,可以从多个机器学习模型当中选择第二机器学习模型作为最佳机器学习模型。当基于劣化阶段信息确定多个非易失性存储器对应于后期劣化阶段时,可以从多个机器学习模型当中选择第三机器学习模型作为最佳机器学习模型。

142.图16是示出图1中的接收最佳机器学习模型的第一参数的示例的流程图。

143.参照图16,在图1中的接收最佳机器学习模型的第一参数中,当第一机器学习模型被选择为最佳机器学习模型时,可以经由tcm接口接收第一参数(s510)。当第二机器学习模型和第三机器学习模型中的一者被选择为最佳机器学习模型时,可以经由缓冲存储器接口接收第一参数(s530)。

144.在一些实施例中,当通过执行操作s510和s530选择机器学习模型作为最佳机器学习模型时,可以从以上参照图15描述的第一易失性存储器710、第二易失性存储器730和第三易失性存储器750中的一者接收第一参数。当第一机器学习模型被选择为最佳机器学习模型时,可以从第一易失性存储器710接收第一参数。当第二机器学习模型被选择为最佳机器学习模型时,可以从第二易失性存储器730接收第一参数。当第三机器学习模型被选择为最佳机器学习模型时,可以从第三易失性存储器750接收第一参数。

145.图17和图18是用于描述根据一些示例实施例的包括在存储设备中的非易失性存储器的阈值电压和读取电压的示图。

146.在图17和图18中,在示例中示出了包括具有三阶单元(tlc,triple level cell)结构的存储单元的非易失性存储器件的阈值电压分布和读取电压。

147.参照图17,包括在非易失性存储器件中的存储单元可以具有擦除状态e和第一编程状态p1至第七编程状态p7中的一者。可以在考虑存储单元的特性的情况下预先确定读取电压vrd1至vrd7。

148.在一些实施例中,可以在存储单元被编程之后,立即基于阈值电压分布来确定读取电压vrd1至vrd7,但在其他示例实施例中,在继存储单元被编程后经过预定时间之后,例如,在存储单元稳定之后,可以基于阈值电压分布来确定读取电压vrd1至vrd7。

149.参照图18,当包括在非易失性存储器件中的存储单元的物理特性由于外部因素而改变时,阈值电压分布可以改变,如图18中所示。例如,在电荷俘获闪存(ctf)存储单元中,可能出现其中存储单元的阈值电压分布随编程时间的流逝而减小的初始验证移位(ivs)现

象。此外,由于在存储单元编程期间突然断电(spo),存储单元的阈值电压分布可以交叠,如图18中所示。当基于读取电压vrd1至vrd7来获取存储在非易失性存储器件中的数据时,读取数据可以包括多个错误。因此,当使用以上参照图1描述的机器学习模型预测非易失性存储器的阈值电压或读取电压时,可以有效地减少可能包括在读取数据中的误差的数目。

150.图19、图20和图21是用于描述根据一些示例实施例的作为用于预测存储设备的可靠性信息的多个机器学习模型的示例的人工神经网络的示图。如上面参照图2所描述的,多个机器学习模型可以包括基于卷积神经网络、递归神经网络、支持向量机(svm)以及诸如线性回归、逻辑回归、朴素贝叶斯分类、随机森林、决策树和k-最近邻(knn)的算法的机器学习模型。

151.参照图19,常见神经网络(例如,ann)可以包括输入层il、多个隐藏层hl1、hl2、

…

、hln和输出层ol。

152.输入层il可以包括i个输入节点x1、x2、

…

、xi,其中,i是自然数。其长度为i的输入数据(例如,向量输入数据)idat可以被输入到输入节点x1、x2、

…

、xi,使得输入数据idat的每个元素被输入到输入节点x1、x2、

…

、xi中的相应输入节点。在一些实施例中,如上面参照图8描述的直接劣化信息和间接劣化信息可以作为输入数据idat被输入。

153.多个隐藏层hl1、hl2、

…

、hln可以包括n个隐藏层,其中,n是自然数,并可以包括多个隐藏节点h

11

、h

12

、h

13

、...、h

1m

、h

21

、h

22

、h

23

、...、h

2m

、h

n1

、h

n2

、h

n3

、...、h

nm

。例如,隐藏层hl1可以包括m个隐藏节点h

11

、h

12

、h

13

、...、h

1m

,隐藏层hl2可以包括m个隐藏节点h

21

、h

22

、h

23

、...、h

2m

,并且隐藏层hln可以包括m个隐藏节点h

n1

、h

n2

、h

n3

、...、h

nm

,其中,m是自然数。

154.输出层ol可以包括j个输出节点y1、y2、...、yj,其中,j是自然数。输出节点y1、y2、...、yj中的每一个输出节点可以对应于待分类的类别中的相应类别。输出层ol可以针对每个类别输出与输入数据idat关联的输出值odat(例如,类别分数或简单(simply)分数)。输出层ol可以被称为全连接层,并且可以指示例如输入数据idat对应于相应类别的概率。

155.图19中示出的神经网络的结构可以由关于节点之间的示出为线的分支(或连接)的信息和未示出的分配给每个分支的加权值来表示。一个层内的节点可以不相互连接,但不同层的节点可以完全或部分相互连接。

156.每个节点可以接收前一节点的输出,可以对接收到的输出执行计算操作、计算或运算,并且可以将计算操作、计算或运算的结果作为输出输出输出到下一节点。例如,节点h

11

可以接收前一节点x1的输出,可以对接收到的前一节点x1的输出执行计算操作、计算或运算,并可以将计算操作、计算或运算的结果作为输出输出到下一节点h

21

。每个节点可以通过将输入应用于特定函数(例如,非线性函数)来计算待输出的值。

157.通常,可以预先设置神经网络的结构,并且使用具有数据属于哪一类别的已知答案的数据来适当地设置节点之间连接的加权值。具有已知答案的数据被称为“训练数据”,并且确定加权值的过程被称为“训练”。神经网络在训练过程中进行“学习”。一组独立可训练的结构和加权值被称为“模型”,并且通过具有确定的加权值的模型预测输入数据属于哪一类别然后输出预测值的过程被称为“测试”过程。

158.图19中示出的常见神经网络可能不适于处理输入数据idat,因为每个节点(例如,节点h

11

)连接到前一层的所有节点(例如,包括在层il中的节点x1、x2、

…

、xi),然后随着输入数据idat的大小增加,加权值的数目急剧增加。因此,已经研究出通过将过滤技术与常见神

经网络相结合实现的卷积神经网络(cnn),使得输入数据idat被cnn有效地训练。

159.参照图20,cnn可以包括多个层conv1、relu1、conv2、relu2、pool1、conv3、relu3、conv4、relu4、pool2、conv5、relu5、conv6、relu6、pool3和fc。这里,conv是卷积层,relu是修正线性单元,pool是池化层,fc是全连接层。

160.与常见神经网络(例如,图19的神经网络)不同,cnn的每一层可以具有宽度、高度和深度三个维度,因此输入到每一层的数据可以是具有宽度、高度和深度三个维度的体数据。例如,图20中的输入数据idat可以具有32*32*3的大小。输入数据idat可以被称为输入体数据或输入激活体。

161.卷积层conv1、conv2、conv3、conv4、conv5和conv6中的每一者可以对输入体数据执行卷积运算。卷积运算表示基于具有加权值的掩模来处理数据并通过将输入值乘以加权值并将所有相乘的值相加来获得输出值的操作。掩模可以被称为过滤器、窗口或内核。

162.特别地,每个卷积层的参数可以包括一组可学习过滤器(filter)。每个过滤器在空间上可以较小(沿着宽度和高度),但可以延伸遍及输入体的整个深度。例如,在前向传递期间,每个过滤器可以遍及(across)输入体的宽度和高度滑动(更确切地,卷积),并且可以在任何位置处计算过滤器的条目和输入之间的点积。当过滤器在输入体的宽度和高度上滑动时,可以生成给出该过滤器在每个空间位置处的响应的二维激活图。结果,可以通过沿着深度维度堆叠这些激活图来生成输出体。例如,如果大小为32*32*3的输入体数据在进行零填充的情况下通过具有四个过滤器的卷积层conv1,则卷积层conv1的输出体数据的大小可以为32*32*12(例如,体数据的深度增加)。

163.relu层relu1、relu2、relu3、relu4、relu5和relu6中的每一者可以执行与例如由函数f(x)=max(0,x)(例如,对于所有负输入x,输出为零)定义的激活函数对应的修正线性单元(relu)操作。例如,如果大小为32*32*12的输入体数据通过relu层relu1以执行修正线性单元操作,则relu层relu1的输出体数据的大小可以为32*32*12(例如,体数据的大小被保持)。

164.池化层pool1、pool2和pool3中的每一者可以沿着宽度和高度的空间维度对输入体数据执行下采样操作。例如,可以基于2*2过滤器将以2*2矩阵形式排列的四个输入值转换为一个输出值。例如,可以基于2*2最大池化来选择以2*2矩阵形式排列的四个输入值中的最大值,或者可以基于2*2平均池化来获得以2*2矩阵形式排列的四个输入值的平均值。例如,如果大小为32*32*12的输入体数据通过具有2*2过滤器的池化层pool1,则池化层pool1的输出体数据的大小可以为16*16*12(例如,体数据的宽度和高度减小,并且体数据的深度被保持)。

165.典型地,一个卷积层(例如,conv1)和一个relu层(例如,relu1)可以在cnn中形成一对conv/relu层,多对conv/relu层可以重复地布置在cnn中,并且池化层可以周期性插入cnn中,由此减小输入体数据的空间大小并提取输入体数据的特性。

166.输出层或全连接层fc可以针对每个类别输出输入体数据的结果(例如,类别分数)。例如,当重复进行卷积操作和下采样操作时,可以将输入体数据转换为一维矩阵或向量。例如,全连接层fc可以表示输入体数据对应于每个类别的概率。

167.包括在cnn中的层的类型和数目可以不限于参照图20描述的示例,并可以根据示例实施例来改变。另外,尽管未在图20中示出,但cnn还可以包括其他层,诸如,用于将对应

于预测结果的分数值转换为概率值的softmax层、用于添加至少一个偏置的偏置添加层等。

168.参照图21,递归神经网络(rnn)可以包括使用图21左侧示出的特定节点或单元n的重复结构。

169.图21右侧示出的结构可以表示左侧示出的rnn的递归式连接被展开(或铺开)。术语“展开”意味着针对包括所有节点na、nb和nc的完整或整个序列输出或示出网络。例如,如果所关注的序列是3个词的句子,则rnn可以展开为3层神经网络,每个词一层(例如,在没有递归式连接的情况下或在没有循环的情况下)。

170.在图21中的rnn中,x表示rnn的输入。例如,x

t

可以是在时间步长t处的输入,并且x

t-1

和x

t+1

可以分别是在时间步长t-1和t+1处的输入。

171.在图21中的rnn中,s表示隐藏状态。例如,s

t

可以是在时间步长t处的隐藏状态,并且s

t-1

和s

t+1

可以分别是在时间步长t-1和t+1处的隐藏状态。可以基于先前隐藏状态(w)和当前步长(u)处的输入来计算隐藏状态。例如,s

t

=f(ux

t

+ws

t-1

)。例如,函数f常常可以是诸如tanh或relu的非线性函数。计算第一隐藏状态所需的s-1

通常可以初始化为全零。

172.在图21中的rnn中,o表示rnn的输出。例如,o

t

可以是在时间步长t处的输出,并且o

t-1

和o

t+1

可以分别是在时间步长t-1和t+1处的输出。例如,如果需要预测句子中的下一个词,它将是遍及词汇表的概率向量(v)。例如,o

t

=softmax(vs

t

)。

173.在图21中的rnn中,隐藏状态可以是网络的“记忆”。换句话说,rnn可以具有捕获关于到目前为止计算出什么的信息的“记忆”。隐藏状态s

t

可以捕获关于在所有先前时间步长中发生了什么的信息。可以仅仅基于当前时间步长t处的记忆来计算输出o

t

。另外,与在每一层使用不同参数的传统神经网络不同,rnn可以遍及所有时间步长共享相同的参数。这可以代表以下事实:在每个步长处可以执行相同的任务,只是使用的是不同的输入。这可以大大减少需要被训练或学习的参数的总数。

174.在一些示例实施例中,可以基于以上参照图3描述的可靠性信息预测器或存储控制器来执行和处理诸如存储设备的可靠性信息的预测等的各种服务和/或应用。

175.图22是示出根据示例实施例的操作存储设备的方法的流程图。

176.参照图22,在操作存储设备的方法中,预测可靠性信息(s710),并基于预测可靠性信息的结果对存储设备执行读取操作(s730)。

177.在一些实施例中,可以通过以上参照图1描述的操作s100、s200和s300来执行s710。

178.在一些实施例中,每当在存储设备被驱动的同时执行读取操作、编程操作、磨损均衡(wear leveling)、垃圾收集和/或读取回收操作中的至少一者时,可以执行s710。

179.图23是根据一些示例实施例的存储设备和存储系统的框图。

180.参照图23,存储系统1000可以包括主机设备1100和存储设备1200。

181.主机设备1100可以控制存储系统1000的总体操作。例如,主机设备1100可以包括控制主机设备1100的操作并执行操作系统(os)的主机处理器以及存储由主机处理器执行和处理的指令和数据的主机存储器。

182.存储设备1200可以由主机设备1100访问并可以包括存储控制器1210、多个非易失性存储器1220a、1220b和1220c以及缓冲存储器1230。存储控制器1210可以控制存储设备1200的操作。多个非易失性存储器1220a、1220b和1220c可以存储多个数据。

183.缓冲存储器1230可以存储由存储控制器1210执行和处理的命令和数据,并临时存储多个非易失性存储器1220a、1220b和1220c中存储的或者将要存储的数据。

184.图2的存储系统100可以以存储设备1200的形式实现,并且存储控制器1210和非易失性存储器1220a、1220b和1220c可以分别对应于存储控制器310和非易失性存储器320a、320b和320c。

185.包括在存储设备1200中的可靠性信息预测器(srip)1212可以对应于图2的可靠性信息预测器312。在一些实施例中,存储控制器1210还可以包括用于检测写入数据的输入/输出模式的神经处理单元(npu)1214。

186.在一些实施例中,存储设备1200可以是固态驱动器(ssd)、通用闪存(ufs)、多媒体卡(mmc)、嵌入式mmc(emmc)等。在其他实施例中,存储设备1200可以以安全数字(sd)卡、微型sd卡、记忆棒、芯片卡、通用串行总线(usb)卡、智能卡、紧凑型闪存(cf)卡等的形式实现。

187.如上所述,在根据示例实施例的预测存储设备的可靠性信息的方法中,可以执行图1的操作s100、s200和s300,以更有效地预测包括在存储设备中的非易失性存储器的可靠性信息。更具体地,在预测存储设备的可靠性信息的方法中,可以基于劣化特性信息和劣化阶段信息来输出模型请求信号。可以通过基于模型请求信号自适应选择作为多个机器学习模型中的一者的最佳机器学习模型来预测非易失性存储器的可靠性信息。即,预测存储设备的可靠性信息的方法可以通过在考虑非易失性存储器的劣化程度的情况下自适应读取最佳机器学习模型的参数来有效地预测非易失性存储器的可靠性信息。

188.以上示出了示例实施例并且不被理解为是对其的限制。虽然已经描述了一些示例实施例,但本领域的技术人员将容易理解,在实质上不脱离示例实施例的新颖教导和优点的情况下,可以在示例实施例中进行许多修改。因此,所有这些修改形式旨在被包括在如权利要求书中限定的示例实施例的范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1