一种基于PCIe104接口的国密算法卡的制作方法

一种基于pcie104接口的国密算法卡

技术领域:

1.本实用新型属于加密设备技术领域,特别涉及一种基于pcie104接口的国密算法卡。

背景技术:

2.随着计算机的飞速发展,计算机网络已经成为一种不可缺少的信息交换工具。同时,计算机网络具有开放性、互联性、连接方法的多样性、终端分布的不均匀性等特点,网络安全也就成为当今网络社会的焦点,人们在广泛应用网络的同时更加关注私有数据的安全性。近年来,国家有关机关和监管机构站在国家安全的高度提出了推动国密算法应用实施、加强行业安全可控的要求。为了摆脱对国外技术和产品的过度依赖,建设行业网络安全环境。增强我国行业信息系统的“安全可控”能力显得尤为必要和迫切。密码算法是保障信息安全的核心技术,尤其是最关键的银行业等核心领域长期以来都是沿用3des、sha

‑

1、rsa等国际通用的密码算法体系及相关标准。为保障重要密码应用安全,国家密码管理局公布了我国自主研制的sm2、 sm3、sm4三类算法,分别是非对称算法、哈希算法和对称算法。通过数据加密,人们可以有效地保证通信线路上的内容不被泄露,而且还可以检验传送信息的完整性。

3.对于一些关键行业,国家要求必须使用硬件加密设备,密钥必须保存在硬件载体上,不能出现在系统内存中。因此高性能国密算法卡也成为网络和信息安全等领域一个十分重要的部件。目前,市面上的算法卡一般为pci或者pcie的接口,多为传统的90

°

竖插或者180

°

平插方式插卡,这类插卡的方式在一定程度上占用空间比较大且在稳定性上存在一些问题,比如,容易从卡槽脱落,金手指易氧化等。这将导致数据传输延迟、响应速度慢等的问题。

4.公开于该背景技术部分的信息仅仅旨在增加对本实用新型的总体背景的理解,而不应当被视为承认或以任何形式暗示该信息构成已为本领域一般技术人员所公知的现有技术。

技术实现要素:

5.本实用新型的目的在于提供一种基于pcie104接口的国密算法卡,从而克服上述现有技术中的缺陷。

6.为实现上述目的,本实用新型采用的技术方案如下:

7.一种基于pcie104接口的国密算法卡,包括主处理器、分别与主处理器连接的存储模块、电源模块、时钟模块、国密算法模块、随机数模块、销毁模块、pcie104接口,所述主处理器用于数据的采集及处理,所述存储模块用于文件的配置及数据的存储,所述国密算法模块用于对数据进行加密,所述随机数模块用于产生密钥,所述销毁模块用于销毁密钥,所述pcie104接口用于连接外部服务器,所述主处理器通过pcie104接口与外部服务器实现数据输入输出通讯。

8.所述主处理器选用fpga芯片,所述fpga芯片与pcie104接口通过pcie2.0 信号进行数据传输。

9.所述存储模块选用128mbit的spi flash存储。

10.所述pcie104接口与外部服务器通过扣板或螺丝锁紧。

11.所述电源模块与主处理器之间还设置有电源转换模块。

12.所述主处理器还设置有jiag测试访问接口和手动复位按钮。

13.采用本实用新型的技术方案的一个方面具有以下有益效果:

14.本实用新型在主处理器上连接国密算法模块、随机数模块及销毁模块,可保障数据的安全性;其中存储模块用于文件的配置及数据的存储,可实现文件配置加速,降低系统间的延迟,提高系统的响应速度;此外pcie104接口与外部服务器通过扣板或螺丝锁紧,可提高系统稳定性,节省安装空间。

附图说明:

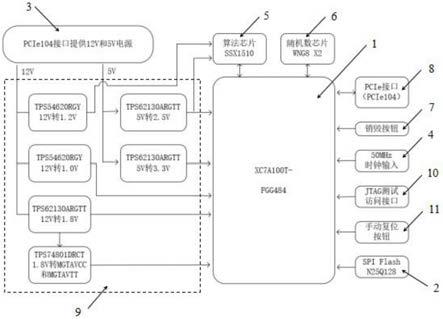

15.图1为本实用新型的一种基于pcie104接口的国密算法卡的示意图。

16.附图说明:1

‑

主处理器、2

‑

存储模块、3

‑

电源模块、4

‑

时钟模块、5

‑

国密算法模块、6

‑

随机数模块、7

‑

销毁模块、8

‑

pcie104接口、9

‑

电源转换模块、 10

‑

jiag测试访问接口、11

‑

手动复位按钮。

具体实施方式:

17.下面对本实用实用新型的具体实施方式进行详细描述,但应当理解本实用新型的保护范围并不受具体实施方式的限制。

18.除非另有其它明确表示,否则在整个说明书和权利要求书中,术语“包括”或其变换如“包含”或“包括有”等等将被理解为包括所陈述的元件或组成部分,而并未排除其它元件或其它组成部分。

19.如图1所示,一种基于pcie104接口的国密算法卡,包括主处理器1、分别与主处理器1连接的存储模块2、电源模块3、时钟模块4、国密算法模块 5、随机数模块6、销毁模块7、pcie104接口8,所述主处理器1用于数据的采集及处理,所述存储模块2用于文件的配置及数据的存储,所述国密算法模块5用于对数据进行加密,所述随机数模块6用于产生密钥,所述销毁模块7用于销毁密钥,所述pcie104接口8用于连接外部服务器,所述主处理器1通过pcie104接口8与外部服务器实现数据输入输出通讯。

20.所述主处理器1选用fpga芯片,所述fpga芯片与pcie104接口8通过 pcie2.0信号进行数据传输,其中fpga芯片具体为xilinx fpga模块,具有业界最低的系统成本和功耗的fpga芯片。

21.所述存储模块2选用128mbit的spi flash存储,具体的选用n25q128a13ese40f芯片。

22.所述pcie104接口8与外部服务器通过扣板或螺丝锁紧。

23.所述电源模块3与主处理器1之间还设置有电源转换模块9。

24.所述主处理器1还设置有jiag测试访问接口10和手动复位按钮11。

25.此外,国密算法模块5选用ssx1510芯片,xilinx fpga模块通过数据总线与国密算

法模块5连接,国密算法模块5由fpga状态机控制,用于实现sm2 运算、sm3摘要生产和sm4加解密算法,可极大的提高算法卡保护的数据机密性、完整性;国密算法模块5通过完善的自检措施,可保证算法卡的可用性和运行的稳定性、使用身份鉴别技术防止非法用户操作算法卡、通过密钥分层保护机制,可实现密钥的逐层保护,防止密钥泄露,并且算法卡的密钥在任何情况下均不会以明文形式出现在算法卡以外的任何地方;

26.随机数模块6选用wng8芯片,xilinx fpga模块通过数据总线与随机数模块6连接;

27.销毁模块7选用kan4541芯片,xilinx fpga模块通过fpga一个管脚外接毁钥按键,其余管脚被所述密码卡的保护罩压住,当有外力强行破坏保护罩时,会及时销毁算法芯片内部的密钥。

28.实施时,主处理器1通过pcie104接口8采集外部服务器数据,由存储模块2对采集的数据进行文件配置及数据存储,通过国密算法模块5对数据进行加解密算法保护,再通过随机数模块6生成密钥及密钥对形成数据保护,销毁模块7用于需要时销毁密钥及密钥对,其中电源转换模块9用于将电压转换后再为主处理器1的供电。

29.本实用新型在主处理器1上连接国密算法模块5、随机数模块6及销毁模块7,可保障数据的安全性;其中存储模块2用于文件的配置及数据的存储,可实现文件配置加速,降低系统间的延迟,提高系统的响应速度;此外pcie104 接口8与外部服务器通过扣板或螺丝锁紧,可提高系统稳定性,节省安装空间。

30.前述对本实用新型的具体示例性实施方案的描述是为了说明和例证的目的。这些描述并非想将本实用新型限定为所公开的精确形式,并且很显然,根据上述教导,可以进行很多改变和变化。对示例性实施例进行选择和描述的目的在于解释本实用新型的特定原理及其实际应用,从而使得本领域的技术人员能够实现并利用本实用新型的各种不同的示例性实施方案以及各种不同的选择和改变。本实用新型的范围意在由权利要求书及其等同形式所限定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1