ARM芯片与FPGA芯片的高速通信模块及变频控制器的制作方法

arm芯片与fpga芯片的高速通信模块及变频控制器

技术领域

1.本实用新型涉及电子电路领域,尤其涉及一种arm芯片与fpga芯片的高速通信模块及变频控制器。

背景技术:

2.本部分旨在为权利要求书中陈述的本实用新型实施例提供背景或上下文。此处的描述不因为包括在本部分中就承认是现有技术。

3.在变频控制器中,将arm芯片作为变频器的主控制芯片,将fpga芯片作为变频器的外围接口芯片,利用arm芯片能够实现各种复杂算法,利用fpga芯片不仅能够实现高速并行数据传输,还能够实现快速响应和高精度变频控制,实时性强、灵活性高。

4.在实现arm芯片与fpga芯片的通信时,现有技术采用spi总线或者rs485总线进行数据双向交换,数据在传输过程中容易受到外部信号的干扰,同时传输数据效率较低,数据传输速度慢,不适用于块数据的传输。

技术实现要素:

5.本实用新型实施例中提供了一种arm芯片与fpga芯片的高速通信模块,用以在arm芯片与fpga芯片之间实现高速数据传输,该高速通信模块包括:arm芯片和fpga芯片;其中,arm芯片与fpga芯片之间通过16位数据总线或地址总线连接,以并行方式传输数据。

6.进一步地,本实用新型实施例中提供的高速通信模块中,arm芯片采用imx6qd芯片;fpga芯片采用xc6slx16-3ftg256c&w25q80vss芯片。

7.进一步地,本实用新型实施例中提供的高速通信模块中,arm芯片的d16信号管脚、d17信号管脚、d18信号管脚、d19信号管脚、d20信号管脚、d21信号管脚、d22信号管脚、d23信号管脚、d24信号管脚、d25信号管脚、d26信号管脚、d27信号管脚、d28信号管脚、d29信号管脚、d30信号管脚、d31信号管脚,与fpga芯片的eim_d16信号管脚、eim_d17信号管脚、eim_d18信号管脚、eim_d19信号管脚、eim_d20信号管脚、eim_d21信号管脚、eim_d22信号管脚、eim_d23信号管脚、eim_d24信号管脚、eim_d25信号管脚、eim_d26信号管脚、eim_d27信号管脚、eim_d28信号管脚、eim_d29信号管脚、eim_d30信号管脚、eim_d31信号管脚分别连接,用于实现16位数据信号传输。

8.进一步地,本实用新型实施例中提供的高速通信模块中,arm芯片的eb0信号管脚、eb1信号管脚、eb2信号管脚、eb3信号管脚,与fpga芯片的eim_eb0信号管脚、eim_eb1信号管脚、eim_eb2信号管脚、eim_eb3信号管脚分别连接,用于实现块数据传输。

9.进一步地,本实用新型实施例中提供的高速通信模块中,arm芯片的bclk信号管脚,与fpga芯片的eim_bclk信号管脚连接,用于实现时钟信号传输。

10.进一步地,本实用新型实施例中提供的高速通信模块中,arm芯片的cs0信号管脚、cs1信号管脚、we_b信号管脚、wait信号管脚、oe_b信号管脚,与fpga芯片的eim_cs0信号管脚、eim_cs1信号管脚、eim_we_b信号管脚、eim_wait信号管脚、eim_oe_b信号管脚分别连

接,用于实现使能信号传输。

11.进一步地,本实用新型实施例中提供的高速通信模块中,arm芯片的da0信号管脚、da1信号管脚、da2信号管脚、da3信号管脚、da4信号管脚、da5信号管脚、da6信号管脚、da7信号管脚、da8信号管脚、da9信号管脚、da10信号管脚、da11信号管脚、da12信号管脚、da13信号管脚、da14信号管脚、da15信号管脚,与fpga芯片的eim_da0信号管脚、eim_da1信号管脚、eim_da2信号管脚、eim_da3信号管脚、eim_da4信号管脚、eim_da5信号管脚、eim_da6信号管脚、eim_da7信号管脚、eim_da8信号管脚、eim_da9信号管脚、eim_da10信号管脚、eim_da11信号管脚、eim_da12信号管脚、eim_da13信号管脚、eim_da14信号管脚、eim_da15信号管脚分别连接,用于实现地址信号传输。

12.进一步地,本实用新型实施例中提供的高速通信模块中,arm芯片的cpu_fpga0信号管脚、cpu_fpga1信号管脚、cpu_fpga2信号管脚、cpu_fpga3信号管脚、cpu_fpga4信号管脚、cpu_fpga5信号管脚、cpu_fpga6信号管脚、cpu_fpga7信号管脚,与fpga芯片的csi0_dat4信号管脚、csi0_dat5信号管脚、csi0_dat6信号管脚、csi0_dat7信号管脚、csi0_dat12信号管脚、csi0_dat13信号管脚、csi0_dat16信号管脚、csi0_dat17信号管脚分别连接,用于实现中断信号传输。

13.本实用新型实施例中还提供了一种变频控制器,用以在arm芯片与fpga芯片之间实现高速数据传输,该变频控制器包括:上述的arm芯片与fpga芯片的高速通信模块。

14.进一步地,变频控制器还包括:fpga芯片用于将arm芯片输出的控制信号并行传输到多个外部变频设备。

15.进一步地,变频控制器还包括:外部扩展板,与fpga芯片连接,用于扩展出各种现场总线或以太网总线。

16.本实用新型实施例中提供的arm芯片与fpga芯片的高速通信模块及变频控制器,通过16位数据总线或地址总线将arm芯片与fpga芯片连接,以并行方式传输数据,能够在arm芯片与fpga芯片之间实现高速数据的传输。

附图说明

17.为了更清楚地说明本实用新型实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本实用新型的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。在附图中:

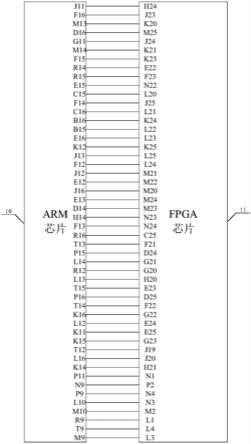

18.图1为本实用新型实施例中一种arm芯片与fpga芯片的高速通信模块示意图;

19.图2为本实用新型实施例中一种变频控制器示意图。

具体实施方式

20.为使本实用新型实施例的目的、技术方案和优点更加清楚明白,下面结合附图对本实用新型实施例做进一步详细说明。在此,本实用新型的示意性实施例及其说明用于解释本实用新型,但并不作为对本实用新型的限定。

21.本实用新型实施例中提供了一种arm芯片与fpga芯片的高速通信模块,图1为本实用新型实施例中一种arm芯片与fpga芯片的高速通信模块示意图,如图1所示,该高速通信

模块包括:arm芯片10和fpga芯片20;其中,arm芯片10与fpga芯片20之间通过16位数据总线或地址总线连接,以并行方式传输数据。

22.在一个实施例中,本实用新型实施例中提供的高速通信模块中,arm芯片10采用imx6qd芯片;fpga芯片20采用xc6slx16-3ftg256c&w25q80vss芯片。表1示出了imx6qd芯片和xc6slx16-3ftg256c&w25q80vss芯片的信号管脚。

23.表1

24.[0025][0026]

imx6qd为一款高端arm芯片,可以运行linux操作系统;通过数据线、地址线、读命令、写命令、通用输入输出线等来进行高速数据交换和传输。目的是将部分快速任务交给fpga来运算和处理,利用fpga并行计算的优势,同时完成多项复杂任务。

[0027]

对于imx6qd芯片来说,外部fpga就是一个智能协处理器,按照严格的时序和顺序将数据写入给fpga后,等待fpga处理完成信号,再读取fpga计算的结果。对imx6软件编程来说,外部fpga就等效为一块双口ram。

[0028]

对于fgpa芯片来说,imx6qd也等效为以块双口ram,按照严格的时序和顺序,可以进行数据的读写。

[0029]

需要说明的是,xc6slx16-3ftg256c&w25q80vss芯片,属于spartan-6fpga系列,是xilinx公司的低成本、低功耗fpga。第六代spartan系列基于低功耗45nm、9金属铜层、双栅极氧化层工艺技术,以及高级功耗管理技术。

[0030]

为了实现数据信号传输,如表1所示,arm芯片10的d16信号管脚、d17信号管脚、d18信号管脚、d19信号管脚、d20信号管脚、d21信号管脚、d22信号管脚、d23信号管脚、d24信号管脚、d25信号管脚、d26信号管脚、d27信号管脚、d28信号管脚、d29信号管脚、d30信号管脚、d31信号管脚,与fpga芯片20的eim_d16信号管脚、eim_d17信号管脚、eim_d18信号管脚、eim_d19信号管脚、eim_d20信号管脚、eim_d21信号管脚、eim_d22信号管脚、eim_d23信号管脚、eim_d24信号管脚、eim_d25信号管脚、eim_d26信号管脚、eim_d27信号管脚、eim_d28信号管脚、eim_d29信号管脚、eim_d30信号管脚、eim_d31信号管脚分别连接,用于实现16位数据信号传输。

[0031]

为了实现块数据传输,如表1所示,arm芯片10的eb0信号管脚、eb1信号管脚、eb2信号管脚、eb3信号管脚,与fpga芯片20的eim_eb0信号管脚、eim_eb1信号管脚、eim_eb2信号管脚、eim_eb3信号管脚分别连接,用于实现块数据传输。

[0032]

为了实现时钟信号传输,如表1所示,arm芯片10的bclk信号管脚,与fpga芯片20的eim_bclk信号管脚连接,用于实现时钟信号传输。

[0033]

为了实现使能信号传输,如表1所示,arm芯片10的cs0信号管脚、cs1信号管脚、we_b信号管脚、wait信号管脚、oe_b信号管脚,与fpga芯片20的eim_cs0信号管脚、eim_cs1信号管脚、eim_we_b信号管脚、eim_wait信号管脚、eim_oe_b信号管脚分别连接,用于实现使能信号传输。

[0034]

为了实现地址信号传输,如表1所示,arm芯片10的da0信号管脚、da1信号管脚、da2信号管脚、da3信号管脚、da4信号管脚、da5信号管脚、da6信号管脚、da7信号管脚、da8信号管脚、da9信号管脚、da10信号管脚、da11信号管脚、da12信号管脚、da13信号管脚、da14信号管脚、da15信号管脚,与fpga芯片20的eim_da0信号管脚、eim_da1信号管脚、eim_da2信号管脚、eim_da3信号管脚、eim_da4信号管脚、eim_da5信号管脚、eim_da6信号管脚、eim_da7信号管脚、eim_da8信号管脚、eim_da9信号管脚、eim_da10信号管脚、eim_da11信号管脚、eim_da12信号管脚、eim_da13信号管脚、eim_da14信号管脚、eim_da15信号管脚分别连接,用于实现地址信号传输。

[0035]

为了实现中断信号传输,如表1所示,arm芯片10的cpu_fpga0信号管脚、cpu_fpga1信号管脚、cpu_fpga2信号管脚、cpu_fpga3信号管脚、cpu_fpga4信号管脚、cpu_fpga5信号管脚、cpu_fpga6信号管脚、cpu_fpga7信号管脚,与fpga芯片20的csi0_dat4信号管脚、csi0_dat5信号管脚、csi0_dat6信号管脚、csi0_dat7信号管脚、csi0_dat12信号管脚、csi0_dat13信号管脚、csi0_dat16信号管脚、csi0_dat17信号管脚分别连接,用于实现中断信号传输。

[0036]

当imx6向fpga写数据时,片选0、片选1都输出逻辑低电平,使能输出高电平,写使能输出高电平,将16位数据输出到data[15:0]管脚上,以及对应的地址线addr[15:0],不断查看wait等待信号。如果该信号为1,表示fpga完成了本次数据写操作,可以对下一组数据进行写操作。如果该信号为0,表示fpga未完成本次数据写操作,需要再等待若干个时钟周期,直到本次写操作完成,才能够进行下一次写操作或者读操作。

[0037]

当imx6向fpga读数据时,片选0、片选1都输出逻辑低电平,使能输出高电平,写使能输出低电平,将16位地址数据输出到addr[15:0]管脚上,不断查看wait等待信号。如果该信号为1,表示fpga完成了本次数据读操作,可以对下一组地址的数据进行读操作。如果该信号为0,表示fpga未完成本次数据读操作,需要再等待若干个时钟周期,直到本次读操作完成,才能够进行下一次写操作或者读操作。

[0038]

当imx6需要fpga快速完成某项运算时,可以在中断0~3管脚上输出一个从低电平到高电平的上升沿,fpga收到上升沿后,会立即进入中断处理程序。

[0039]

当fpga需要imx6快速完成某项运算时,可以在中断4~7管脚上输出一个从低电平到高电平的上升沿,imx6收到上升沿后,会立即进入中断处理程序。

[0040]

块操作0~4和块操作时钟,是用来实现imx6与fpga之间大量数据的快速读写交换。进入块操作后,只需要在地址总线addr[15:0]管脚上写第一个地址,fpga或imx6就会记住该地址。随着块操作时钟的改变,fpga或imx6内部会自动对地址进行增加,不需要在地址总线addr[15:0]管脚上进行输出,只需要将输出16位数据输出到data[15:0]管脚上,就可以完成大量数据的快速读写传输。根据当前设计,将整个数据区域划分为16个数据块,通过块操作0~3来进行选择。表2所示为块操作块操作0~3的时钟信号。

[0041]

表2

[0042]

序号块操作选择0块操作选择1块操作选择2块操作选择3块选择1低电平低电平低电平低电平02高电平低电平低电平低电平13低电平高电平低电平低电平2

4高电平高电平低电平低电平35低电平低电平高电平低电平46高电平低电平高电平低电平57低电平高电平高电平低电平68高电平高电平高电平低电平79低电平低电平低电平高电平810高电平低电平低电平高电平911低电平高电平低电平高电平1012高电平高电平低电平高电平1113低电平低电平高电平高电平1214高电平低电平高电平高电平1315低电平高电平高电平高电平1416高电平高电平高电平高电平15

[0043]

图2为本实用新型实施例中一种变频控制器示意图,如图2所示,本实用新型实施例中还提供了一种变频控制器,包括:上述任一项的arm芯片与fpga芯片的高速通信模块。

[0044]

在一个实施例中,本实用新型实施例中提供的变频控制器中,还包括:fpga芯片20用于将arm芯片10输出的控制信号并行传输到多个外部变频设备。

[0045]

在一个实施例中,本实用新型实施例中提供的变频控制器还包括:usb接口301,与arm芯片10连接,用于与外部usb设备通信。

[0046]

本实用新型实施例提供的变频控制器,将arm芯片作为变频器的主控制芯片,将fpga芯片作为变频器的外围接口芯片,利用arm芯片能够实现各种复杂算法,利用fpga芯片不仅能够实现高速并行数据传输,还能够实现快速响应和高精度变频控制,实时性强、灵活性高。通过rs422转换电路30,实现usb信号与ttl信号之间的转换,使得arm芯片10通过usb接口与外部usb设备通信,从而便于usb调试arm芯片系统(例如,linux系统)的功能,方便系统调试人员的工作,还可支持热插拔功能。

[0047]

在一个实施例中,本实用新型实施例中提供的变频控制器还包括:pcie转pci芯片101、光纤以太网芯片102a、光纤以太网接口103a、电口以太网芯片102b和电口以太网接口103b;

[0048]

其中,光纤以太网接口103a,与光纤以太网芯片102a连接,用于通过光纤传输以太网数据;电口以太网接口103b,与电口以太网芯片102b连接,用于通过网线传输以太网数据;pcie转pci芯片101与arm芯片10连接,用于将arm芯片10扩展出光纤以太网总线和电口以太网总线,使得arm芯片10通过扩展出的光纤以太网总线与光纤以太网芯片102a连接;通过扩展出的电口以太网总线与电口以太网芯片102b连接。

[0049]

本实用新型实施例提供的变频控制器,集成百兆标准以太网接口,支持tcp/ip协议,通过pcie转pci芯片101扩展出光纤以太网接口,实现高速以太网原始报文的收发。可选地,本实用新型实施例中,通过pcie转pci芯片101扩展出两路以太网总线,其中,一路为电口以太网,另一路为塑料光纤以太网。可选地,本实用新型实施例中pcie转pci芯片可以将一个pcie总线接口扩展出两个pci总线接口,每个pci总线接口可以与一个以太网芯片连接。

[0050]

可选地,pcie转pci芯片可以xio2001芯片。

[0051]

在一个实施例中,本实用新型实施例中提供的变频控制器还包括:rtc时钟芯片104,与arm芯片10连接,用于提供时钟信号。可选地,本实用新型实施例提供的变频控制器中,arm芯片10通过i2c总线扩展出实时时钟(real-time clock,rtc)芯片,来实现实际时间的记录和存储,使得整个系统和控制器更加完善。

[0052]

在一个实施例中,本实用新型实施例中提供的变频控制器还包括:ddr内存106和mmc存储器105;其中,ddr内存106,与arm芯片10连接,用于存储内存数据;mmc存储器105,与arm芯片10连接,用于存储数据。可选地,mmc存储器可以是mmc卡,通过mmc卡实现板载的数据存储,对于系统校验和加密数据,都需要保存在mmc卡中。由于mmc卡的读写速度快于cf卡读写,因此紧急保持的数据,可以存储在mmc卡中。本实用新型实施例提供的变频控制器中,arm芯片通过ddr的的方式扩展ram,实现了大批量内存数据的存储和运算,支持当前各种主流ddr总线。

[0053]

在一个实施例中,本实用新型实施例中提供的变频控制器还包括:usb接口301,用于与外部usb设备通信;usb转ttl模块302,与所述arm芯片10连接,用于将usb数据转换为ttl数据。

[0054]

本实用新型实施例提供的变频控制器可以采用24v直流供电,通过底部的电源接口211与外部电源连接。可选地,电源接口211可以是电源端子。

[0055]

可选地,本实用新型实施例提供的变频控制器中,arm芯片采用4核a9系列,主频可达1ghz。与现有dsp芯片的主频(百兆级)相比,本实用新型实施例提供的变频控制器,基于arm+fpga系统架构,能够实现快速实时响应和高精度变频控制,从而更适应于高端变频器及系统应用的需求。另外,本实用新型实施例提供的变频控制器中,fpga芯片负责并行的高速数据处理,光纤数据通信等工作,通过协调配合实现一个控制器带多个电机的功能。可选地,arm芯片可以通过本地总线与fpga芯片进行高速数据通信。

[0056]

在一个实施例中,本实用新型实施例中提供的变频控制器还包括:cf卡接口107,与arm芯片10连接,用于将数据存储至外部cf卡中或读取外部cf卡中的数据。通过将arm芯片扩展出cf卡存储功能,将系统数据或用户数据存储在cf卡中,能够方便通过cf卡进行系统和程序升级。

[0057]

在一个实施例中,本实用新型实施例中提供的变频控制器还包括:数码管驱动芯片108和数码管109;其中,数码管驱动芯片108与arm芯片10连接,用于驱动数码管109点亮或熄灭;数码管109用于显示变频控制器的状态信息。可选地,数码管109为一个8位led数码管,用来显示当前控制器状态,方便用户判断当前控制器内部软件的情况。可选地,数码管驱动芯片108可以是74hc595d串转并芯片,将arm芯片的串行信号转换为驱动led数码管的并行信号。

[0058]

在一个实施例中,本实用新型实施例中提供的变频控制器还包括:外部扩展板201,与fpga芯片20连接,用于扩展出各种现场总线或以太网总线。fpga芯片通过内部总线扩展了外部扩展板,可以实现各种现场总线、实时以太网总线的支持,增强了系统的扩展性。

[0059]

在一个实施例中,本实用新型实施例中提供的变频控制器还包括:中断信号传输接口212,与fpga芯片20连接,用于传输中断信号。

[0060]

在一个实施例中,本实用新型实施例中提供的变频控制器中,fpga芯片20还可以用于扩展出如下任意一种接口can总线接口202、rs485总线接口203、rs232总线接口204、ssi编码器信号接口205、增量编码器信号接口206、数字量输入信号接口207、数字量输出信号接口208、模拟量输入信号接口209和模拟量输出信号接口210、电源接口211。通过扩展多种通信协议的数据传输接口,实现多通信协议的协调统一操作。其中,fpga芯片通过塑料光纤或者玻璃光纤的方式,扩展出接收或发送快速中断信号的中断信号传输接口,实现多个控制器之间的数据同步和信号同步。arm芯片还支持中断触发功能,以便实现快速信号的紧急处理。

[0061]

综上所述,本实用新型实施例中提供的arm芯片与fpga芯片的高速通信模块及变频控制器,通过16位数据总线或地址总线将arm芯片与fpga芯片连接,以并行方式传输数据,能够在arm芯片与fpga芯片之间实现高速数据的传输。

[0062]

本领域内的技术人员应明白,本实用新型的实施例可提供为方法、系统、或计算机程序产品。因此,本实用新型可采用完全硬件实施例、完全软件实施例、或结合软件和硬件方面的实施例的形式。而且,本实用新型可采用在一个或多个其中包含有计算机可用程序代码的计算机可用存储介质(包括但不限于磁盘存储器、cd-rom、光学存储器等)上实施的计算机程序产品的形式。

[0063]

本实用新型是参照根据本实用新型实施例的方法、设备(系统)、和计算机程序产品的流程图和/或方框图来描述的。应理解可由计算机程序指令实现流程图和/或方框图中的每一流程和/或方框、以及流程图和/或方框图中的流程和/或方框的结合。可提供这些计算机程序指令到通用计算机、专用计算机、嵌入式处理机或其他可编程数据处理设备的处理器以产生一个机器,使得通过计算机或其他可编程数据处理设备的处理器执行的指令产生用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的装置。

[0064]

这些计算机程序指令也可存储在能引导计算机或其他可编程数据处理设备以特定方式工作的计算机可读存储器中,使得存储在该计算机可读存储器中的指令产生包括指令装置的制造品,该指令装置实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能。

[0065]

这些计算机程序指令也可装载到计算机或其他可编程数据处理设备上,使得在计算机或其他可编程设备上执行一系列操作步骤以产生计算机实现的处理,从而在计算机或其他可编程设备上执行的指令提供用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的步骤。

[0066]

以上所述的具体实施例,对本实用新型的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本实用新型的具体实施例而已,并不用于限定本实用新型的保护范围,凡在本实用新型的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本实用新型的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1