一种看门狗复位电路及装置的制作方法

1.本实用新型涉及电子领域,尤其涉及一种看门狗复位电路及装置。

背景技术:

2.目前,现有的cpu(central processing unit,中央处理器)都会存在程序跑飞、死机的情况,而针对出现死机的情况,通常的处理方式主要包括两种,一是对设备进行重新上下电,二是通过硬件复位按钮,来达到系统重新启动的效果。但是,上述两种方式都需要人为操作,对于用户来说,体检并不是很好,并且不是所有设备形态都能接受硬件复位按钮。为了解决这一问题,需要看门狗电路介入,一旦设备死机,电路会自动产生复位信号来使主控重新启动并正常工作。

3.目前,主流的看门狗复位电路为主控io直连专用看门狗芯片的喂狗信号输入管脚,但是,由于一些主控管脚抗干扰能力较弱,在静电或一些极端的环境情况下,会误触发看门狗复位,导致主控重新启动,从而影响主控的稳定性,使主控出现一些意料之外的特殊情况。

技术实现要素:

4.鉴于以上所述现有技术的缺点,本实用新型提供一种看门狗复位电路及装置,以解决上述技术问题。

5.本实用新型提供的看门狗复位电路,包括:

6.耦合电容模块、复位控制模块、分压模块和限压模块,

7.所述分压模块与限压模块连接,所述限压模块分别与耦合电容模块和复位控制模块连接;

8.所述复位控制模块通过耦合电容模块与主控模块连接,用于对主控模块进行复位;

9.所述耦合电容模块包括第一电容和第二电容;

10.所述第一电容的一端与主控模块的信号输出端连接,所述第一电容的另一端与复位控制模块的清零输入端连接,所述第二电容的一端分压模块连接,所述第二电容的另一端接地;

11.当主控模块的输出信号由高电平变为低电平时,第一电容与主控模块的信号输出端连接的一端接收到下降沿跳变,第一电容的另一端产生下降沿跳变,触发复位控制模块输出复位信号。

12.与本实用新型的一实施例中,所述分压模块包括第三电阻和第四电阻;

13.所述第三电阻的一端分别与第四电阻的一端和第二电容的一端连接,第三电阻的另一端与电源连接,用于提供工作电压;

14.所述第四电阻的两端分别与第二电容的两端连接,形成并联结构。

15.与本实用新型的一实施例中,所述限压模块包括第一二极管,所述第一二极管的

正极与复位控制模块的清零输入端连接,所述第一二极管的负极与第二电容的非接地端连接。

16.与本实用新型的一实施例中,还包括第一电阻和第二电阻,所述第一电阻的一端与第一电容的与主控模块的信号输出端连接的一端连接,所述第一电阻的另一端接地,所述第二电阻的一端与电源连接,第二电阻的另一端与第一电容连接主控模块信号输出端的一端连接。

17.与本实用新型的一实施例中,还包括第五电阻,所述第五电阻一端与复位控制模块的复位端连接,第五电阻的另一端接地。

18.与本实用新型的一实施例中,所述第一二极管为肖特基二极管。

19.本实用新型还提供一种看门狗复位装置,包括互相连接的主控模块和如上述的看门狗复位电路;

20.所述看门狗复位电路包括:耦合电容模块、复位控制模块、分压模块和限压模块,

21.所述分压模块与限压模块连接,所述限压模块分别与耦合电容模块和复位控制模块连接;

22.所述复位控制模块通过耦合电容模块与主控模块连接,用于对主控模块进行复位;

23.所述耦合电容模块包括第一电容和第二电容;

24.所述第一电容的一端与主控模块的信号输出端连接,所述第一电容的另一端与复位控制模块的清零输入端连接,所述第二电容的一端分压模块连接,所述第二电容的另一端接地;

25.当主控模块的输出信号由高电平变为低电平时,第一电容与主控模块的信号输出端连接的一端接收到下降沿跳变,第一电容的另一端产生下降沿跳变,触发复位控制模块输出复位信号。

26.与本实用新型的一实施例中,所述主控模块包括中央处理器。

27.本实用新型的有益效果:本实用新型中的看门狗复位电路及装置,改进看门狗电路心跳信号的触发方式,通过使用电容耦合的方式,解决了现有技术中主控死机的问题,并且,避免了由于主控管脚抗干扰能力较弱,导致在静电或一些极端的环境情况下,误触发看门狗复位,致使主控重新启动的问题,大大提高了看门狗电路的可靠性。

附图说明

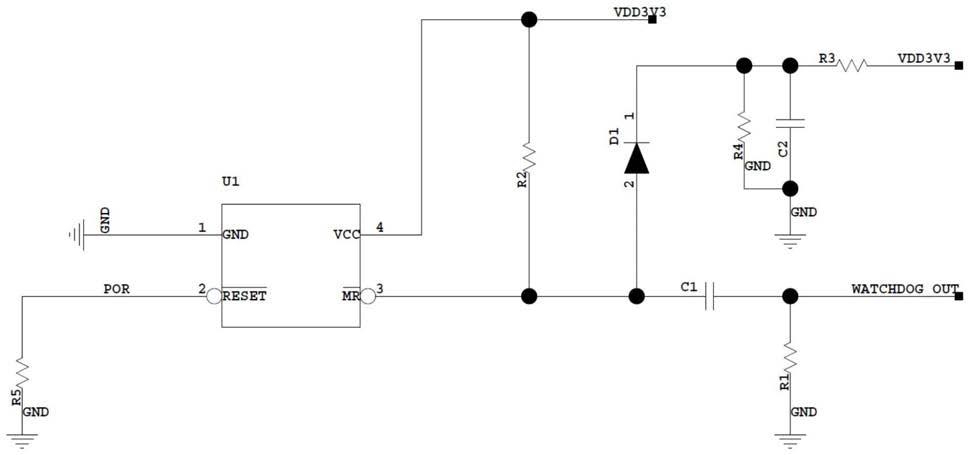

28.图1是本实用新型实施例中看门狗复位电路的电路结构示意图。

29.附图标记说明:

30.r1-第一电阻;r2-第二电阻;r3-第三电阻;r4-第四电阻;r5-第五电阻;

31.c1-第一电容;c2-第二电容;

32.d1-第一二极管;

33.u1-复位控制模块。

具体实施方式

34.以下通过特定的具体实例说明本实用新型的实施方式,本领域技术人员可由本说

明书所揭露的内容轻易地了解本实用新型的其他优点与功效。本实用新型还可以通过另外不同的具体实施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本实用新型的精神下进行各种修饰或改变。需说明的是,在不冲突的情况下,以下实施例及实施例中的特征可以相互组合。

35.需要说明的是,以下实施例中所提供的图示仅以示意方式说明本实用新型的基本构想,遂图式中仅显示与本实用新型中有关的组件而非按照实际实施时的组件数目、形状及尺寸绘制,其实际实施时各组件的型态、数量及比例可为一种随意的改变,且其组件布局型态也可能更为复杂。

36.在下文描述中,探讨了大量细节,以提供对本实用新型实施例的更透彻的解释,然而,对本领域技术人员来说,可以在没有这些具体细节的情况下实施本实用新型的实施例是显而易见的,在其他实施例中,以方框图的形式而不是以细节的形式来示出公知的结构和设备,以避免使本实用新型的实施例难以理解。

37.如图1所示,本实施例中的看门狗复位电路,包括:耦合电容模块、复位控制模块u1、分压模块和限压模块,分压模块与限压模块连接,限压模块分别与耦合电容模块和复位控制模块连接;复位控制模块u1通过耦合电容模块与主控模块连接,用于对主控模块进行复位;耦合电容模块包括第一电容c1和第二电容c2;第一电容c1的一端与主控模块的信号输出端watchdog out连接,第一电容c1的另一端与复位控制模块u1的清零输入端mr连接,第二电容c2的一端分压模块连接,所述第二电容c2的另一端接地;当主控模块的输出信号watchdog out由高电平变为低电平时,第一电容c1与主控模块的信号输出端连接的一端接收到下降沿跳变,第一电容c1的另一端产生下降沿跳变,触发复位控制模块输出复位信号por。

38.在本实施例中,分压模块包括第三电阻r3和第四电阻r4,第三电阻r3的一端分别与第四电阻r4的一端和第二电容c2的一端连接,第三电阻r3的另一端与电源vdd连接,用于提供工作电压;第四电阻r4的两端分别与第二电容c2的两端连接,形成并联结构。在本实施例中,限压模块包括第一二极管d1,第一二极管d1的正极与复位控制模块的清零输入端mr连接,第一二极管d1的负极与第二电容c2的非接地端连接。在本实施例中,第一二极管d1为肖特基二极管,肖特基二极管是贵金属(金、银、铝、铂等)为正极,以n型半导体为负极,利用二者接触面上形成的势垒具有整流特性而制成的金属-半导体器件。

39.在本实施例中,还包括第一电阻r1和第二电阻r2,第一电阻r1的一端与第一电容c1的与主控模块的信号输出端连接的一端连接,第一电阻r1的另一端接地,第二电阻r2的一端与电源vdd连接,第二电阻r2的另一端与第一电容c1连接主控模块信号输出端的一端连接。还包括第五电阻r5,第五电阻r5一端与复位控制模块的复位端reset连接,第五电阻r5的另一端接地。

40.在本实施例中,主控模块输出高电平信号watchdog,当主控死机时,watchdog信号由高电平变为低电平,第一电容c1与看门狗复位芯片相连的一端默认状态为高电平,当第一电容c1与主控模块相连的一端接收到下降沿跳变,第一电容c1的另一端也会产生下降沿跳变,持续一定时间低电平后即会触发看门狗芯片u1输出por复位信号,来使主控重新启动,达到主控程序的内部复位的目的,实现看门狗监控主控模块的功能。

41.在本实施例中,以工作电压3.3v,默认watchdog信号为高电平为例,由于当

watchdog信号由低电平跳转到高电平的上升沿,第一电容c1与看门狗芯片u1相连的一端也会在默认3.3v的基础上叠加一个高电平跳变脉冲,上冲值取决于基础高电平2.2v、二极管d1的钳位电压和动作时间、第一电容c1上升沿充放电产生的脉冲,若不加以限制,此上冲值会超过芯片管脚的绝对电压,极端情况下造成芯片闩锁,为解决此影响,本实施例中通过第三电电阻r3和第四电阻r4分压加上二极管钳位电压来使u1的mr脚高电平达到高电平阈值,但由于上升沿脉冲较快,二极管的动作时间不足以使上冲快速降低,本实施例通过增加第二电容c2通过给电容充电的方式来减缓上升沿的跳变速度,可控制u1的mr管脚复位高电平为3.3v。在本实施例中,vcc表示模拟信号电源,vdd是芯片的工作电压,gnd表示模拟信号地。

42.相应的,在本实施例还提供一种看门狗复位装置,包括互相连接的主控模块和如上述实施例中的看门狗复位电路,本实施例的看门狗复位电路,包括:耦合电容模块、复位控制模块u1、分压模块和限压模块,分压模块与限压模块连接,限压模块分别与耦合电容模块和复位控制模块连接;复位控制模块u1通过耦合电容模块与主控模块连接,用于对主控模块进行复位;耦合电容模块包括第一电容c1和第二电容c2;第一电容c1的一端与主控模块的信号输出端watchdog out连接,第一电容c1的另一端与复位控制模块u1的清零输入端mr连接,第二电容c2的一端分压模块连接,所述第二电容c2的另一端接地;当主控模块的输出信号watchdog out由高电平变为低电平时,第一电容c1与主控模块的信号输出端连接的一端接收到下降沿跳变,第一电容c1的另一端产生下降沿跳变,触发复位控制模块输出复位信号por。

43.在本实施例中,主控模块可以是通用处理器,包括中央处理器(central processing unit,简称cpu)、网络处理器(network processor,简称np)等;还可以是数字信号处理器(digital signal processing,简称dsp)、专用集成电路(application specific integrated circuit,简称asic)、现场可编程门阵列(field-programmable gate array,简称fpga)或者其他可编程逻辑器件、分立门或者晶体管逻辑器件、分立硬件组件。可选的,本实施例中的主控模块包括中央处理器。

44.上述实施例仅示例性说明本实用新型的原理及其功效,而非用于限制本实用新型。任何熟悉此技术的人士皆可在不违背本实用新型的精神及范畴下,对上述实施例进行修饰或改变。因此,但凡所属技术领域中具有通常知识者在未脱离本实用新型所揭示的精神与技术思想下所完成的一切等效修饰或改变,仍应由本实用新型的权利要求所涵盖。

45.在上述实施例中,除非另外规定,否则通过使用“第一”、“第二”等序号对共同的对象进行描述,只表示其指代相同对象的不同实例,而非是采用表示被描述的对象必须采用给定的顺序,无论是时间地、空间地、排序地或任何其他方式。在上述实施例中,说明书对“本实施例”、“一实施例”、“另一实施例”、或“其他实施例”的提及表示结合实施例说明的特定特征、结构或特性包括在至少一些实施例中,但不必是全部实施例。“本实施例”、“一实施例”、“另一实施例”的多次出现不一定全部都指代相同的实施例。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1