支持网络升级的电路及电子装置的制作方法

1.本技术属于终端升级技术领域,尤其涉及支持网络升级的电路及电子装置。

背景技术:

2.固件升级指设备通过网络获取软件版本并对设备的固件进行升级,很多设备例如大型显示屏其本身不具有操作系统,无法通过网络进行固件升级,当设备出现问题或者需要对设备进行固件升级时,由于不支持网络隔空升级固件,需要设备生产商实地进行升级维护,对于设备生产商和用户来说升级成本高、难度大。

技术实现要素:

3.本技术的主要目的为提供支持网络升级的电路及电子设备,旨在解决传统不具有操作系统的设备无法通过网络完成固件升级的问题。

4.本技术实施例的第一方面提了支持网络升级的电路,包括:

5.处理器;

6.第一存储单元,与所述处理器连接;

7.主板接口,与所述处理器连接,用于所述处理器通过所述主板接口检测待升级主板的固件信息;以及

8.以太网模块电路,与所述主板接口连接且与所述处理器连接,所述以太网模块电路用于所述主板接口和所述处理器进行网络通信,所述处理器通过网络通信下载固件升级数据并存储至所述第一存储单元,以用于所述待升级主板的固件升级。

9.其中一个实施例中,所述以太网模块电路包括:

10.以太网收发器芯片;

11.晶振电路,与所述以太网收发器芯片连接,所述晶振电路用于给所述以太网收发器芯片提供时钟信号;

12.供电电路,与所述以太网收发器芯片连接,所述供电电路用于给所述以太网收发器芯片供电;以及

13.led控制电路,与所述以太网收发器芯片连接,所述led控制电路用于指示所述以太网模块电路的工作状态。

14.其中一个实施例中,所述以太网模块电路还包括:第一电阻、第二电阻、第三电阻和第四电阻;

15.所述第一电阻、所述第二电阻、所述第三电阻和所述第四电阻分别串接在所述以太网收发器芯片rmii标准信号接口和所述处理器的rmii标准信号接口之间,用于所述以太网收发器芯片和所述处理器之间传输rmii数据。

16.其中一个实施例中,所述以太网模块电路还包括:第五电阻、第六电阻、第七电阻和第八电阻;

17.所述第五电阻串接在所述以太网收发器芯片的使能引脚和所述处理器的使能引

脚之间,用于传输使能信号;

18.所述第六电阻串接在所述以太网收发器芯片的载波侦听引脚和所述处理器的载波侦听引脚之间,用于指示载波侦听和接收数据有效;

19.所述第七电阻串接在所述以太网收发器芯片的数据状态指示引脚和所述处理器的数据状态指示引脚之间,用于指示数据传输状态;

20.所述第八电阻串接在所述以太网收发器芯片的时序参考引脚和所述处理器时序参考引脚之间,用于所述处理器给所述以太网收发器芯片提供时序参考信号;

21.所述以太网收发器芯片的复位引脚、管理信息引脚、管理信息时钟引脚分别和所述处理器的对应的复位引脚、管理信息引脚、管理信息时钟引脚连接。

22.其中一个实施例中,所述主板接口包括:

23.mdi接口,与所述以太网模块电路连接,用于所述待升级主板向所述以太网模块电路传输网络信号;

24.iic接口,与所述处理器连接,用于所述待升级主板和所述处理器通信。

25.其中一个实施例中,所述主板接口还包括:

26.uart接口,与所述处理器连接,用于所述待升级主板和所述处理器通信使所述处理器检测到固件信息;

27.usb接口,与所述处理器连接,用于待升级主板通过所述处理器下载固件升级数据以完成固件升级。

28.其中一个实施例中,所述处理器具有uart接口、spi接口、usb接口、闪存控制器和两个以太网媒体接入控制器。

29.其中一个实施例中,所述第一存储单元包括:闪存芯片、第九电阻和第二电容,所述闪存芯片与所述处理器通过spi接口通信连接,所述第九电阻串接在所述闪存芯片的串行时钟引脚和所述处理器之间,所述闪存芯片的地脚与所述第二电容的一端连接且接地,所述第二电容的另一端与所述闪存芯片的电源引脚连接且接电源。

30.其中一个实施例中,还包括第二存储单元,所述第二存储单元包括eeprom芯片、第十电阻和第三电容,所述eeprom芯片与所述处理器通过iic接口通信连接,所述第十电阻的一端与所述eeprom芯片的测试引脚连接,所述第十电阻的另一端接电源,所述eeprom芯片的地址引脚和地脚共接地,所述第三电容的一端接所述eeprom芯片的电源引脚,所述第三电容的另一端接地。

31.本技术的第二方面提供了一种电子装置,用于网络升级固件,所述电子装置包括上述支持网络升级的电路。

32.本技术实施例与现有技术相比存在的有益效果是:当设备需要进行固件升级时,通过上述的支持网络升级的电路可以对不具有操作系统的设备进行固件升级,通过网络就可以完成设备的隔空升级,大大降低了设备生产商后期维护升级设备的成本,解决了非智能操作系统设备升级难的问题,且该电路集成度高易于实现。

附图说明

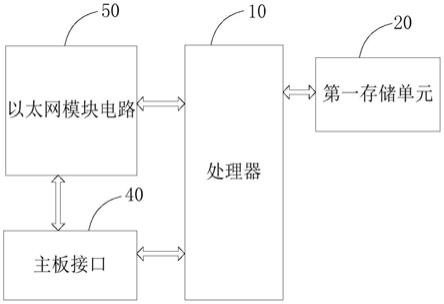

33.图1为本技术一实施例提供的支持网络升级的电路原理示意图;

34.图2为本技术一实施例提供支持网络升级的电路原理图;

35.图3为本技术一实施例提供的主板接口的电路原理图;

36.图4为本技术一实施例提供的处理器和第一存储单元的电路原理图;

37.图5为本技术一实施例提供的处理器和第二存储单元的电路原理图。

具体实施方式

38.为了使本技术所要解决的技术问题、技术方案及有益效果更加清楚明白,以下结合附图及实施例,对本技术进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本技术,并不用于限定本技术。

39.需要说明的是,当元件被称为“固定于”或“设置于”另一个元件,它可以直接在另一个元件上或者间接在该另一个元件上。当一个元件被称为是“连接于”另一个元件,它可以是直接连接到另一个元件或间接连接至该另一个元件上。

40.需要理解的是,术语“长度”、“宽度”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本技术和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本技术的限制。

41.此外,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征。在本技术的描述中,“多个”的含义是两个或两个以上,除非另有明确具体的限定。

42.如图1所示,支持网络升级的电路包括处理器10,第一存储单元20、主板接口40以及以太网模块电路50。

43.处理器10可以为单片机、arm处理器或者其他可编程控制器;第一存储单元20和处理器10通信连接,第一存储单元20包括存储芯片例如闪存芯片flash芯片,第一存储单元20用于存储固件升级数据,处理器10将通过网络通讯下载的固件升级数据存储到flash存储芯片中;以太网模块电路50与主板接口40连接且与处理器10连接,以太网模块电路50用于主板接口40和处理器10进行网络通信,处理器10通过网络通信下载固件升级数据并存储至第一存储单元20以用于待升级主板的固件升级。

44.该实施例中,支持网络升级的电路通过网络检测到固件升级数据推送,将固件升级数据下载到第一存储单元20的存储芯片中,处理器10通过主板接口40和待升级主板进行通信,处理器10将存储在第一存储单元20中的固件升级数据下载到待升级主板中完成待升级主板设备的固件升级,对于不具有智能操作系统的设备通过网络完成固件的升级维护,降低设备固件升级维护的成本和难度,且该电路集成度高易于实现。

45.在该升级的过程中,例如固件信息的检测,固件升级数据的下载和写入虽然可能需要软件程序实现,但这些软件程序都是容易从常规应用中获取。

46.其中一个实施例中,处理器10可以是具有uart(universal asynchronous receiver/transmitter,通用异步收发)接口、spi(serial peripheral interface,串行外围设备接口)接口、falsh控制器和两个mac(media access control,媒体接入控制器)控制器的功能多样的处理器,并且处理器10支持带有存储器直接访问请求dma(direct memory access,存储器直接访问)请求和确认的sram(static-random-access-memory,静态随机存

取存储器)及外部设备,处理器10支持带有dma请求和确认的sram及外部设备,当待升级设备需要下载固件升级数据时,待升级设备可以直接访问第一存储单元20来下载固件升级数据,而不需要通过处理器10或处理器10进行对该访问的干预操作。处理器10和主板接口40之间通过uart串口通信来检测待升级设备主板固件信息,当处理器10检测到设备主板需要升级时,主板接口40通过usb2.0接口和处理器10通信并将存储在第一存储单元20中的固件升级数据下载到待升级主板中,本实施例中的处理器10支持带有dma请求和确认的sram及外部设备,不需要干预待升级主板下载固件升级数据的过程,可以有效提高固件升级效率,节省处理器10的算力。

47.其中一个实施例中,本技术的支持网络升级的电路还包括第二存储单元30,第二存储单元30与处理器10连接,第二存储单元30包括存储芯片例如eeprom芯片,第二存储单元30用于存储处理器10的预设配置信息,预设配置信息例如处理器10需要的驱动程序;主板接口40与处理器10连接,处理器10通过主板接口40检测待升级主板的固件信息,固件信息例如是待升级主板的型号、固件版本等信息;以太网模块电路50设置于主板接口40和处理器10之间

48.具体的,请参阅图2,以太网模块电路50包括以太网收发器芯片501,晶振电路502、供电电路503和led控制电路504,晶振电路502与以太网收发器芯片501连接,用于给以太网收发器芯片501提供时钟信号,供电电路503与以太网收发器芯片501连接,用于给以太网收发器芯片501提供正常工作必要的电路配置,比如定义以太网收发器芯片501内部标准电流的电路配置,led控制电路504与以太网收发器芯片501连接,用于通过配置led的显示模式指示以太网模块电路50的工作状态。

49.其中一个实施例中,以太网模块电路50还包括第一电阻r1、第二电阻r2、第三电阻r3和第四电阻r4,请参阅图2,以太网收发器芯片501的rmii标准信号接口包括txd0引脚、rxd0引脚、txd1引脚和rxd1引脚,第一电阻r1连接在以太网收发器芯片501的txd0引脚和处理器10的rxd0引脚之间,第二电阻r2连接在以太网收发器芯片501的txd1引脚和处理器10的rxd1引脚之间,用于以太网收发器芯片501向处理器10传输rmii数据信号。第三电阻r3连接在以太网收发器芯片501的rxd0引脚和处理器10的txd0引脚之间,第四电阻r4连接在以太网收发器芯片501的rxd1引脚和处理器10的txd1引脚之间,用于以太网收发器芯片501接收处理器10的rmii数据信号。

50.其中一个实施例中,以太网模块电路50还包括第五电阻r5、第六电阻r6、第七电阻r7和第八电阻r8,请参阅图2,第五电阻r5连接在以太网收发器芯片501的使能引脚txen引脚和处理器10的txen引脚之间,用于传输使能信号或者检测信号。第六电阻r6连接在以太网收发器芯片501的载波侦听引脚rxdv引脚和处理器10的rxdv引脚之间,用于在以太网收发器芯片501在rmii模式下指示载波侦听和接收数据有效,当接收介质处于非空闲状态时,以太网收发器芯片501依据与工作模式相关的标准异步确认并通过载波检测来保证接收数据有效。第七电阻r7连接在以太网收发器芯片501的数据状态指示引脚rxer引脚和处理器10的rxer引脚之间,用于表示数据传输的状态,以太网收发器芯片501通过rxer引脚输出端来标识当前以太网收发器芯片501到帧传输过程中曾出现的错误。第八电阻r8的一端连接以太网收发器芯片501的时序参考引脚rxclk引脚,第八电阻r8的另一端和第一电容c1的一端共同连接处理器10的refclk引脚,第一电容c1的另一端接地,refclk引脚提供一个连续

时钟为以太网收发器芯片501和处理器10之间的数据通信提供时序参考,这里由处理器10的mac层提供时序参考,也可以由外部时钟源提供。以太网收发器芯片501的复位引脚reset_n引脚、管理信息引脚mdio引脚、管理信息时钟引脚mdc引脚分别和处理器10的reset引脚、mdio引脚、mdc引脚连接,处理器10通过reset引脚控制以太网收发器芯片501的复位,处理器10通过mdio引脚传输管理信息,处理器10通过mdc引脚为mdio引脚传输管理信息提供时钟参考。

51.其中一个实施例中,请参阅图3,主板接口40包括mdi接口(快速以太网100base-t定义的与介质有关接口,media dependent interface)、iic接口(多向控制总线接口)、uart接口(通用异步收发,universal asynchronous receiver/transmitter)和usb2.0(通用串行总线,universal serial bus)接口,其中mdi接口与所述以太网模块电路50连接,mdi接口包括mdi_rn引脚、mdi_rp引脚、mdi_tn引脚和mdi_tp引脚,用于待升级主板向以太网模块电路50传输mdi网络信号,iic接口与处理器10连接,iic接口包括i2c_sda引脚和i2c_scl引脚,用于待升级主板和处理器10之间进行iic通信,uart接口包括uart_tx引脚和uart_rx引脚,用于待升级主板和处理器10通信使处理器10检测到固件信息,usb2.0接口包括usb_dp引脚和usb_dm引脚,usb2.0与处理器10连接,用于待升级主板通过处理器10下载固件升级数据以完成自身的固件升级。

52.其中一个实施例中,以太网收发器芯片501被配置为rmii模式。

53.具体地,以太网收发器芯片501的与介质有关接口包括mdi_rn引脚、mdi_rp引脚、mdi_tn引脚和mdi_tp引脚,分别主板接口40的与介质有关接口引脚对应连接,参阅图3,主板接口40包括mdi_rn引脚、mdi_rp引脚、mdi_tn引脚和mdi_tp引脚,用于以太网收发器芯片501接收来自待升级主板的mdi网络信号。以太网收发器芯片501通过硬件配置或者软件配置被配置为媒体独立接口模式,通过将来自主板接口40传输的网络信号在芯片内部自动装换成rmii(与介质无关接口,reduced media independent interface)标准信号并传输给处理器10,即以太网收发器芯片501被配置为rmii模式,这里可以采用硬件配置或者软件配置。处理器10就可以通过网络通讯检测待升级主板的固件升级数据推送,进而通过网络通讯下载待升级主板所需要的固件升级数据,利用待升级设备的网络信号来隔空获取固件升级数据,电路接口集成度高易于实现,针对不具有智能操作系统的待升级设备灵活配套使用,达到网络升级固件的目的。

54.其中一个实施例中,主板接口40和处理器10之间的通信方式包括iic总线通信、uart通信、usb2.0通信,请参阅图2、3,处理器10通过uart通信检测待升级主板的固件信息,并且通过网络下载固件升级数据到第一存储单元20,第一存储单元20的存储模块例如是flash存储芯片,采用flash存储芯片存储固件升级数据,flash存储芯片同样容量占芯片的面积更小且成本低,对于存储固件升级数据这种数据占用存储空间较多的使用场景更加适合。请参阅图4,第一存储单元20包括flash存储芯片、第九电容和第二电阻,所述flash存储芯片和处理器10通过spi(串行外围设备接口,serial peripheral interface)接口通信,第九电阻r9串接在flash存储芯片的sck引脚和处理器10之间,flash存储芯片的gnd引脚与第二电容c2的一端连接且接地,第二电容c2的另一端与flash存储芯片的vcc引脚连接且接电源,待升级主板检测到固件升级信息并且通过usb2.0通信方式下载存储在flash存储芯片中的固件升级数据来完成自身的固件升级,采用外部的存储单元存储固件升级数据,待

升级主板通过与处理器10通讯下载升级,不需要占用待升级设备的存储空间,使得待升级设备升级固件更加简便实用。

55.其中一个实施例中,第二存储单元30可以包括eeprom芯片,请参阅图5,第二存储单元30包括eeprom芯片、第十电阻r10和第三电容c3,eeprom芯片与处理器10通过iic通信连接,第十电阻r10的一端与eeprom芯片的测试引脚wp引脚连接,第十电阻r10的另一端接电源vdd,与eeprom芯片的地址引脚a0引脚、a1引脚、a2引脚以及gnd引脚共接地,第三电容c3的一端接eeprom芯片的vcc引脚,第三电容c3的另一端接地,其中eeprom芯片的wp引脚被配置为高电平以开启eeprom芯片的写入保护功能,eeprom芯片属于非易失性存储器,掉电可以保证存储的数据不丢失,采用单独的eeprom芯片相比于处理器自带的eeprom,芯片的擦写次数更多,稳定性更高。

56.本技术实施例还提供了一种电子装置,用于网络升级固件,包括上述任一项实施例中的支持网络升级的电路。

57.以上所述实施例仅用以说明本技术的技术方案,而非对其限制;尽管参照前述实施例对本技术进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本技术各实施例技术方案的精神和范围,均应包含在本技术的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1