一种芯片自毁装置的制作方法

1.本实用新型属于电子信息安全技术领域,尤其是涉及一种芯片自毁装置。

背景技术:

2.随着客户对产品质量的要求不断提高,对高质量产品的防伪要求越来越高。假冒商品日益横行,导致市面上假冒伪劣商品泛滥,品牌生产企业深受其害,蒙受渗重损失,消费者在经济上承受损失,在身体健康乃至人身安全上受到伤害,严重扰乱人们的生活、社会环境,如何杜绝假冒商品已是当务之急。

3.针对假冒商品日益横行的现状,很多防伪企业也推出了一系列防伪产品。例如,对于烟酒、医药、保健品、箱包等中高端商品,通过在商品上增加具有信息识别功能强、体积小、成本低、使用方便等特点的防伪标签进行防伪,目前应用范围较广、使用量较大的防伪标签主要是无源型的nfc芯片、rfid芯片等电子标签。然而,随着电子标签的大量使用,商品启用后废弃的电子标签往往因不容易自毁,而被不法分子回收进行二次利用制作假冒商品,回收废弃电子标签的目的在于冒用电子标签芯片中的商品信息。

4.因此,急需提供一种芯片自毁装置用于防止被回收冒用。

技术实现要素:

5.本实用新型的目的在于针对现有技术中存在的不足,提供一种设计合理,结构简单,成本低廉,能够防止被回收冒用的芯片自毁装置。

6.为了实现上述目的,本实用新型采用以下技术方案:

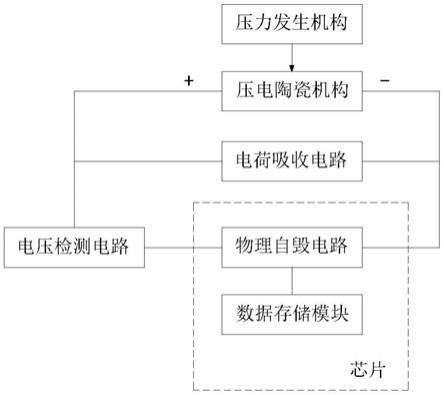

7.一种芯片自毁装置,其包括压力发生机构、压电陶瓷机构、电压检测电路、电荷吸收电路和具有物理自毁电路的芯片;

8.芯片,其内置有数据存储模块和物理自毁电路,物理自毁电路用于电导通后对数据存储模块进行物理损坏;

9.压力发生机构,其抵触连接在压电陶瓷机构上,用于对压电陶瓷机构施加压力以触发自毁信号;

10.压电陶瓷机构,用于接收自毁信号后,产生高电压输送至电压检测电路的输入端和电荷吸收电路的一端;压电陶瓷机构的负极分别电连接电荷吸收电路的另一端和物理自毁电路的输出端;

11.电压检测电路,其分别电连接压电陶瓷机构的正极和物理自毁电路的输入端,用于在检测到高电压超过阈值时对物理自毁电路进行电导通;

12.电荷吸收电路,用于吸收压电陶瓷机构自身输出的杂散电流或者外界轻微振动导致压电陶瓷机构输出的较小电压。

13.作为优选,所述压电陶瓷机构包括一个以上压电陶瓷片,每个压电陶瓷片均包括绝缘座、陶瓷薄片、正极压电片、负极压电片和两个高压导线,陶瓷薄片为采用陶瓷作为压电材料制作而成的薄片,正极压电片设于陶瓷薄片的一表面作为正极面,负极压电片设于

陶瓷薄片的另一表面作为负极面,陶瓷薄片通过负极面嵌置在绝缘座上设有的安装槽内,两个高压导线的一端分别与正极面和负极面电连接,两个高压导线的另一端分别延伸出安装槽外。

14.作为优选,所述压电陶瓷机构包括两个以上压电陶瓷片,两个以上压电陶瓷片并联设置,防止单个压电陶瓷片失效。

15.作为优选,所述电压检测电路至少包括二极管,二极管的正极与压电陶瓷机构的正极电连接,二极管的负极与物理自毁电路的输入端电连接。

16.作为优选,所述电荷吸收电路至少包括电容,电容的一端与压电陶瓷机构的正极电连接,电容的另一端与压电陶瓷机构的负极电连接,电容的击穿电压大于二极管的正向导通压降。

17.作为优选,所述压力发生机构为由硬质材料加工成型的按压件。

18.作为优选,所述芯片为无源型的nfc芯片或者rfid芯片。

19.本实用新型采用以上技术方案,当压力发生机构被压下时,压力发生机构对压电陶瓷机构施加压力,压电陶瓷机构产生瞬间高压电流,高压电流从压电陶瓷机构的正极通过高压导线同时输送到电压检测电路的输入端和电荷吸收电路的一端,当高压电流流经电压检测电路,电压检测电路检测到高压电流对应的高电压超过阈值(即,高电压大于二极管的正向导通压降)时,对物理自毁电路进行电导通,物理自毁电路电导通后对芯片的数据存储模块进行物理损坏,从而实现芯片自毁,使得芯片自毁后无法被相应的芯片阅读器读取到芯片内的信息,以防止芯片被回收二次利用进行商品假冒,达到防伪的目的;同时,高压电流输送到电荷吸收电路的一端时,当高压电流对应的高电压超过电荷吸收电路的击穿电压(即,高电压大于电容的击穿电压)时,电容被击穿,以将芯片短路。此外,由于电压检测电路的二极管具有一定的正向导通压降,压电陶瓷机构自身输出的杂散电流或者外界轻微振动导致压电陶瓷机构输出较小的电压时,不会使二极管和物理自毁电路电导通,杂散电流或较小电压电荷均能够被电容c所吸收,从而不会误触发芯片自毁。

附图说明

20.为了更清楚地说明本实用新型实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,现针对附图进行如下说明:

21.图1为本实用新型芯片自毁装置的结构示意图;

22.图2为本实用新型压电陶瓷机构的一种实施方式结构示意图;

23.图3为本实用新型压电陶瓷机构的另一种实施方式结构示意图;

24.图4为本实用新型实施例1中芯片自毁装置的结构示意图;

25.图5为本实用新型实施例2中芯片自毁装置的使用方法示意图;

26.图6为本实用新型实施例3中芯片自毁装置的使用方法示意图;

27.图7为本实用新型实施例4中芯片自毁装置的使用方法示意图。

具体实施方式

28.以下所描述的实施例仅是本实用新型一部分实施例,并不代表与本实用新型相一致的所有实施例。现结合附图,对示例性实施例进行如下说明:

29.如图1-7之一所示,本实用新型的芯片自毁装置,其包括压力发生机构、压电陶瓷机构、电压检测电路、电荷吸收电路和具有物理自毁电路的芯片;

30.芯片,为无源型的nfc芯片或者rfid芯片,其内置有数据存储模块和物理自毁电路,物理自毁电路用于电导通后对数据存储模块进行物理损坏;

31.压力发生机构,其抵触连接在压电陶瓷机构上,用于对压电陶瓷机构施加压力以触发自毁信号;

32.压电陶瓷机构,用于接收自毁信号后,产生高电压输送至电压检测电路的输入端和电荷吸收电路的一端;压电陶瓷机构的负极分别电连接电荷吸收电路的另一端和物理自毁电路的输出端;

33.电压检测电路,其分别电连接压电陶瓷机构的正极和物理自毁电路的输入端,用于在检测到高电压超过阈值时对物理自毁电路进行电导通;

34.电荷吸收电路,用于吸收压电陶瓷机构自身输出的杂散电流或者外界轻微振动导致压电陶瓷机构输出的较小电压。

35.如图2所示,为本实用新型压电陶瓷机构的一种实施方式结构示意图;在该实施方式中,压电陶瓷机构包括一个以上压电陶瓷片10。

36.每个压电陶瓷片10均包括绝缘座11、陶瓷薄片12、正极压电片13、负极压电片14和两个高压导线15、16,陶瓷薄片12为采用陶瓷作为压电材料制作而成的薄片,正极压电片13设于陶瓷薄片12的一表面作为正极面,负极压电片14设于陶瓷薄片12的另一表面作为负极面,陶瓷薄片12通过负极面嵌置在绝缘座11上设有的安装槽内,两个高压导线15的一端分别与正极面和负极面电连接,两个高压导线15、16的另一端分别延伸出安装槽外。

37.如图3所示,为本实用新型压电陶瓷机构的另一种实施方式结构示意图;在该实施方式中,压电陶瓷机构包括两个以上压电陶瓷片10,两个以上压电陶瓷片10并联设置,防止单个压电陶瓷片失效。

38.每个压电陶瓷片10均包括绝缘座11、陶瓷薄片12、正极压电片13、负极压电片14和两个高压导线15,陶瓷薄片12为采用陶瓷作为压电材料制作而成的薄片,正极压电片13设于陶瓷薄片12的一表面作为正极面,负极压电片14设于陶瓷薄片12的另一表面作为负极面,陶瓷薄片12通过负极面嵌置在绝缘座11上设有的安装槽内,两个高压导线15、16的一端分别与正极面和负极面电连接,两个高压导线15、16的另一端分别延伸出安装槽外。

39.本实用新型的工作原理是:

40.当压力发生机构被压下时,压力发生机构对压电陶瓷机构施加压力,压电陶瓷机构产生瞬间高压电流,高压电流从压电陶瓷机构的正极通过高压导线15同时输送到电压检测电路的输入端和电荷吸收电路的一端,当高压电流流经电压检测电路,电压检测电路检测到高压电流对应的高电压u超过阈值(即,高电压大于二极管d的正向导通压降)时,对物理自毁电路进行电导通,物理自毁电路电导通后对芯片的数据存储模块进行物理损坏,从而实现芯片自毁,使得芯片自毁后无法被相应的芯片阅读器读取到芯片内的信息,以防止芯片被回收二次利用进行商品假冒,达到防伪的目的;同时,高压电流输送到电荷吸收电路的一端时,当高压电流对应的高电压u超过电荷吸收电路的击穿电压(即,高电压大于电容的击穿电压)时,电容被击穿,以将芯片短路。此外,由于电压检测电路的二极管具有一定的正向导通压降,压电陶瓷机构自身输出的杂散电流或者外界轻微振动导致压电陶瓷机构输

出较小的电压时,不会使二极管和物理自毁电路电导通,杂散电流或较小电压电荷均能够被电容c所吸收,从而不会误触发芯片自毁。

41.实施例1

42.如图4所示,在上述结构基础上,电压检测电路至少包括二极管d,二极管d的正极与压电陶瓷机构的正极电连接,二极管d的负极与物理自毁电路的输入端电连接。电荷吸收电路至少包括电容c,电容c的一端与压电陶瓷机构的正极电连接,电容c的另一端与压电陶瓷机构的负极电连接,电容c的击穿电压大于二极管d的正向导通压降。压力发生机构为由硬质材料加工成型的按压件。

43.在该实施例中,本实用新型对电压检测电路和电荷吸收电路进行了极简化,从而大大降低防伪成本,提高了商品市场竞争力。

44.实施例2

45.如图5所示,一种芯片自毁装置的使用方法,将上述任一项的芯片自毁装置设置在容器瓶的瓶盖内,当旋转打开瓶盖时,借助旋转力带动压力发生机构对压电陶瓷机构施加压力,以触发自毁信号。

46.实施例3

47.如图6所示,一种芯片自毁装置的使用方法,将上述任一项的芯片自毁装置设置在容器盒的锁体中,压力发生机构设于容器盒的开锁按钮内端,当挤压开锁按钮打开锁体时,借助开锁的挤压力带动压力发生机构对压电陶瓷机构施加压力,以触发自毁信号。

48.实施例4

49.如图7所示,一种芯片自毁装置的使用方法,将上述任一项的芯片自毁装置设置在包装盒的按压式撕口处,当按压撕口打开包装盒时,借助按压力带动压力发生机构对压电陶瓷机构施加压力,以触发自毁信号。

50.以上仅为本实用新型的较佳具体实施例,并不用以限制本实用新型保护范围;凡本技术领域中技术人员依本实用新型的构思在现有技术的基础上通过逻辑分析、推理或者有限的实验所做的均等变化、修改、替换和变型,皆应在由权利要求书所确定的保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1