检测处理器的指令流水线中的重复模式以减少重复取回的制作方法

本公开的技术涉及计算机处理器(“处理器”),更具体地,涉及将指令取回到要被执行的处理器的指令流水线中。

背景技术:

1、微处理器,也称为“处理器”,执行针对各种应用的计算任务。微处理器包括中央处理单元(cpu),其包括一个或多个处理器核,也称为“cpu核”。cpu执行计算机程序指令(“指令”),也称为“软件指令”,以基于数据执行操作并生成结果,结果是所产生的值。cpu可以包括指令流水线,其中一系列指令被取回到一个或多个指令流水线中,每个指令流水线具有一定数目的处理级以执行朝向其执行的任务。与在处理下一条指令之前顺序处理并完全执行每条指令相反,这允许在同一时间和不同级中处理多条指令,以提高指令处理吞吐量。在这方面,cpu可以包括指令取回电路,其将指令取回到指令流水线中。指令随后在译码级中被译码,并在用于执行的其他流水线级中被进一步处理。指令最终在指令流水线的执行级被执行。作为指令取回电路取回指令流水线中处理的指令的结果,cpu中消耗了功率。

2、作为取回和处理要被执行的指令的结果,重复模式可以在cpu的指令流水线中被接收。例如,要被执行的所取回的指令可以是编程构造,例如软件循环。在退出循环之前,可以重新执行软件循环多次,从而使得循环中的指令被重复地取回和处理。不仅可能在指令流水线中重复、取回和处理相同的指令,而且处理这些指令所消耗的数据也可能导致指令流水线中的数据的重复。将指令到要被处理和执行的cpu的指令流水线中的每一次重复取回都消耗cpu的指令取回电路中的功率。

技术实现思路

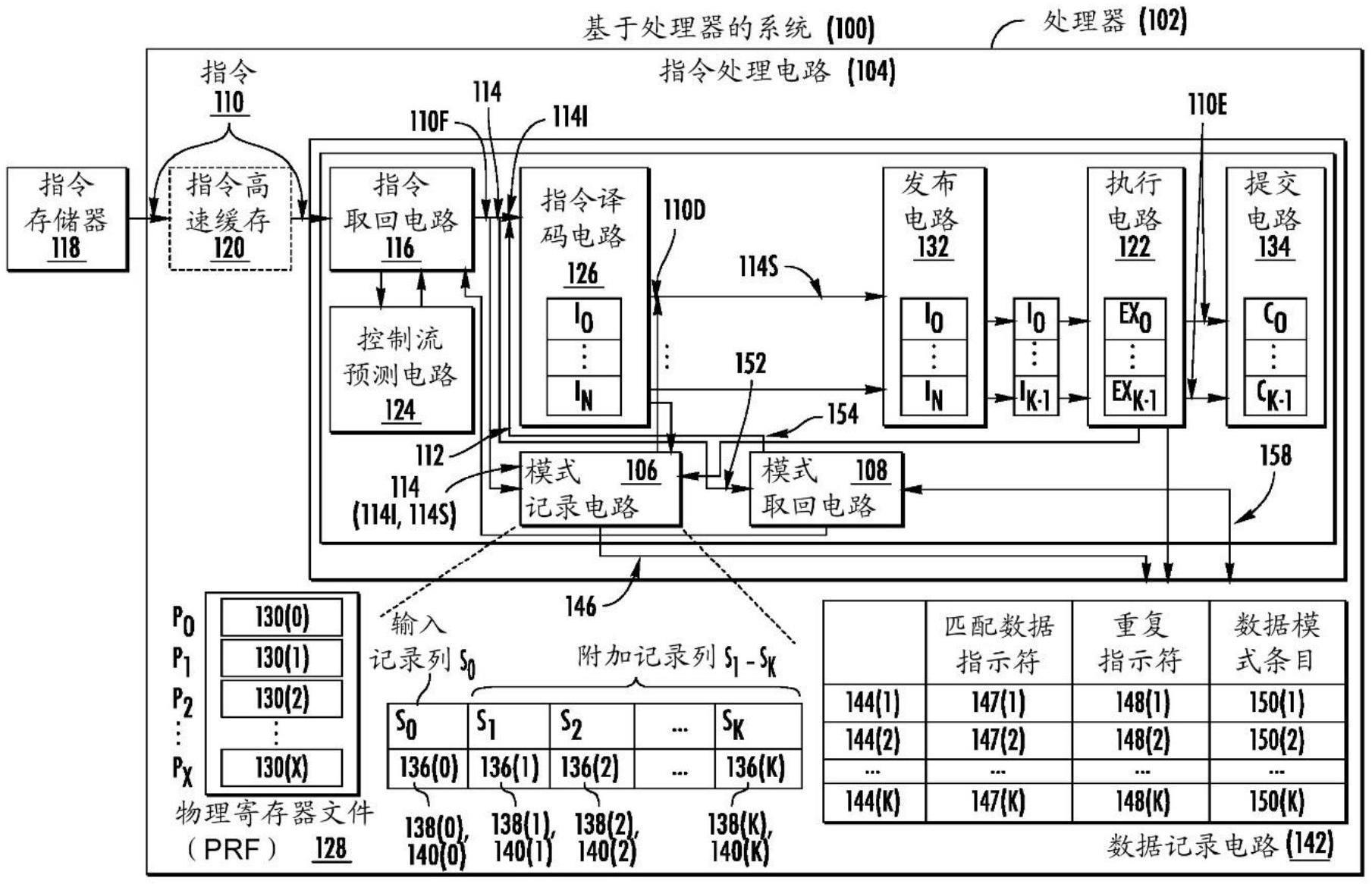

1、本文公开的示例性方面包括检测处理器的指令流水线中的重复模式以减少重复取回。该处理器包括指令处理电路,该指令处理电路被配置为将指令取回到指令流水线中作为将要作为指令流水线的一部分而被处理和执行的指令数据流的一部分。由所取回的指令中的源操作数指定的数据也被取回到指令流水线中,并用于执行指令流水线中的数据流中的指令。取回到指令流水线中的指令和/或其源数据可以重复(即,被重复地取回到指令流水线中)。在示例性方面,期望检测在指令流水线中出现的数据(例如,指令和/或源数据)的这些重复模式,使得这样的数据的先前记录的模式可以被插入到指令流水线中,而不必重新取回该数据。

2、在示例性方面,处理器包括模式记录电路。该模式记录电路被配置为接收指令流水线中的数据流(例如,指令和/或源数据)中的信息。在一个示例中,模式记录电路包括先进先出(fifo)表电路。模式记录电路包含输入记录列和多个附加相邻记录列。记录列的数目限定模式记录电路的宽度。随着新数据出现在数据流中,模式记录电路被配置为将来自数据流的下个传入数据顺序地记录到模式记录电路的输入记录列的下个输入条目中,并且然后将先前记录的数据存储(例如,移动)到模式记录电路的相邻记录列的相邻条目中。因此,如果数据在数据流中以等于或小于模式记录电路的宽度的频率重复,记录在模式记录电路中的输入记录列中的传入数据将与先前移动到附加记录列中的数据的先前出现匹配。输入记录列和包括匹配数据的附加记录列之间的距离是数据流中数据的重现(即,重复)之间的距离。附加记录列还包括相应的频率指示符,其由模式记录电路针对一个或多个附加记录列中的数据与输入记录列中记录的新输入数据之间的所检测到的匹配而更新。

3、以此方式,指示重复数据模式的出现的频率指示符可以由处理器中的模式取回电路而查询(consult),以确定指令流水线中的数据流中出现的潜在数据模式。检测处理器的指令流水线中的重复模式可以用于减少重复的重新取回。例如,模式取回电路可以被配置为接收取回到指令流水线中的新数据的指示。模式取回电路可以被配置为查询先前针对新取回数据而记录的频率指示符,以确定新取回数据是先前记录的重复数据模式的开始的可能性。如果新取回数据被确定为先前记录的重复数据模式的开始,模式取回电路被配置为将来自先前记录的重复数据模式的数据插入到指令流水线中,使得新数据的取回可以暂时被禁用。

4、就此而言,在一个示例性方面,公开了一种处理器,其包括指令处理电路和模式记录电路,该指令处理电路被配置为将数据取回到指令流水线中作为数据流,该模式记录电路包括输入记录列和一个或多个附加输入记录列,该输入记录列包括输入数据条目,该一个或多个附加输入记录列各自包括数据条目和频率指示符。模式记录电路被配置为从数据流接收下个传入数据,并且在输入记录列中的输入数据条目中存储下个传入数据。响应于从数据流接收到下个传入数据,模式记录电路还被配置为将来自输入记录列的输入数据条目的下个传入数据存储到一个或多个附加记录列中与输入记录列相邻的附加记录列,并将该一个或多个附加记录列的每个数据条目中的数据存储到该一个或多个附加记录列中的相应的相邻附加记录列的数据条目中。响应于存储在一个或多个附加记录列中的附加记录列的数据条目中的数据与下个传入数据匹配,该模式记录电路还被配置为将该附加记录列的频率指示符更新为指示该数据流中的下个传入数据的重复频率的重复频率状态。

5、在另一示例性方面,公开了一种检测处理器的指令流水线中的重复模式的方法。该方法包括从取回到指令流水线中的数据流接收下个传入数据,并将下个传入数据存储在模式记录电路中的输入记录列中的输入数据条目中。该方法还包括将来自输入记录列的输入数据条目的下个传入数据存储到模式记录电路中的一个或多个附加记录列中与输入记录列相邻的附加记录列,将该一个或多个附加记录列的每个数据条目中的数据存储到该一个或多个附加记录列中的相应的相邻附加记录列中的数据条目中,并确定存储在该一个或多个附加记录列中的附加记录列的数据条目中的数据是否与传入数据匹配。响应于存储在一个或多个附加记录列中的附加记录列的数据条目中的数据与传入数据匹配,该方法还包括将附加记录列的频率指示符更新为指示数据流中的传入数据的重复频率的重复频率状态。

6、本领域技术人员将理解本公开的范围,并在阅读以下与附图相关联的优选实施例的详细描述之后了解其附加方面。

技术特征:

1.一种处理器,包括:

2.根据权利要求1所述的处理器,其中每个附加记录列基于其与所述输入记录列的距离而被分配给所述数据流中的相应数据重复频率。

3.根据权利要求1所述的处理器,其中所述指令处理电路被配置为将多个指令取回到所述指令流水线中作为所述数据流。

4.根据权利要求1所述的处理器,其中所述指令处理电路被配置为将用于处理一个或多个指令的多个源数据取回到所述指令流水线中作为所述数据流。

5.根据权利要求1所述的处理器,其中所述模式记录电路包括先进先出(fifo)表电路,

6.根据权利要求1所述的处理器,其中:

7.根据权利要求1所述的处理器,还包括耦合到所述模式记录电路的数据记录电路,所述数据记录电路包括:

8.根据权利要求7所述的处理器,还包括模式取回电路,所述模式取回电路被配置为:

9.根据权利要求8所述的处理器,其中所述模式取回电路还被配置为,响应于包含所匹配的所述数据指示符的所述数据记录条目的所述重复指示符条目中的所述重复指示符超过所述数据模式重复阈值:

10.根据权利要求8所述的处理器,其中所述模式取回电路被配置为:

11.根据权利要求1所述的处理器,其中:

12.根据权利要求7所述的处理器,其中:

13.一种检测处理器的指令流水线中的重复模式的方法,包括:

14.根据权利要求13所述的方法,还包括数据记录电路,所述数据记录电路被配置为:

15.根据权利要求14所述的方法,进一步包括:

技术总结

本文公开的示例性方面包括检测处理器的指令流水线中的重复模式以减少重复取回。处理器包括模式记录电路,模式记录电路被配置为接收指令流水线中的数据流(例如,指令或消耗的数据)中的信息。模式记录电路包括先进先出(FIFO)表电路,其包含输入记录列和多个附加的相邻记录列。随着数据流中出现新数据,数据记录电路被配置为将来自数据流的下个传入数据顺序地记录到输入记录列的下个输入条目中,然后将先前记录的数据移动到相邻记录列的相邻条目中。输入记录列和具有匹配数据的附加记录列之间的距离是数据流中数据重复出现之间的距离。

技术研发人员:J·W·小哈斯金斯

受保护的技术使用者:微软技术许可有限责任公司

技术研发日:

技术公布日:2024/1/11

- 还没有人留言评论。精彩留言会获得点赞!