用于加速器中多个并行数据路径通道的存储体式存储器架构的制作方法

背景技术:

1、扩展深度神经网络(dnn)加速器时,会出现常见的存储器带宽问题。缩放加速器的计算吞吐量的一种方法是通过缩放独立数据路径的数目来增加数据并行度,每个独立数据路径对数据的不同部分(例如,矩阵中的不同行或不同的输入向量)并行操作。然而,如果这些数据路径中的每一个都必须从单个逻辑统一的存储器结构访问数据,那么支持对该结构的越来越多的独立访问的复杂度变得过高地昂贵。

技术实现思路

1、提供本

技术实现要素:

是为了以简化形式介绍一组概念,这些概念将在下面的具体实施方式中进一步描述。本发明内容不旨在标识所要求保护的主题的关键特征或必要特征,也不旨在用作确定所要求保护的主题的范围的辅助。

2、一个示例实现涉及一种与加速器一起使用的存储体式存储器(banked memory)结构。该存储体式存储器结构可以包括多个本地存储器,其中多个本地存储器包括存储器解码器。该存储体式存储器结构可以包括多个计算单元;以及多个通道,其中多个通道中的每个通道与多个本地存储器中的单独的本地存储器和多个计算单元中的一个计算单元配对;并且其中存储器解码器接收用于加速器的数据,其中数据包括多个向量,并且多个向量中的每个向量由存储器解码器分配给多个通道中的一个通道,用于由与通道相关联的计算单元进行处理。

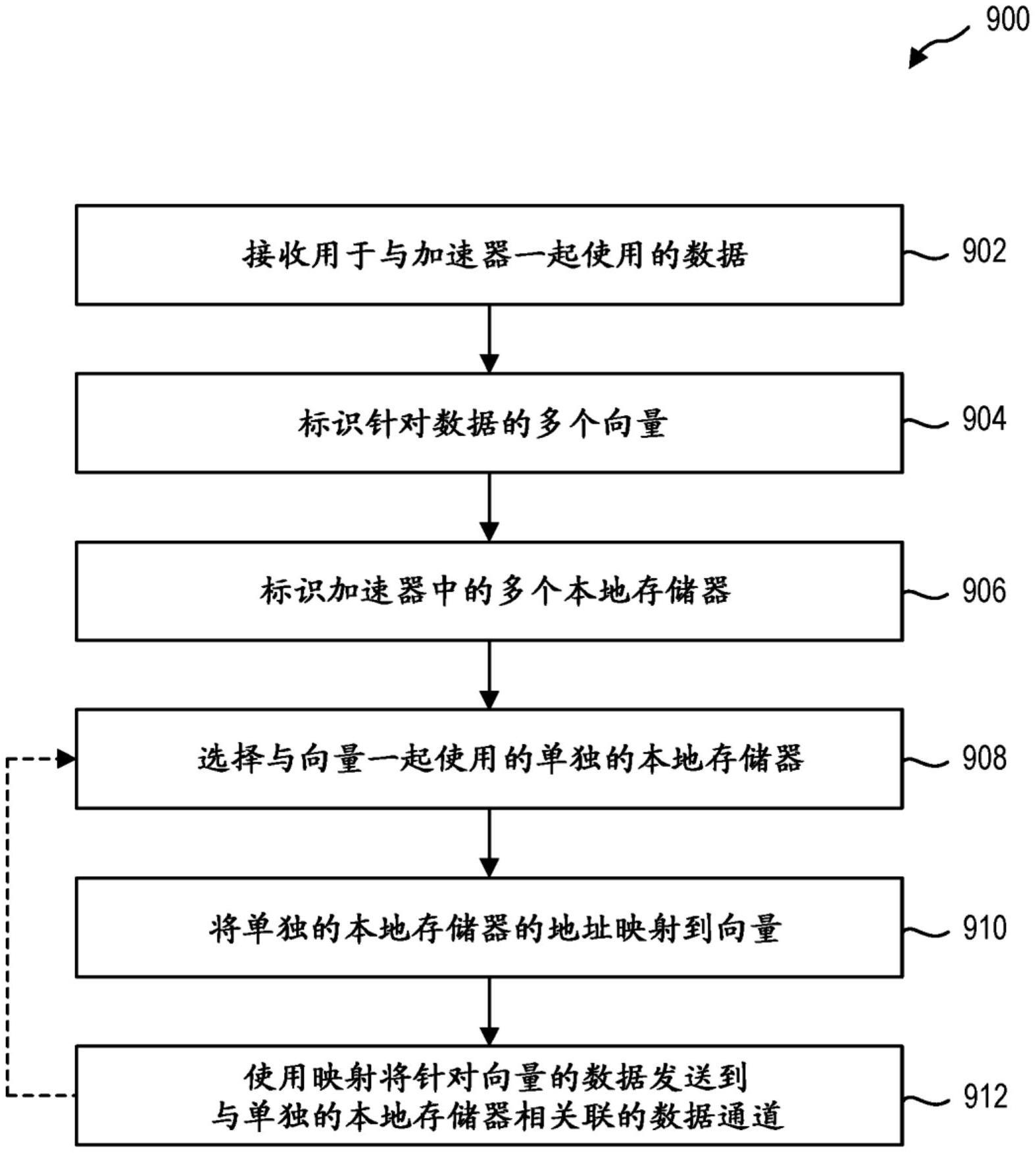

3、另一示例实现涉及一种由加速器的存储器解码器执行的方法。该方法可以包括:接收与用于加速器一起使用的数据。该方法可以包括:标识针对数据的多个向量。该方法可以包括:标识加速器中的多个本地存储器。该方法可以包括:针对多个向量中的每个向量:选择多个本地存储器中的单独的本地存储器以用于与向量一起使用;将单独的本地存储器的地址映射到向量;以及使用映射以将针对向量的数据发送到与单独的本地存储器相关联的数据通道。

4、另一示例实现涉及一种设备。该设备可以包括:一个或多个处理器;与一个或多个处理器进行电子通信的存储器;以及存储在存储器中的指令,指令可由一个或多个处理器执行以:接收与加速器一起使用的数据;标识数据的多个向量;标识加速器中的多个本地存储器;针对多个向量中的每个向量:选择多个本地存储器中的单独的本地存储器以与向量一起使用;将单独的本地存储器的地址映射到向量;以及使用映射将向量的数据发送到与单独的本地存储器相关联的数据通道。

技术特征:

1.一种用于与加速器一起使用的存储体式存储器结构,包括:

2.根据权利要求1所述的存储体式存储器结构,其中每个计算单元被配置为处理被提供给该计算单元的所述数据而不访问来自其他通道的数据或与所述其他通道共享所述数据。

3.根据权利要求1所述的存储体式存储器结构,其中每个计算单元被配置为将所述数据写入与所述通道相关联的所述单独的本地存储器,并且从与所述通道相关联的所述单独的本地存储器读取所述数据,并且

4.根据权利要求1所述的存储体式存储器结构,其中所述存储器解码器被配置为使用存储器地址策略,以通过迭代通过所述多个向量中的每个向量来将所述多个向量中的每个向量映射到所述单独的本地存储器的存储器地址,并且在每次迭代中,所述存储器解码器顺序地将所述多个向量中的每个向量映射到所述多个本地存储器中的下一单独的本地存储器。

5.根据权利要求1所述的存储体式存储器结构,其中所述多个计算单元中的每个计算单元被配置为在被分配给每个计算单元的所述数据上并行操作。

6.根据权利要求1所述的存储体式存储器结构,其中所述单独的本地存储器包括向量寄存器文件(vrf),并且每个通道包括矩阵-向量乘法器(mvm)。

7.根据权利要求1所述的存储体式存储器结构,其中所述加速器是深度神经网络(dnn)加速器。

8.一种由加速器的存储器解码器执行的方法,包括:

9.根据权利要求8所述的方法,还包括:

10.根据权利要求9所述的方法,其中选择针对所述向量的所述单独的本地存储器是以所述多个本地存储器的顺序的次序发生的。

11.根据权利要求8所述的方法,其中多个本地存储器的子集被用于选择针对所述向量的所述单独的本地存储器。

12.根据权利要求8所述的方法,其中每个单独的本地存储器与多个计算单元中的计算单元相关联,并且所述计算单元在针对所述单独的本地存储器的所述数据上并行地执行处理。

13.根据权利要求8所述的方法,其中所述多个本地存储器中的每个所述单独的本地存储器针对独立的并发可执行的存储器访问模式而被访问。

14.根据权利要求8所述的方法,其中所述单独的本地存储器是向量寄存器文件(vrf),并且所述加速器是深度神经网络(dnn)加速器。

15.一种设备,包括:

技术总结

本公开涉及用于将存储体式存储器结构与加速器一起使用的设备和方法。这些设备和方法可以对加速器的数据路径和存储器中的数据流进行分段和隔离。这些设备和方法可以为每个数据通道提供其自己的寄存器存储器库。这些设备和方法可以使用存储器地址解码器来将局部变量放置在适当的存储器库中。

技术研发人员:S·S·杨,S·K·莱因哈特,耿慧

受保护的技术使用者:微软技术许可有限责任公司

技术研发日:

技术公布日:2024/1/12

- 还没有人留言评论。精彩留言会获得点赞!