存储器延迟感知GPU架构的制作方法

背景技术:

1、用于常规处理系统的平台包括中央处理单元(cpu)、图形处理单元(gpu)、一个或多个存储器模块(诸如动态随机存取存储器,或dram)和支持这些实体之间的通信的总线。在一些情况下,平台被实现为单片处理架构,诸如片上系统(soc)。分布式架构提供单片处理架构的替代方案,其中经由高性能互连以协调方式操作物理或逻辑上分开的处理单元。分布式架构的一个示例是小芯片架构,该小芯片架构获得在较小节点处制造处理系统的一些部分的优点,同时如果其他部分不受益于较小节点的减小的规模,则允许在具有较大尺寸的节点处制造其他部分。减少由单片soc架构或小芯片架构使用的存储器模块的延迟改善了在处理系统上执行的应用程序的性能。然而,较低延迟存储器模块导致较高的成本并且可以消耗附加的面积。因此,在选择将在处理系统中实现的存储器的类型时要考虑性能-成本-面积折衷。

技术实现思路

技术特征:

1.一种装置,包括:

2.根据权利要求1所述的装置,其中所述存储器访问特性指示所述应用程序的延迟敏感性。

3.根据权利要求1或权利要求2所述的装置,其中所述资源管理器响应于存储器访问请求具有较低程度的局部性或不规则的存储器访问模式来分配所述第一存储器部分。

4.根据权利要求3所述的装置,其中所述资源管理器响应于所述存储器访问请求具有相对较高程度的局部性或规则的存储器访问模式来分配所述第二存储器部分。

5.根据权利要求3所述的装置,其中基于包括在对应的程序代码中的提示来确定存储器访问请求n的不规则性。

6.根据任一前述权利要求所述的装置,其中所述资源管理器被配置为监测存储器访问请求并且测量所述存储器访问请求的统计值。

7.根据权利要求6所述的装置,其中所述统计值表示所监测的存储器访问请求的高速缓存未命中率或行缓冲器未命中率。

8.根据权利要求6所述的装置,其中所述资源管理器被配置为基于所述统计值来分配或重新分配所述第一存储器部分或所述第二存储器部分。

9.根据任一前述权利要求所述的装置,还包括:

10.根据权利要求1所述的装置,还包括:

11.一种方法,包括:

12.根据权利要求11所述的方法,其中选择性地分配所述第一存储器部分或所述第二存储器部分包括响应于存储器访问请求具有较低程度的局部性或不规则的存储器访问模式来分配所述第一存储器部分。

13.根据权利要求12所述的方法,其中选择性地分配所述第一存储器部分或所述第二存储器部分包括响应于所述存储器访问请求具有相对较高程度的局部性或规则的存储器访问模式来分配所述第二存储器部分。

14.根据权利要求12或权利要求13所述的方法,还包括:

15.根据任一前述权利要求所述的方法,还包括:

16.根据权利要求15所述的方法,其中测量所述统计值包括测量所监测的存储器访问请求的高速缓存未命中率或行缓冲器未命中率。

17.根据权利要求15所述的方法,还包括:

18.一种方法,包括:

19.根据权利要求18所述的方法,还包括:

20.根据权利要求18或权利要求19所述的方法,还包括:

技术总结

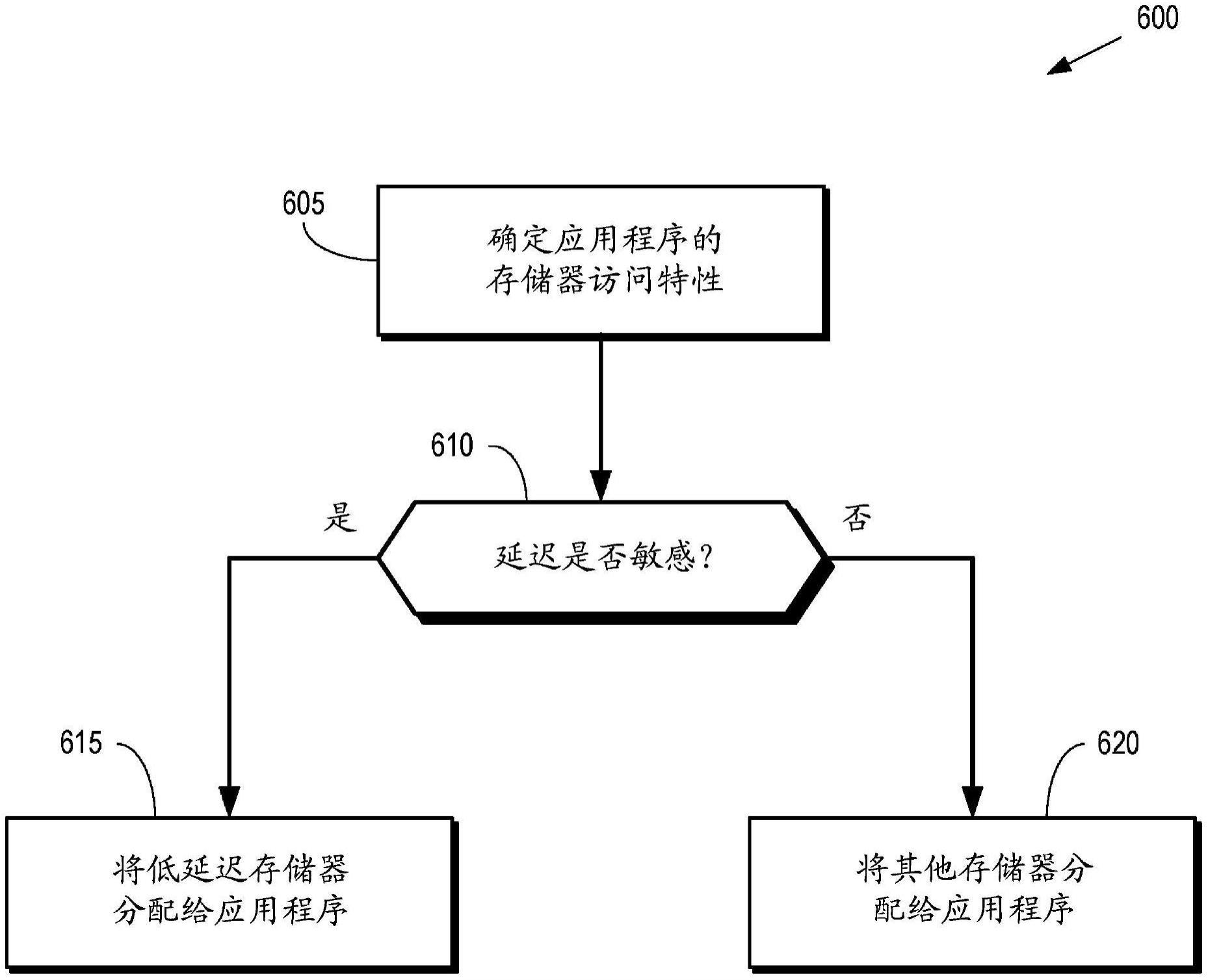

一个或多个处理单元[200,205]诸如图形处理单元(GPU)执行应用程序。资源管理器[160]基于存储器访问特性将第一存储器部分[130]或第二存储器部分[135]选择性地分配给该处理单元。该第一存储器部分具有第一延迟,该第一延迟比该第二存储器部分的第二延迟低。在一些情况下,该存储器访问特性指示延迟敏感性。在一些情况下,使用对应的程序代码中包括的提示来确定该存储器访问特性。该存储器访问特性还可以通过以下操作来确定:监测存储器访问请求、测量所监测的存储器访问请求的高速缓存未命中率或行缓冲器未命中率,以及基于该高速缓存未命中率或该行缓冲器未命中率来确定该存储器访问特性。

技术研发人员:尼缇·马登,迈克尔·L·朱,阿斯温·艾吉

受保护的技术使用者:超威半导体公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!