传输带宽失配时FPGA片间数据的传输方法与流程

传输带宽失配时fpga片间数据的传输方法

技术领域

1.本发明涉及数据传输技术领域,具体为一种传输带宽失配时fpga片间数据的传输方法。

背景技术:

2.采用宽带信号的雷达可获得很高的距离分辨率,同时为了提升雷达自身的抗干扰能力,雷达通常具备频率捷变的能力,这都对侦察干扰系统的工作带宽提出了更高的要求,为此,为了采样得到雷达数字信号,通常需要极高采样率的adc,这对高速ad数据的片间传输提出了更高的要求。

3.高速串行接口技术在fpga片间传输中发挥着巨大作用,但是基于lvds协议的传输方式单线的传输速率上限为1.6gbps,要实现高速率的ad数据传输,要多根传输线并行使用,这不仅浪费了io资源,还需采用闭环的方式保证多根线之间的同步性。

4.基于serdes协议的gth单线传输速率上限为13.1gbps,但是为了保证传输的可靠性,传输过程中需要插入k码,这不利于传输ad数据这种需要持续不间断传输的数据。

技术实现要素:

5.本发明的目的在于提供一种传输带宽失配时fpga片间数据的传输方法,以解决上述背景技术中提出的问题。

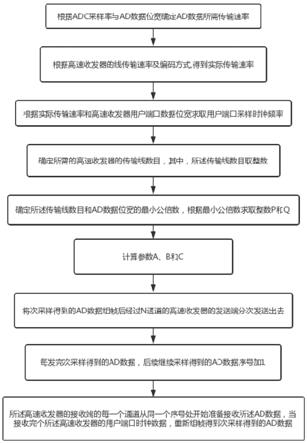

6.为实现上述目的,本发明提供如下技术方案:一种传输带宽失配时fpga片间数据的传输方法,包括如下步骤:

7.根据adc采样率与ad数据位宽确定ad数据所需传输速率;

8.根据高速收发器的线传输速率及编码方式,得到实际传输速率;

9.根据实际传输速率和高速收发器用户端口数据位宽求取用户端口采样时钟频率;

10.确定所需的高速收发器的传输线数目,其中,传输线数目取整数;

11.确定传输线数目和ad数据位宽的最小公倍数,根据最小公倍数求取整数p和q;

12.计算参数a、b和c;

13.将a

·

q次采样得到的ad数据组帧后经过n通道的高速收发器的发送端分b

·

p次发送出去;

14.每发完a

·

q次采样得到的ad数据,后续继续采样得到的ad数据序号加1;

15.高速收发器的接收端的每一个通道从同一个序号处开始准备接收ad数据,当接收完a

·

p个高速收发器的用户端口时钟数据,重新组帧得到a

·

q次采样得到的ad数据。

16.优选的,传输速率的求取公式为:

17.m=w*fs

18.其中,m为为ad数据所需传输速率,w为ad数据位宽,fs为adc采样率。

19.优选的,实际传输速率的求取公式为:

20.l'=l*0.8

21.其中,l'为实际传输速率,l为线传输速率。

22.优选的,采样时钟频率的计算公式为:

[0023][0024]

其中,g为高速收发器用户端口数据位宽,l'为实际传输速率,f

u-clk

为采样时钟频率。

[0025]

优选的,传输线数目的求取公式为:

[0026][0027]

其中,m为为ad数据所需传输速率,l'为实际传输速率,n传输线数目,表示向上取整。

[0028]

优选的,整数p和q的求取公式为:

[0029]

k=g*n*p=q*w

[0030]

其中,k为n和w的最小公倍数,g为高速收发器用户端口数据位宽,n为传输线数目,w为ad数据位宽。

[0031]

优选的,参数a、b和c的计算公式为:

[0032][0033]

其中,fs为adc采样率,g为高速收发器用户端口数据位宽,l'为实际传输速率。

[0034]

优选的,编码方式为8b10b。

[0035]

与现有技术相比,本发明的有益效果是:

[0036]

1、本发明,将a

·

q次采样得到的ad数据组帧后经过n通道的高速收发器的发送端分b

·

p次发送出去,不要多根传输线并行使用,节省了io资源,无需采用闭环的方式保证多根线之间的同步性;

[0037]

2、本发明,采用k码的形式提高整体传输的稳定性,但是传输ad数据会不间断进行数据传输。

附图说明

[0038]

图1为本发明的实施例的流程图;

[0039]

图2为本发明实施例的高速收发器的发送端ad数据(暂用递增数代替)示意图;

[0040]

图3为本发明实施例的高速收发器的发送端数据重组后gth用户端数据流图;

[0041]

图4为本发明实施例的高速收发器的接收端恢复出的ad数据(暂用递增数代替)示意图;

[0042]

图5为本发明实施例的高速收发器的接收端恢复出的ad数据图;

[0043]

图6为本发明实施例的基于gth的开环高速ad数据fpga片间传输示意图;

[0044]

图7为本发明实施例的高速收发器的发送端带宽匹配即数据重组与同步传输示意图;

[0045]

图8为本发明实施例的高速收发器的接收端带宽匹配即数据重组与同步接收示意

图。

具体实施方式

[0046]

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

[0047]

在对如下实施例进行说明之前,先对实施例中涉及的名词结合实施例进行解释说明:

[0048]

高速收发器(gth):是一种高速的信号转换的一种装置。

[0049]

请参阅图1-8,其中,图1为本发明的实施例的流程图;图2为本发明实施例的高速收发器的发送端ad数据(暂用递增数代替)示意图;图3为本发明实施例的高速收发器的发送端数据重组后gth用户端数据流图,图中,加粗的方框内的的数据为index与k码的结合,可以保证gth正常工作,实现多路gth开环同步;图4为本发明实施例的高速收发器的接收端恢复出的ad数据(暂用递增数代替)示意图;图5为本发明实施例的高速收发器的接收端恢复出的ad数据图,图中可知,可见恢复出的ad数据规律和发送端一致;图6为本发明实施例的基于gth的开环高速ad数据fpga片间传输示意图;

[0050]

图7为本发明实施例的高速收发器的发送端带宽匹配即数据重组与同步传输示意图;图8为本发明实施例的高速收发器的接收端带宽匹配即数据重组与同步接收示意图本发明提供一种技术方案:一种传输带宽失配时fpga片间数据的传输方法,包括如下步骤:

[0051]

根据adc采样率与ad数据位宽确定ad数据所需传输速率。

[0052]

在本实施例中,其中,adc采样率为6.4ghz,ad数据位宽为12bits,传输速率的求取公式为:

[0053]

m=w*fs=76.8gbps

[0054]

其中,m为为ad数据所需传输速率,w为ad数据位宽,fs为adc采样率。

[0055]

根据高速收发器的线传输速率及编码方式,得到实际传输速率。

[0056]

在本实施例中,实际传输速率的求取公式为:l'=l*0.8=6.4gbps。

[0057]

根据实际传输速率和高速收发器用户端口数据位宽求取用户端口采样时钟频率。

[0058]

在本实施例中,其中,用高速收发器用户端口数据位宽为32bits,采样时钟频率的计算公式为:

[0059][0060]

上述公式中,g为高速收发器用户端口数据位宽,l'为实际传输速率,f

u-clk

为采样时钟频率。

[0061]

确定所需的高速收发器的传输线数目,其中,传输线数目取整数。

[0062]

在本实施例中,传输线数目的求取公式为:

[0063]

[0064]

上述公式中,m为为ad数据所需传输速率,l'为实际传输速率,n传输线数目,表示向上取整。

[0065]

确定传输线数目和ad数据位宽的最小公倍数,根据最小公倍数求取整数p和q。

[0066]

在本实施例中,k=g*n*p=q*w,其中,在计算过程中,g不带入单位,计算可以得到:

[0067][0068]

计算参数a、b和c。

[0069]

在本实施例中,参数a、b和c的计算公式为:

[0070][0071]

其中,fs为adc采样率,g为高速收发器用户端口数据位宽,l'为实际传输速率;

[0072]

由上述公式可以得出:

[0073]

a=1

[0074]

b=1

[0075]

c=1

[0076]

将a

·

q次采样得到的ad数据组帧后经过n通道的高速收发器的发送端分b

·

p次发送出去;

[0077]

每发完a

·

q次采样得到的ad数据,后续继续采样得到的ad数据序号加1;

[0078]

高速收发器的接收端的每一个通道从同一个序号处开始准备接收ad数据,当接收完a

·

p个高速收发器的用户端口时钟数据,重新组帧得到a

·

q次采样得到的ad数据;

[0079]

在本实施例中,将416次采样得到的ad数据组帧后经过13通道高速收发器分12次发送出去,即每采完416次ad数据后将在12个高速收发器用户端口时钟内传输完毕,由上述步骤可知,在采样完416次ad数据的时间内,高速收发器除了可以转发完ad数据,还可以转发c次其他数据,其中,c为1,本发明中将数据设置为序号与编码的方式的结合,具体的采用8b10b中的k28.0与k28.5(1cbc)并结合序号的组合,其中k码帮助gth稳定的工作,序号解决多路gth的同步问题,其中k码帮助高速收发器稳定的工作,序号解决多路高速收发器的同步问题。

[0080]

在一种可选的实施方式中,编码方式为8b10b,具体采用为1cbc进行编码,能够更好的提高高速收发器工作的稳定性。

[0081]

尽管已经示出和描述了本发明的实施例,对于本领域的普通技术人员而言,可以理解在不脱离本发明的原理和精神的情况下可以对这些实施例进行多种变化、修改、替换和变型,本发明的范围由所附权利要求及其等同物限定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1