一种NANDFlash读DQS采样方法与流程

一种nand flash读dqs采样方法

技术领域

1.本发明涉及ddr内存数据读写技术领域,具体是一种nand flash 读dqs采样方法。

背景技术:

2.目前,nand flash接口协议有2种:onfi和toggle协议。为提升数据传输速率,两者均使用ddr方式,即在dqs的上升沿和下降沿进行数据传输。而进行nand flash读操作时,dqs由nand flash返回,与nand flash phy时钟为异步关系,即相位关系不确定,因此实现读dqs的正确采样成为一个问题。根据奈奎斯特采样定律,采样频率必须大于被采样信号最高频率的两倍,因此,若要实现读dqs的正确采样并将其完全恢复出来,一般来说,nand flash phy时钟频率需大于dqs频率的两倍。但是,在fpga中,时钟资源有限,且相对于asic,fpga原型验证时钟频率较低。

技术实现要素:

3.本发明要解决的技术问题是一种nand flash读dqs采样方法,将dqs看作数据信号,使用与其频率相同的nand flash phy时钟clk_phy即可实现读dqs的采样,节省时钟资源。

4.为了解决所述技术问题,本发明采用的技术方案是:一种nand flash读dqs采样方法,本方法将dqs看作数据信号,使用与其频率相同的nand flash phy时钟clk_phy实现读dqs的采样,其中,clk_phy需要经过时钟管理单元mmcm进行相移,以达到最佳采样位置。

5.进一步的,clk_phy进行相移的过程为:对clk_phy进行训练,在训练过程中,相移值shift_val从0一直增大到最大值,同时进行读操作,记录下每个shift_val值对应的dqs_underrun的值,dqs_underrun的值标志着读dqs在读过程中没有被clk_phy正确采样,这样会形成一个数据眼图,其中1表示眼图闭合,表示使用当前相移值,clk_phy上升沿无法采样到正确的读dqs,0表示眼图打开,表示使用当前相移值,clk_phy上升沿可以采样到正确的读dqs,将dqs_underrun为0时的shift_val中间值作为最终的clk_phy相移值,产生最终的读时钟clk_rd,即可准确的用clk_rd采样到读dqs。

6.进一步的,通过相移状态控制机进行clk_phy训练,相移状态控制机共有6种状态:空闲状态、复位状态、计算状态、请求相移状态、等待相移状态和响应状态,相移状态控制机默认为空闲状态,当接收到相移调节信号为1时,进入复位状态,若此时复位信号有效,则保持在复位状态,若无效则进入相移计算状态,相移计算状态的转移条件受两个信号控制:相移锁定信号和相移计数值,相移锁定信号为1表示计算状态能稳定输出,相移控制状态机将接收到的相移初始值shift_val赋值给相移计数值,在相移请求状态时对输入时钟clk_phy进行相移,相移值shift_val从0一直增大到最大值,等待相移状态等待相移完成,相移完成后进入响应状态,最后进入空闲状态。

7.进一步的,本方法的实施步骤为:s01)、读dqs进入iddr,使用clk_rd进行采样,输出q0和q1,其中q0为在clk_phy上

升沿采样的读dqs电平,标记为dqs_valid,q1为在clk_phy下降沿采样到的读dqs电平,本方法中仅使用到q0;s02)、定义dfi_dqs_underrun,它标志着读dqs在读过程中没有被clk_rd正确采样,判断条件为dqs_valid为0且phy接收到的dfi接口读数据使能信号dfi_rddata_en为1;s03)、clk_phy经过时钟管理单元mmcm后产生读时钟clk_rd,并对clk_rd进行训练,使其产生合适的相移;s04)、将dqs看作数据信号,使用与其频率相同的读时钟clk_rd实现读dqs的采样。

8.进一步的,本方法用于fpga原型验证领域,将dqs看作数据信号,即在其进入fpga后,使用fpga接口上的输入ddr采样单元iddr,转换为电平信号,与读数据一同进入fifo,使用与其频率相同的nand flash phy时钟clk_phy即可实现读dqs的采样。

9.本发明的有益效果:本发明将读dqs看作数据信号,使用同频的clk_phy即可将读dqs进行正确采样,节省了时钟资源。

10.本发明介绍了在fpga原型验证领域的nand flash读dqs采样方法,并介绍了读dqs相移控制逻辑及训练方法,该方法灵活快捷准确,并可随着nand flash型号及使用工况的不同选择最佳的读dqs采样位置,避免亚稳态的发生。

附图说明

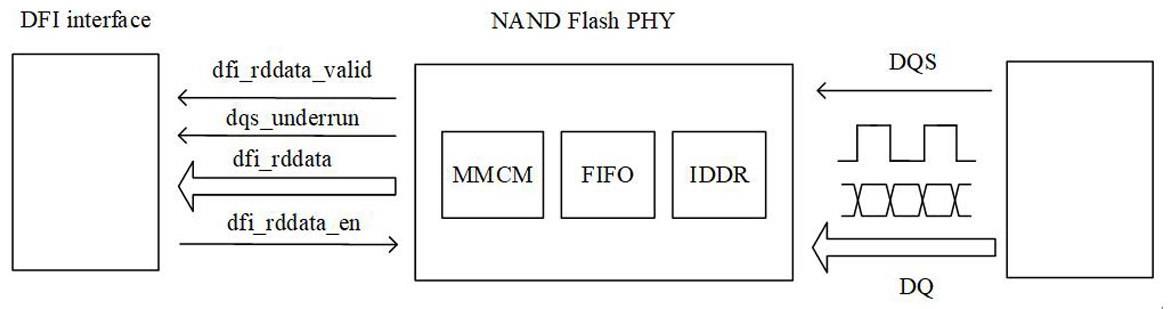

11.图1为本方法的系统架构图;图2为相移控制状态机的示意图。

具体实施方式

12.下面结合附图和具体实施例对本发明作进一步的说明。

13.实施例1本实施例公开一种nand flash读dqs采样方法,本方法将dqs看作数据信号,使用与其频率相同的nand flash phy时钟clk_phy实现读dqs的采样,其中,clk_phy需要经过时钟管理单元mmcm进行相移,以达到最佳采样位置。

14.clk_phy进行相移的过程为:对clk_phy进行训练,在训练过程中,相移值shift_val从0一直增大到最大值,同时进行读操作,记录下每个shift_val值对应的dqs_underrun的值,dqs_underrun的值标志着读dqs在读过程中没有被clk_phy正确采样,这样会形成一个数据眼图,其中1表示眼图闭合,表示使用当前相移值,clk_phy上升沿无法采样到正确的读dqs,0表示眼图打开,表示使用当前相移值,clk_phy上升沿可以采样到正确的读dqs,将dqs_underrun为0时的shift_val中间值作为最终的clk_phy相移值,产生最终的读时钟clk_rd,即可准确的用clk_rd采样到读dqs。

15.本实施例中,通过相移状态控制机进行clk_phy训练,如图2所示,相移状态控制机共有6种状态:空闲状态、复位状态、计算状态、请求相移状态、等待相移状态和响应状态,相移状态控制机默认为空闲状态,当接收到相移调节信号为1时,进入复位状态,若此时复位信号有效,则保持在复位状态,若无效则进入相移计算状态,相移计算状态的转移条件受两个信号控制:相移锁定信号和相移计数值,相移锁定信号为1表示计算状态能稳定输出,相移控制状态机将接收到的相移初始值shift_val赋值给相移计数值,在相移请求状态时对

输入时钟clk_phy进行相移,相移值shift_val从0一直增大到最大值,等待相移状态等待相移完成,相移完成后进入响应状态,最后进入空闲状态。

16.本方法的实施步骤为:s01)、读dqs进入iddr,使用clk_rd进行采样,输出q0和q1,其中q0为在clk_phy上升沿采样的读dqs电平,标记为dqs_valid,q1为在clk_phy下降沿采样到的读dqs电平,本方法中仅使用到q0;s02)、定义dfi_dqs_underrun,它标志着读dqs在读过程中没有被clk_rd正确采样,判断条件为dqs_valid为0且phy接收到的dfi接口读数据使能信号dfi_rddata_en为1;s03)、clk_phy经过时钟管理单元mmcm后产生读时钟clk_rd,并对clk_rd进行训练,使其产生合适的相移;s04)、将dqs看作数据信号,使用与其频率相同的读时钟clk_rd实现读dqs的采样。

17.实施例2本实施例涉及一种nand flash读dqs采样方法,用于fpga原型验证领域,如图1所示,在进行nand flash读操作时,nand flash返回dqs和dq至nand flash phy,其中dq在dqs跳变沿进行变化。由于读dqs和nand flash phy 时钟clk_phy时钟频率一致,但为异步时钟关系,即读dqs和clk_phy相位关系不固定,因此用clk_phy采样读dqs容易产生亚稳态现象,因此需要对clk_phy时钟域进行训练,经过mmcm产生合适的相移并固定,生成时钟clk_rd,用clk_rd实现对读dqs的正确采样。最终转化为标准的ddr phy interface(dfi)接口信号。

18.对clk_phy时钟域进行训练与实施例1相同,此处不再累述。

19.以上描述的仅是本发明的基本原理和优选实施例,本领域技术人员根据本发明做出的改机和替换,属于本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1