基于FPGA人工智能加速器的数据存储和传输方法

基于fpga人工智能加速器的数据存储和传输方法

技术领域

1.本发明涉及一种基于fpga人工智能加速器的数据存储和传输方法,属于图像算法技术领域。

背景技术:

2.随着人们对深度学习的深入研究,基于卷积神经网络算法精度得到了大幅提高,已经开始越来越广泛地应用于交通、安防、自动驾驶、航空航天等领域。改进后算法通过卷积神经网络提取图像中所需要的信息实现对图像中目标的定位和分类,涉及大量并行性运算,目前大多数卷积神经网络主要都是基于cpu、gpu实现的,基于cpu的卷积神经网络处理器无法利用卷积神经网络高并行性的特性,无法获得较高的计算吞吐量,并且其也存在功耗过高的问题。基于gpu的卷积神经网络处理器虽然可以利用卷积神经网络的计算并行性,获得很高的计算吞吐量,但是其功耗过高限制了其应用在嵌入式等对功耗要求高的场景。

3.另一方面,伴随着物联网时代到来,网络数据传输量激增,给云端数据中心运算处理带来极大负担,而边缘计算技术能分担服务器端的运算压力。为了满足边缘计算的需求,人们进行了大量研究,包括专用集成电路和基于fpga的深度学习加速器。由于设计灵活性高和开发时间短的优点,fpga已广泛应用于高效的深度学习。但是,大部分卷积神经网络的权重数量多,运算量庞大,需要存储资源、运算资源充足的fpga才能满足需求。

4.有鉴于此,针对图像识别领域和人工智能领域中硬件设备功耗受限导致性能不够满足需求的问题,确有必要提出一种基于fpga人工智能加速器的数据存储和传输方法,以解决上述问题。

技术实现要素:

5.本发明的目的在于提供一种基于fpga人工智能加速器的数据存储和传输方法,以优化加速器内部存储器和片上数据之间交互,使加速器内部数据更高效地存储传输。

6.为实现上述目的,本发明提供了一种基于fpga人工智能加速器的数据存储和传输方法,所述数据存储和传输方法主要包括:

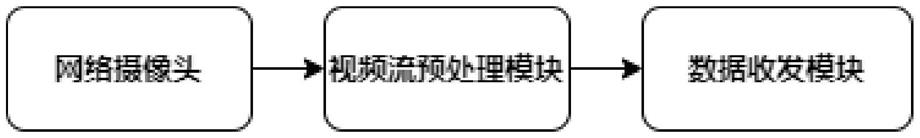

7.步骤1,设计arm端的架构:所述arm端包括图像收集模块、预处理模块以及数据发送模块;使用图像收集模块通过以太网将图像传递给预处理模块,所述预处理模块在arm端对收集到的数据进行预处理并将处理好的数据发送给所述数据收发模块;所述数据收发模块将图像数据和网络权重参数数据发送到fpga端的ddr4存储器上;

8.步骤2,设计fpga端的架构:所述fpga端包括输入缓冲模块、输出缓冲模块、dma、ddr4以及逻辑运算模块;dma从ddr4中读取图像数据和网络权重数据并发送到输入缓冲模块;输入缓冲模块将数据发送到逻辑运算模块进行处理;逻辑运算模块完成神经网络的各种运算;输出缓冲模块将逻辑运算模块运算完的输出数据发送到ddr4上;dma将运算结果从ddr4中读出来并发送到arm端的数据收发模块;

9.步骤3,优化fpga端数据存储传输通路。

10.作为本实用新型的进一步改进,所述步骤3具体包括:

11.步骤3.1,增加乒乓buffer:在双缓冲的基本思想上建立可编程逻辑上的缓冲设计,所述双缓冲区以乒乓方式,以使数据传输时间与计算时间重叠;

12.步骤3.2,对神经网络权重参数重排序:根据权重参数数据,对各层的神经网络权重参数根据当前层的特定进行参数排序。

13.作为本实用新型的进一步改进,在步骤1中,所述图像收集模块为网络摄像头模块。

14.作为本实用新型的进一步改进,在步骤1中,所述预处理模块为视频流预处理模块。

15.作为本实用新型的进一步改进,在步骤1中,所述数据收发模块与所述预处理模块之间的交互为axi总线和dma进行交互。

16.作为本实用新型的进一步改进,在步骤1中,所述ddr4存储器与片上数据缓冲之间的数据交互是由dma完成。

17.作为本实用新型的进一步改进,步骤2中所述各种运算包括卷积、池化、累加和地址映射。

18.本发明的有益效果是:本发明优化了加速器内部存储器和片上数据之间交互,使加速器内部数据更高效地存储传输,有效提高了吞吐量降低延迟,适用于对严格限制功耗和要求低延迟的应用场景,提高了智能硬件的计算效率。

附图说明

19.图1是本发明中arm端整体流程的示意图。

20.图2是本发明中fpga端整体流程的示意图。

21.图3是本发明中乒乓搬运的结构示意图。

22.图4是本发明中在dram中从参数排序的结构示意图。

具体实施方式

23.为了使本发明的目的、技术方案和优点更加清楚,下面结合附图和具体实施例对本发明进行详细描述。

24.本发明的基于fpga人工智能加速器的数据存储和传输方法主要包括:步骤1,设计arm端的架构:arm端有网络摄像头模块、视频流预处理模块、数据发送模块。本方法使用网络摄像头通过以太网口将图像传递给处理器系统(arm端),在arm端使用opencv库编写的相关软件代码对视频流进行预处理。然后数据收发模块通过axi总线和dma进行交互,并将图像数据和网络权重参数数据发送到fpga端的ddr4存储器上,由dma完成ddr4存储器与片上数据缓冲之间的数据交互。

25.如图1所示为arm端的整体流程图。最终分配给arm端,负责图像采集、预处理以及数据的发送。

26.步骤2,设计fpga端的架构:如图2所示,fpga端有输入输出缓冲模块、dma、ddr4、逻辑运算模块。dma从ddr中读取图像数据和网络权重数据并发送到输入缓冲模块。输入缓冲模块将数据发送到逻辑运算模块进行。逻辑运算模块负责完成神经网络的各种运算,涉及

卷积、池化、累加和地址映射等。输出缓冲单元用于将卷积神经网络运算完的输出feature map数据发送到ddr4上。dma将运算结果从ddr4中读出来并发送到arm端的数据收发模块。

27.步骤3,优化fpga端数据存储传输通路。通过优化来高效地存储和传输数据,来对卷积神经网络进行加速。将卷积神经网络应用于实现低功耗、特殊应用的高性能集成电路fpga,展示出了性能的提升。对于数据存储传输通路的优化有以下两点:

28.1)乒乓buffer

29.可编程逻辑上的缓冲设计建立在双缓冲区的基本思想之上,其中双缓冲区以乒乓方式,以使数据传输时间与计算时间重叠。本方法将乒乓buffer分为四组:两组用于存储输入feature map和卷积核权重,两组用于存储输出feature map。每个缓冲区都包含几个独立的缓冲库,每个输入缓冲库的数量等于feature map的平铺大小tn;每个输出缓冲组中的缓冲库的数量等于输出feature map的并行运算通道数tm。为了提高带宽利用率,采用双缓冲组来实现乒乓操作,一个用于装载操作,另一个用于卸载操作。图3显示了多个计算核数据传输阶段的时间,其中n为输入feature map的通道数。对于第一阶段,计算引擎正在处理输入缓冲组0,同时将下一阶段数据装载到输入缓冲区组1,然后在下一阶段执行相反的操作,这是输入特征图和权重的乒乓球操作。当n/tn阶段的计算核数据搬运完成后,将执行一次卸载操作,运算出来的输出feature map将被写回到ddr。在n/tn阶段,卸载操作将会卸载输出缓冲组0里的输出结果,直到输出缓冲组1中重用的临时数据生成新的结果,这是输出feature map的乒乓操作。如图3所示,通过乒乓buffer的设计,将从ddr读取数据的时延、在可编程逻辑上进行数据处理的时延和将处理完的数据写回ddr的时延重叠,减少总时延。

30.2)参数重排

31.对于权重参数数据,由于神经网络每层各不相同,与当前层和数据通路有关,可以对各层的神经网络权重参数根据当前层的特定进行参数重新排序,以减少访问内存的次数和增大突发传输的数据长度。假设神经网络第一层的权重规模为16*3*3*3(nof*nif*wky*wkx)也可以看作16*3*9(nof*nif*(wky*wkx)),其中nif为输入特征图的通道数,nof为输出特征图的通道书,wkx和wky为卷积核的长度。权重重排序前存取如图4所示,参数在ddr中没有按照排列顺序存储,需要按照箭头顺序从内存中取出。但由于权重参数在ddr中没有连续存放,一共需要访问ddr 16*3次,每次突发传输数据9个。如图4所示,数重新排序后将要读取的参数数据在ddr中顺序存储,在取出参数数据时只需要读取3次ddr,每次取出数据长度位16*9=144。减少搬运权重参数数据的次数,提高了带宽的使用率,降低了传输时延。

32.经实验证明,这种fpga人工智能加速器中的数据存储和传输方法,有效提高吞吐量降低延迟,适用于对严格限制功耗和要求低延迟的应用场景,提高了智能硬件的计算效率。

33.综上所述,本发明优化了加速器内部存储器和片上数据之间交互,使加速器内部数据更高效地存储传输,有效提高了吞吐量降低延迟,适用于对严格限制功耗和要求低延迟的应用场景,提高了智能硬件的计算效率。

34.以上实施例仅用以说明本发明的技术方案而非限制,尽管参照较佳实施例对本发明进行了详细说明,本领域的普通技术人员应当理解,可以对本发明的技术方案进行修改或者等同替换,而不脱离本发明技术方案的精神和范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1