电脑可读取记录介质及其提取三维芯片的寄生参数的方法与流程

本发明大体上涉及一种提取寄生参数的方法,更具体言之,其涉及一种提取三维芯片的寄生参数的方法以及内储其程序的电脑可读取记录介质。

背景技术:

1、设计规则检查(design rule checking,drc)、电路布局验证(layout versusschematic,lvs)以及布局寄生参数提取(layout parasitic extraction,lpe)是电子设计自动化的一个重要组成部分。drc决定了指定的集成电路芯片的物理布局(layout)是否满足所需的参数要求与设计规范,绘制与编辑好的布局会根据代工厂的制作工艺要求进行drc检查。lvs用以评估布局是否与电路图(schematic)完全一致,lpe则是对布局进行寄生参数(rc)提取,产生出一网表(netlist),其中描述了布局中部件的连接、电阻、电容或其他电性或尺寸等性质。

2、为了因应半导体制作工艺受到电子及材料物理极限的限制,三维芯片(3d ic)技术应运而生,其通过穿硅孔(through silicon via,tsv)或是混和键合(hybrid bonding)的方式将多颗裸片(die)进行三维空间的垂直整合,实现裸片在垂直方向上的相互连接,以此大幅增加布局密度。然而,现有的eda工具仅能提取三维芯片中个别裸片的寄生参数,无法完整提取整个三维芯片的寄生参数,特别是裸片之间混和键合界面处的寄生参数。故此,本领域的技术人士仍需对现有的寄生参数提取方法做进一步的改良,以期能够充分应用在三维芯片设计中。

技术实现思路

1、有鉴于前述现有技术的现况,本发明于此提出了一种新颖的提取三维芯片的寄生参数的方法,其可提取出完整的三维芯片(包含裸片之间的混和键合界面处)的寄生参数。

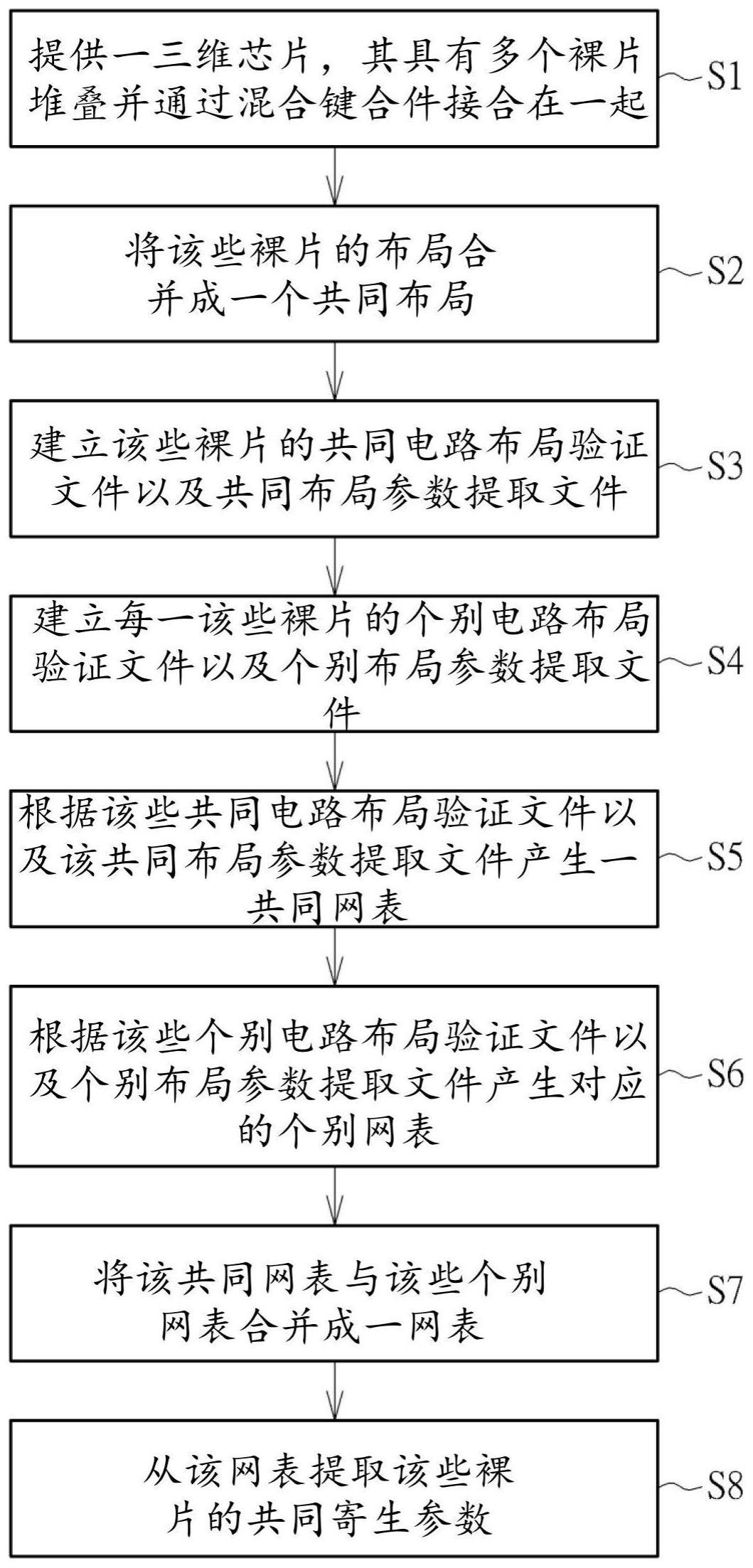

2、本发明的面向之一在于提出一种提取三维芯片的寄生参数的方法,其步骤包含提供一三维芯片,其具有多个裸片堆叠并通过混和键合件接合在一起、将该些裸片的个别布局合并成一共同布局、根据该共同布局建立该些裸片的共同电路布局验证文件以及共同布局参数提取文件、根据该些个别布局建立每一该些裸片的个别电路布局验证文件以及个别布局参数提取文件、根据该共同电路布局验证文件以及该共同布局参数提取文件产生一共同网表、根据该些个别电路布局验证文件以及该些个别布局参数提取文件产生对应的个别网表、将该共同网表与该些个别网表合并成一网表、以及从该网表提取该些裸片的共同寄生参数。

3、本发明的另一面向在于提出一种内储程序的电脑可读取记录介质,在电脑执行该程序时进行如下步骤:提供一三维芯片电路,该三维芯片电路具有多个裸片堆叠并通过混和键合件接合在一起、将该些裸片的个别布局合并成一共同布局、根据该共同布局建立该些裸片的共同电路布局验证文件以及共同布局参数提取文件、根据该些个别布局建立每一该些裸片的个别电路布局验证文件以及个别布局参数提取文件、根据该共同电路布局验证文件以及该共同布局参数提取文件产生一共同网表、根据该些个别电路布局验证文件以及该些个别布局参数提取文件产生对应的个别网表、将该共同网表与该些个别网表合并成一网表、以及从该网表提取该些裸片的共同寄生参数。

4、本发明的这类目的与其他目的在阅者读过下文中以多种图示与绘图来描述的优选实施例的细节说明后应可变得更为明了显见。

技术特征:

1.一种提取三维芯片的寄生参数的方法,该三维芯片具有多个裸片堆叠并通过混和键合件接合在一起,该方法包含:

2.如权利要求1所述的提取三维芯片的寄生参数的方法,其中根据该共同布局建立该些裸片的共同电路布局验证文件以及共同布局参数提取文件的步骤包括:

3.如权利要求1所述的提取三维芯片的寄生参数的方法,其中建立每一该些裸片的个别电路布局验证文件以及个别布局参数提取文件的步骤包括将每一该些裸片的截面建立在其对应的该个别布局参数提取文件中。

4.如权利要求1所述的提取三维芯片的寄生参数的方法,其中通过该共同布局参数提取文件能够提取该些裸片的键合界面处的寄生参数。

5.如权利要求1所述的提取三维芯片的寄生参数的方法,其中通过该个别布局参数提取文件能够提取该些裸片个别的寄生参数。

6.如权利要求1所述的提取三维芯片的寄生参数的方法,其中通过该共同布局参数提取文件与某一该个别布局参数提取文件能够同时提取该些裸片的键合界面处的寄生参数以及某一该裸片个别的寄生参数。

7.如权利要求1所述的提取三维芯片的寄生参数的方法,其中通过该共同布局参数提取文件与该些个别布局参数提取文件能够分别提取该些裸片的键合界面处的寄生参数以及该些裸片个别的寄生参数。

8.一种内储程序的电脑可读取记录介质,在电脑执行该程序时进行如下步骤:

9.如权利要求8所述的内储程序的电脑可读取记录介质,其中根据该共同布局建立该些裸片的共同电路布局验证文件以及共同布局参数提取文件的步骤包括:

10.如权利要求8所述的内储程序的电脑可读取记录介质,其中建立每一该些裸片的个别电路布局验证文件以及个别布局参数提取文件的步骤包括将每一该些裸片的截面建立在其对应的该个别布局参数提取文件中。

11.如权利要求8所述的内储程序的电脑可读取记录介质,其中通过该共同布局参数提取文件能够提取该些裸片的键合界面处的寄生参数。

12.如权利要求8所述的内储程序的电脑可读取记录介质,其中通过该个别布局参数提取文件能够提取该些裸片个别的寄生参数。

13.如权利要求8所述的内储程序的电脑可读取记录介质,该通过该共同布局参数提取文件与某一该个别布局参数提取文件能够同时提取该些裸片的键合界面处的寄生参数以及某一该裸片个别的寄生参数。

14.如权利要求8所述的内储程序的电脑可读取记录介质,其中通过该共同布局参数提取文件与该些个别布局参数提取文件能够分别提取该些裸片的键合界面处的寄生参数以及该些裸片个别的寄生参数。

技术总结

本发明公开一种内储程序的电脑可读取记录介质以及其提取三维芯片的寄生参数的方法,其中该提取三维芯片的寄生参数的方法的步骤包含提供一具有多个裸片的三维芯片、将该些裸片的个别布局合并成一共同布局、根据该共同布局建立该些裸片的共同电路布局验证文件以及共同布局参数提取文件、根据该些个别布局建立每一该些裸片的个别电路布局验证文件以及个别布局参数提取文件、根据该共同电路布局验证文件以及该共同布局参数提取文件产生一共同网表、根据该些个别电路布局验证文件以及该些个别布局参数提取文件产生对应的个别网表、将该共同网表与该些个别网表合并成一网表、以及从该网表提取该些裸片的共同寄生参数。

技术研发人员:林志岳,林峻毅,刘上裕,白洁茹

受保护的技术使用者:联华电子股份有限公司

技术研发日:

技术公布日:2024/1/14

- 还没有人留言评论。精彩留言会获得点赞!