数据读取方法、缓存器及集成电路与流程

本申请涉及数据存储技术,特别涉及一种数据读取方法、缓存器及集成电路。

背景技术:

1、在计算机系统中,通常需要用到用于存储数据的数据存储系统,但如何快速读取已经存储在数据存储系统的数据,一直是面临解决的主要技术问题。

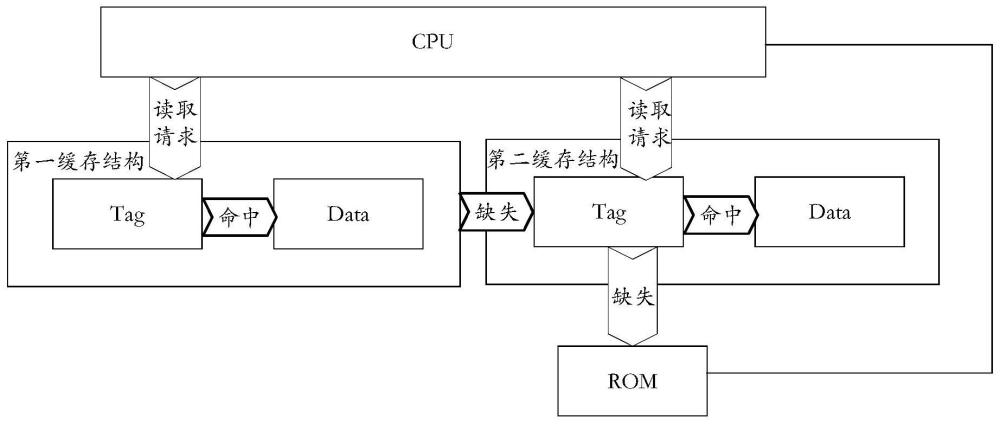

2、在现有技术中,通常是在中央处理器cpu和只读磁盘rom之间插入多级串行高速缓存器,如图1所示,第一缓存器和第二缓存器以″串连方式″与cpu连接,当cpu需要读取数据时,首先向第一缓存器的tag(tagmemory,是第一缓存器中用于存放地址的一块存储器)发送数据读取请求,如果第一缓存器命中该数据时,则根据tag从date(date memory,是第一缓存器中用于存放数据的一块存储器)中读取该数据。如果第一缓存器缺失该数据时,所述第一缓存器需要向第二缓存器发送数据读取请求,如果第二缓存器还缺失存储该数据,则第二缓存器就向rom发送数据读取请求,以获取该数据,而在获取到该数据之后,rom依次向第二缓存器发送该数据,第二缓存器接收到该数据之后,还需要向第一缓存器发送该数据,第一缓存器然后再将该数据发送至cpu。

3、由此可见,在现有技术中,如图1(a)~(c)所示,第一缓存器和第二缓存器在接收该请求之后才会在下一时钟节拍时确定本地是否存储该数据,而这导致第一缓存器和第二缓存器各有1个时钟节拍的时间消耗。而在第一缓存器和第二缓存器都未存储该数据时,需要去rom读取数据。此时已经至少有2个时钟节拍的时间消耗,这都会增加数据读取的延迟。另外,由于cpu和rom之间插入了多个串行高速缓存器,若数据存储在离cpu较远的缓存器或rom时,在获取数据时,需要逐级返回数据,进一步导致数据读取的延迟。

技术实现思路

1、本申请提供了一种数据读取方法、缓存器及集成电路,可以降低数据读取的延迟。

2、本申请提供的技术方案包括:

3、第一方面,本申请提供了一种数据读取方法,该方法应用于缓存器,所述缓存器包括分别与中央处理器cpu连接的第一缓存结构和第二缓存结构,所述方法包括:

4、所述第一缓存结构和所述第二缓存结构分别在第一时钟周期接收所述cpu发送的用于表示读取目标数据的目标数据读取请求;

5、若所述第一缓存结构在所述第一时钟周期针对所述目标数据读取请求的判定结果为命中,则所述第一缓存结构向所述第二缓存结构发送表示所述第一缓存结构存储目标数据的第一判定结果,并读取所述目标数据以向所述cpu发送所述目标数据;

6、当所述第二缓存结构接收到所述第一判定结果时,所述第二缓存结构依据所述第一判定结果中止在第二时钟周期针对所述目标数据读取请求的判定;

7、若所述第一缓存结构在所述第一时钟周期针对所述目标数据请求的判定结果为缺失,则向所述第二缓存结构发送用于表示所述第一缓存结构缺失所述目标数据的第二判定结果;

8、当所述第二缓存结构接收到所述第二判定结果并且在第二时钟周期针对所述目标数据请求的判定结果为命中时,则所述第二缓存结构读取所述目标数据以向所述cpu发送所述目标数据;

9、当所述第二缓存结构接收到所述第二判定结果并且在第二时钟周期针对所述目标数据请求的判定结果为缺失时,则向rom发送用于表示所述第二缓存结构缺失所述目标数据的第三判定结果,以从所述rom读取所述目标数据;

10、其中,所述第二时钟周期是与所述第一时钟周期相邻的下一时钟周期。

11、第二方面,本申请提供了一种缓存器,缓存器包括分别与中央处理器cpu连接的第一缓存结构和第二缓存结构,

12、第一缓存结构被配置为,在第一时钟周期接收cpu发送的用于表示读取目标数据的目标数据读取请求,若在所述第一时钟周期针对所述目标数据请求的判定结果为命中,则向所述第二缓存结构发送表示所述第一存储结构存储目标数据的第一判定结果,并读取所述目标数据以向所述cpu发送所述目标数据;若在所述第一时钟周期针对所述目标数据读取请求的判定结果为缺失,则向所述第二缓存结构发送用于表示所述第一存储结构缺失所述目标数据的第二判定结果;

13、第二缓存结构被配置为,在第一时钟周期接收所述cpu发送的用于表示读取目标数据的目标数据读取请求,当接收到所述第一判定结果时,依据所述第一判定结果中止在第二时钟周期针对所述目标数据读取请求的判定;当接收到所述第二判定结果并且在第二时钟周期针对所述目标数据请求的判定结果为命中时,则读取所述目标数据以向所述cpu发送所述目标数据;当接收到所述第二判定结果并且在第二时钟周期针对所述目标数据请求的判定结果为缺失时,则向rom发送用于表示所述第二缓存结构缺失所述目标数据的第三判定结果,以从所述rom读取所述目标数据;

14、其中,所述第二时钟周期是与所述第一时钟周期相邻的下一时钟周期。

15、第三方面,本申请还提供一种集成电路,包括中央处理器cpu和rom,所述cpu和rom分别连接本申请第二方面提供的所述缓存器。

16、第四方面,本申请还提供一种电子设备,配置有本申请第三方面提供的集成电路。

17、第五方面,本申请还提供一种计算机可读存储介质,存储有计算机程序或指令,所述计算机程序或指令被处理器执行时实现本申请第一方面提供的所述数据读取方法的步骤。

技术特征:

1.一种数据读取方法,其特征在于,该方法应用于缓存器,所述缓存器包括分别与中央处理器cpu连接的第一缓存结构和第二缓存结构,所述方法包括:

2.根据权利要求1所述的方法,其特征在于,所述第一缓存结构包括第一地址存储器和第一数据存储器,所述第一地址存储器用于存储数据所在地址,所述第一数据存储器用于存储数据;

3.根据权利要求2所述的方法,其特征在于,所述第二缓存结构包括第二地址存储器和第二数据存储器,所述第二地址存储器用于存储数据所在地址,所述第二数据存储器用于存储数据;

4.根据权利要求1至3中任一项所述的方法,其特征在于,所述缓存器为高速缓存器,所述第一缓存结构包括flip-flop寄存器,所述第二缓存结构包括sram。

5.一种缓存器,其特征在于,缓存器包括分别与中央处理器cpu连接的第一缓存结构和第二缓存结构,

6.根据权利要求5所述的缓存器,其特征在于,第一缓存结构包括第一地址存储器和第一数据存储器,第一地址存储器用于存储数据所在地址,第一数据存储器用于存储数据;

7.根据权利要求6所述的缓存器,其特征在于,第二缓存结构包括第二地址存储器和第二数据存储器,所述第二地址存储器用于存储数据所在地址,第二数据存储器用于存储数据;

8.根据权利要求5至7任一项所述的缓存器,其特征在于,所述缓存器为高速缓存器,所述第一缓存结构包括flip-flop寄存器,所述第二缓存结构包括sram。

9.一种集成电路,包括中央处理器cpu和rom,其特征在于,所述cpu和rom分别连接如权利要求5至8中任一项所述的缓存器。

10.一种电子设备,其特征在于,配置有如权利要求9所述的集成电路。

11.一种计算机可读存储介质,存储有计算机程序或指令,其特征在于,所述计算机程序或指令被处理器执行时实现权利要求1至4中任一项所述数据读取方法的步骤。

技术总结

本申请提供一种数据读取方法、缓存器及集成电路。所述数据读取方法基于一缓存器。所述缓存器包括并行连接于CPU的第一缓存结构和第二缓结构。缓存器的第一缓存结构和第二缓结构并行连接于CPU,可以使得CPU发送的数据读取请求都能同时到达缓存器的各级缓存结构中。所述数据读取方法将第一缓存结构配置为可以在与CPU的数据读取请求处于同一时钟周期就作出命中或缺失判定结果的响应。本申请数据读取方法在时序上可以节省一个时钟周期,进而能够减少数据读取时间,降低数据读取延迟。

技术研发人员:段楠,吴志伟

受保护的技术使用者:深圳云豹智能有限公司

技术研发日:

技术公布日:2024/4/8

- 还没有人留言评论。精彩留言会获得点赞!