神经网络输入图像点云卷积层计算的效率提升方法及电路与流程

1.本发明涉及人工智能计算技术领域,具体涉及神经网络输入图像点云卷积层计算的效率提升方法及电路。

背景技术:

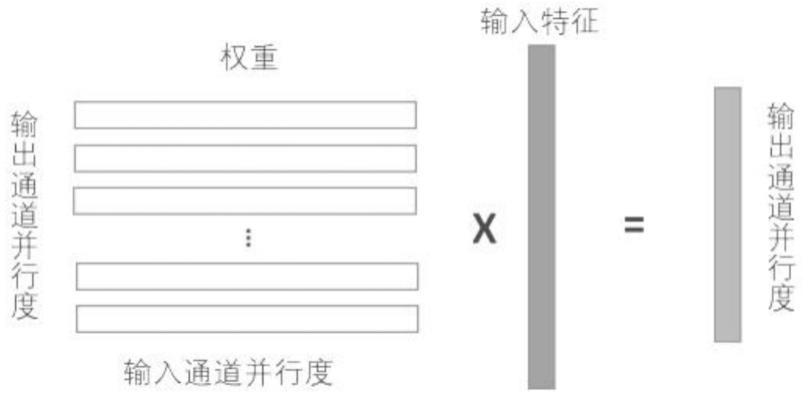

2.近年来,随着人工智能渗透到各个应用领域,深度神经网络在边缘端的部署成为人工智能落地的重要标志。限制神经网络加速性能有两个关键因素:峰值算力和计算效率。由于边缘端芯片尺寸和功耗的制约,不能一味堆砌计算单元来提升峰值算力,如何在已有的算力下提升计算效率已成为加速器设计的重中之重。

3.参考图1,目前业界主流的加速器都是将卷积计算分解为矩阵乘法计算,矩阵乘法可以容易实现并行计算,通常加速器会设置两个维度的并行度来达到较高的峰值算力:输入通道并行度和输出通道并行度。增大两个并行度可以实现较高的峰值算力。如xilinx的dpu的两个并行度最大为16,英伟达的nvdla两个并行度可达64。

4.然而,对于神经网络模型来说,输入的原始数据的通道数为3(图像rgb三通道)或4(点云x,y,z,强度),当加速器的输入通道并行度较高时(假定为64),理论效率不高于4.69%(3/64)或6.25%(4/64)。

技术实现要素:

5.为解决上述问题,本发明提出神经网络输入图像点云卷积层计算的效率提升方法。

6.本发明解决其技术问题所采用的技术方案是:

7.本发明第一方面提供了一种神经网络输入图像点云卷积层计算的效率提升方法,对原始输入数据进行预处理,以提升有效输入通道数,包括步骤:

8.步骤s1,沿输入特征的水平方向,将特征沿通道方向拼接;

9.将kx个尺寸为1*1*ch_in的特征条沿通道方向拼接,得到1*1*ch_in*kx的特征条;

10.步骤s2,沿输入特征垂直方向,将步骤s1拼接后的特征继续沿通道方向进行拼接;

11.将ky个尺寸为1*1*ch_in*kx的特征条沿通道方向拼接,得到1*1*ch_in*kx*ky的特征条;

12.步骤s3,完成卷积层的效率提升,即kx*ky倍;

13.其中,kx、ky分别为卷积层在水平方向和垂直方向的权重尺寸。

14.本发明第二方面提供了一种硬件电路,包括多个寄存器组组成的水平方向池化单元和垂直方向池化单元;

15.对水平方向池化单元的运算模块增加数据拼接功能,以完成步骤s1通道方向拼接;

16.对垂直方向池化单元的运算模块增加数据拼接功能,以完成步骤s2通道方向拼接;

17.将水平方向池化和垂直方向池化分两步进行,以获得将原特征1*1*ch_in的特征条拼接为1*1*ch_in*kx*ky的特征条。

18.本发明的上述技术方案具有如下有益的技术效果:

19.通过对原池化电路进行改进,完成输入特征通道方向的拼接,将特征的通道数提升kx*ky倍,对应的卷积计算效率也提高kx*ky倍。

附图说明

20.图1为现有技术输入/输出通道并行度计算展示图;

21.图2为本发明中输入特征水平方向沿通道方向拼接展示图;

22.图3为本发明中输入特征垂直方向沿通道方向拼接展示图;

23.图4为本发明中硬件电路水平方向池化单元完成通道拼接示意图;

24.图5为本发明中硬件电路垂直方向池化单元完成通道拼接示意图。

具体实施方式

25.为了使本发明实现的技术手段、创作特征、达成目的与功效易于明白了解,下面结合具体实施例和附图,进一步阐述本发明,但下述实施例仅仅为本发明的优选实施例,并非全部。基于实施方式中的实施例,本领域技术人员在没有做出创造性劳动的前提下所获得其它实施例,都属于本发明的保护范围。此外,在以下说明中,省略了对公知结构和技术的描述,以避免不必要地混淆本发明的概念。

26.本发明第一方面提供了一种神经网络输入图像点云卷积层计算的效率提升方法,通过原始输入数据进行预处理,来提升有效输入通道数,进而提升计算效率,假设卷积层的权重尺寸为kx和ky,则理论上卷积层的效率可提升kx*ky倍。

27.如图2所示,首先,沿输入特征的水平方向,将特征沿通道方向拼接;权重在输入特征中进行滑窗处理时,权重所覆盖的特征水平方向尺寸为kx,将这kx个尺寸为1*1*ch_in的特征条沿通道方向拼接,得到1*1*ch_in*kx的特征条;

28.如图3所示,接着,沿输入特征垂直方向,将步骤s1拼接后的特征继续沿通道方向进行拼接;权重所覆盖的特征水平方向尺寸为ky,将这ky个尺寸为1*1*ch_in*kx的特征条沿通道方向拼接,得到1*1*ch_in*kx*ky的特征条;

29.完成卷积层的效率提升,即kx*ky倍;其中,kx、ky分别为卷积层在水平方向和垂直方向的权重尺寸。

30.本发明第二方面提供了一种硬件电路,针对硬件加速器,包括多个寄存器组组成的水平方向池化单元和垂直方向池化单元;

31.如图4所示,首先,对水平方向池化单元的运算模块增加数据拼接功能,以完成通道方向拼接;如图5所示,接着,对垂直方向池化单元的运算模块增加数据拼接功能,以完成通道方向拼接;将水平方向池化和垂直方向池化分两步进行,即可将原特征1*1*ch_in的特征条拼接为1*1*ch_in*kx*ky的特征条。以达到获取卷积层的效率提升kx*ky倍的目的。

32.本发所打到的技术效果:通过对原池化电路进行改进,完成输入特征通道方向的拼接,将特征的通道数提升kx*ky倍,对应的卷积计算效率也提高kx*ky倍。

33.以上显示和描述了本发明的基本原理、主要特征和本发明的优点。本行业的技术

人员应该了解,本发明不受上述实施例的限制,上述实施例和说明书中描述的仅为本发明的优选例,并不用来限制本发明,在不脱离本发明精神和范围的前提下,本发明还会有各种变化和改进,这些变化和改进都落入要求保护的本发明范围内。本发明要求保护范围由所附的权利要求书及其等效物界定。

技术特征:

1.神经网络输入图像点云卷积层计算的效率提升方法,其特征在于,对原始输入数据进行预处理,以提升有效输入通道数,包括步骤:步骤s1,沿输入特征的水平方向,将特征沿通道方向拼接;将kx个尺寸为1*1*ch_in的特征条沿通道方向拼接,得到1*1*ch_in*kx的特征条;步骤s2,沿输入特征垂直方向,将步骤s1拼接后的特征继续沿通道方向进行拼接;将ky个尺寸为1*1*ch_in*kx的特征条沿通道方向拼接,得到1*1*ch_in*kx*ky的特征条;步骤s3,完成卷积层的效率提升,即kx*ky倍;其中,kx、ky分别为卷积层在水平方向和垂直方向的权重尺寸。2.一种硬件电路,其特征在于,包括多个寄存器组组成的水平方向池化单元和垂直方向池化单元;对水平方向池化单元的运算模块增加数据拼接功能,以完成步骤s1通道方向拼接;对垂直方向池化单元的运算模块增加数据拼接功能,以完成步骤s2通道方向拼接;将水平方向池化和垂直方向池化分两步进行,以获得将原特征1*1*ch_in的特征条拼接为1*1*ch_in*kx*ky的特征条。

技术总结

本发明涉及人工智能计算技术领域,具体涉及神经网络输入图像点云卷积层计算的效率提升方法及电路,对原始输入数据进行预处理,以提升有效输入通道数,包括步骤:沿输入特征的水平方向,将特征沿通道方向拼接;将Kx个尺寸为1*1*CH_in的特征条沿通道方向拼接,得到1*1*CH_in*Kx的特征条;沿输入特征垂直方向,将步骤S1拼接后的特征继续沿通道方向进行拼接;将Ky个尺寸为1*1*CH_in*Kx的特征条沿通道方向拼接,得到1*1*CH_in*Kx*Ky的特征条;完成卷积层的效率提升,即Kx*Ky倍;硬件电路,增加多个寄存器组组成的水平方向池化单元和垂直方向池化单元的数据拼接功能;本发明通过对原池化电路进行改进,完成输入特征通道方向的拼接,将特征的通道数提升Kx*Ky倍,对应的卷积计算效率也提高Kx*Ky倍。算效率也提高Kx*Ky倍。算效率也提高Kx*Ky倍。

技术研发人员:蔡文利 戴波 孙皓

受保护的技术使用者:北京宏景智驾科技有限公司

技术研发日:2022.03.10

技术公布日:2022/6/21

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1