一种芯片、信号处理方法以及电子设备与流程

本技术实施例涉及集成电路领域,尤其涉及一种芯片、信号处理方法以及电子设备。

背景技术:

1、随着集成电路技术发展,异步电路在高性能芯片设计中所占比重越来越高。异步电路不同于同步电路,异步电路不用全局时钟来协调系统中的时序,而通过上下级控制电路模块之间的握手信号协调上下级电路模块之间的信号时序。

2、目前异步电路中上下级控制电路模块之间通过握手信号协调信号时序时,为了使得上下级电路模块之间的数据信号和控制信号满足时序约束,一般在上下级控制电路模块之间设计匹配延迟模块,通过匹配延迟模块增加控制信号的时延,从而使得上下级电路模块之间的数据信号和控制信号的时序满足异步电路的时序约束。

3、由于匹配延迟模块的设计需要增加较多的晶体管或者电容,从而导致匹配延迟模块需要占用芯片较大的电路面积,使得芯片的电路面积开销比较大。

技术实现思路

1、本技术实施例提供了一种芯片、信号处理方法以及电子设备,用于降低芯片的电路面积开销。

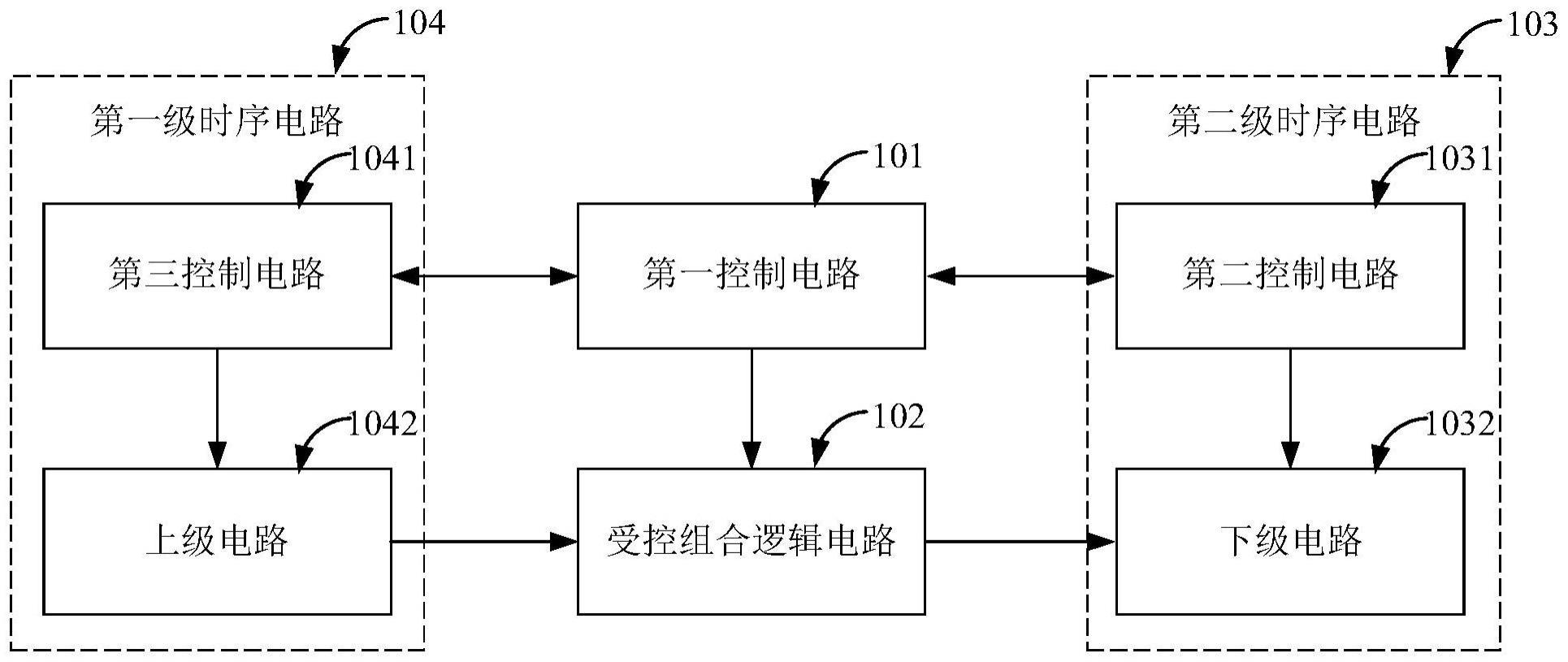

2、本技术实施例第一方面提供了一种芯片,该芯片包括第一控制电路、受控组合逻辑电路、第一级时序电路和第二级时序电路。其中,第一级时序电路的数据输出端与受控组合逻辑电路的数据输入端连接,受控组合逻辑电路的数据输出端与第二级时序电路的数据输入端连接。第一控制电路用于向受控组合逻辑电路发送控制信号,当控制信号为第一逻辑电平时,受控组合逻辑电路用于根据控制信号输出被受控组合逻辑电路锁存的逻辑结果,即受控组合逻辑电路中的组合逻辑电路未被使能,增加了数据信号到达的人第二级时序电路的传输时延。当控制信号为第二逻辑电平时,受控组合逻辑电路用于根据第一级时序电路的数据输出端输出的数据信号,输出受控组合逻辑电路中组合逻辑电路的即时逻辑结果,即受控组合逻辑电路中的组合逻辑电路被使能,直接输出组合逻辑电路的即时逻辑结果。第二逻辑电平与第一逻辑电平不同,第一逻辑电平包括低电平,第二逻辑电平包括高电平。

3、本技术实施例中提供的芯片中,通过在第一级时序电路和第二级时序电路之间的组合逻辑电路增加第一控制电路,使得组合逻辑电路成为受控组合逻辑电路,受控组合逻辑电路基于第一控制电路发送的控制信号输出被锁存的逻辑结果或者即时逻辑结果,从而能够协调受控组合逻辑电路与第二级时序电路的时序约束。相较于通过在第一级时序电路和第二级时序电路增加匹配延迟模块匹配组合逻辑电路时延的方案,本技术实施例中仅需要增加较少的控制器件就可以实现第一级时序电路和第二级时序电路的时序约束,从而降低了芯片的电路面积开销。

4、一种可能的实施方式中,受控组合逻辑电路包括组合逻辑电路、功率门控电路和锁存电路。组合逻辑电路通过功率门控电路与电源或接地点相连接,功率门控电路包括nmos管和pmos管,组合逻辑电路通过pmos管与电源相连接,通过nmos管与接地点相连接。组合逻辑电路和锁存电路串联,锁存电路包括传输门电路与延迟电路并联后的电路。当控制信号为第一逻辑电平时,功率门控电路关闭,传输门电路开启,受控组合逻辑电路输出被锁存电路锁存的逻辑结果。当控制信号为第二逻辑电平时,功率门控电路开启,传输门电路关闭,受控组合逻辑电路输出即时逻辑结果。

5、本技术实施例中的受控组合逻辑电路中,通过功率门控电路和锁存电路实现对组合逻辑电路的控制,其中功率门控电路和锁存电路基于控制信号控制组合逻辑电路输出的逻辑结果,无需匹配延迟模块匹配组合逻辑电路的时延,降低了芯片的电路面积开销。

6、一种可能的实施方式中,受控组合逻辑电路包括组合逻辑电路、第一传输门电路和锁存电路。第一传输门电路、组合逻辑电路和锁存电路依次串联,锁存电路包括第二传输门电路和延迟电路并联后的电路。当控制信号为第一逻辑电平时,第一传输门电路关闭,第二传输门电路开启,受控组合逻辑电路输出被锁存电路锁存的逻辑结果。当控制信号为第二逻辑电平时,第一传输门电路开启,第二传输门电路关闭,受控组合逻辑电路输出即时逻辑结果。

7、本技术实施例中的受控组合逻辑电路中,通过第一传输门电路和锁存电路实现对组合逻辑电路的控制,其中第一传输门控电路和锁存电路基于第一控制电路发送的控制信号控制受控组合逻辑电路输出被锁村的逻辑结果或者即时逻辑结果,多种受控组合逻辑电路的实现方式提升了方案的可实现性。

8、一种可能的实施方式中,控制信号包括第一控制信号和第二控制信号,第二级时序电路包括第二控制电路和下级电路。第一控制电路用于向受控组合逻辑电路发送第一控制信号,第一控制信号用于触发受控组合逻辑电路向下级电路发送第一数据信号,第一数据信号包括被受控组合逻辑电路锁存的逻辑结果和即时逻辑结果。第一控制电路还用于向第二控制电路发请求信号,请求信号用于触发第二控制电路向下级电路发送第一下级控制信号,请求信号和第一控制信号由第一控制电路同时发出,第一数据信号早于第一下级控制信号到达下级电路。

9、本技术实施例中第一控制电路可以同时向第二控制电路发送请求信号和向受控组合逻辑电路发送第一控制信号,并且由第一控制信号触发的第一数据信号早于由请求信号触发的第一下级控制信号到达下级电路,即确保下级电路被使能时第一数据信号已经到达下级电路,从而保障了受控组合逻辑电路和下级电路之间的时序正确性,进而提升了方案的可实现性。

10、一种可能的实施方式中,第二控制电路用于向第一控制电路发送响应信号,响应信号用于触发第一控制电路向受控组合逻辑电路发送第二控制信号。组合逻辑电路用于根据第二控制信号向下级电路发送第二数据信号,第二数据信号包括被受控组合逻辑电路锁存的逻辑结果和即时逻辑结果,第二数据信号与第一数据信号不同。第二控制电路还用于向下级电路发送第二下级控制信号,响应信号和第二下级控制信号由第二控制电路同时发出,第二数据信号晚于第二下级控制信号到达下级电路。

11、本技术实施例中第二控制电路可以同时向第一控制电路发送响应信号和向下级电路发送第二下级控制信号,并且由响应信号触发的第二数据信号晚于第二下级控制信号到达下级电路,即确保下个周期的第二数据信号到达下级电路时下级电路未被使能,从而保障了受控组合逻辑电路和下级电路之间的时序正确性,进而提升了方案的可实现性。

12、一种可能的实施方式中,第一级时序电路包括第三控制电路和上级电路,上级电路包括锁存器、寄存器或上级组合逻辑电路。第二级时序电路包括第二控制电路和下级电路,下级电路包括锁存器、寄存器或下级组合逻辑电路,组合逻辑电路包括全加器。

13、本技术实施例中第一级时序电路和第二级时序电路分别为受控组合逻辑电路的上一级电路和受控组合逻辑电路的下一级电路,第一级时序电路和第二级时序电路的多种实现方式提升了方案的丰富性。

14、一种可能的实施方式中,受控组合逻辑电路包括由组合逻辑电路拆分后的多级受控组合逻辑电路,多级受控组合逻辑电路依次串联,每一级受控组合逻辑电路具有相应控制电路,每一级控制电路用于控制对应的受控组合逻辑电路,具体用于控制该级受控组合逻辑电路中组合逻辑电路输出被锁存的逻辑结果或者输出即时逻辑结果。其中,多级受控组合逻辑电路中每一级受控组合逻辑电路依次对数据信号进行处理,多级受控组合逻辑电路中不同受控组合逻辑电路同时处理多个数据信号。

15、本技术实施例中可将大延迟的组合逻辑电路拆分为多级受控组合逻辑电路,多级受控组合逻辑电路中不同受控组合逻辑电路同时处理多个数据信号,相较于一个组合逻辑电路处理完一个数据再处理下一个数据,拆分后的多级受控组合逻辑电路能够并行处理多个数据信号,从而提升了芯片处理数据的吞吐量,进一步提高了芯片的处理速度。

16、本技术实施例第二方面提供了一种信号处理方法,该方法可以由芯片执行,也可以由芯片的部分电路,例如芯片中受控组合逻辑电路、第一控制电路和第二控制电路等执行,还可以由能实现全部或部分芯片功能的逻辑模块或软件实现。第一方面提供的方法包括以下步骤:受控组合逻辑电路接收第一控制电路发送的控制信号。当控制信号为第一逻辑电平时,受控组合逻辑电路根据控制信号输出被受控组合逻辑电路锁存的逻辑结果。当控制信号为第二逻辑电平时,受控组合逻辑电路根据第一级时序电路的数据输出端的数据信号,输出受控组合逻辑电路中组合逻辑电路的即时逻辑结果,第二逻辑电平与第一逻辑电平不同。

17、一种可能的实施方式中,受控组合逻辑电路包括组合逻辑电路、功率门控电路和锁存电路,组合逻辑电路通过功率门控电路与电源或接地点相连接,组合逻辑电路和锁存电路串联,锁存电路包括传输门电路与延迟电路并联后的电路,受控组合逻辑电路根据控制信号输出被受控组合逻辑电路锁存的逻辑结果的过程中,当控制信号为第一逻辑电平时,功率门控电路关闭,传输门电路开启,受控组合逻辑电路输出被锁存电路锁存的逻辑结果。

18、一种可能的实施方式中,受控组合逻辑电路包括组合逻辑电路、第一传输门电路和锁存电路,第一传输门电路、组合逻辑电路和锁存电路依次串联,锁存电路包括第二传输门电路和延迟电路并联后的电路,受控组合逻辑电路根据第一级时序电路的数据输出端的数据信号,输出受控组合逻辑电路中组合逻辑电路的即时逻辑结果的过程中,当控制信号为第二逻辑电平时,功率门控电路开启,传输门电路关闭,受控组合逻辑电路根据第一级时序电路的数据输出端的数据信号,输出即时逻辑结果。

19、一种可能的实施方式中,第一控制电路向第二控制电路发送请求信号,请求信号用于触发第二控制电路向下级电路发送第一下级控制信号。受控组合逻辑电路向下级电路发送第一数据信号,第一数据信号基于第一控制电路发送的第一控制信号触发,请求信号和第一控制信号由第一控制电路同时发出,第一数据信号早于第一下级控制信号到达下级电路。

20、一种可能的实施方式中,第一控制电路接收第二控制电路发送的响应信号,响应信号用于触发第一控制电路向受控组合逻辑电路发送第二控制信号。受控组合逻辑电路向下级电路发送第二数据信号,第二数据信号基于第一控制电路发送的第二控制信号触发。第二控制电路向下级电路发送第二下级控制信号,响应信号和第二下级控制信号由第二控制电路同时发出,第二数据信号晚于第二下级控制信号到达下级电路。

21、一种可能的实施方式中,下级电路包括锁存器、寄存器或下级组合逻辑电路。

22、一种可能的实施方式中,将芯片中的组合逻辑电路拆分为多级受控组合逻辑电路,多级受控组合逻辑电路依次串联,每一级受控组合逻辑电路具有相应控制电路,每一级控制电路向对应的受控组合逻辑电路发送控制信号,使得该级受控组合逻辑电路中组合逻辑电路输出被锁存的逻辑机构或即时逻辑结果。其中,多级受控组合逻辑电路中每一级受控组合逻辑电路依次对数据信号进行处理,多级受控组合逻辑电路中不同受控组合逻辑电路同时处理多个数据信号。

23、本技术实施例第三方面提供了一种电子设备,包括处理器,处理器与存储器耦合,处理器用于存储指令,当指令被处理器执行时,以使得电子设备上述第二方面或第二方面任意一种的可能的实施方式所述的方法。

24、可以理解,上述提供的任一种信号处理方法或电子设备等所能达到的有益效果可参考对应的芯片中的有益效果,此处不再赘述。

- 还没有人留言评论。精彩留言会获得点赞!