一种车用芯片DDR仿真方法与流程

一种车用芯片ddr仿真方法

技术领域

1.本发明属于芯片仿真技术领域,尤其是涉及一种车用芯片ddr仿真方法。

背景技术:

2.目前,我国的芯片尤其是车规级芯片高度依赖于进口,智能化、电动化、网联化汽车的发展更是带动了芯片在智能座舱及自动驾驶方面的应用,为更好地应对当今国际形势,加强芯片的自主研发刻不容缓;芯片按照使用场景一般可以分成四个等级,即军工级、车规级、工业级、消费级,依据对芯片的严苛程度来说,军工级>车规级>工业级>消费级。由此可见,车规级芯片的严苛程度仅次于军工级,车规级芯片在设计之初就应以更加严格的要求进行;

3.而随着集成电路制造工艺的飞速发展,在当今数字集成电路中,ddr的数据传输速率越来越高,目前多已达到gbps的水平,越来越高的数据传输速率和越来越短的信号上升下降时间,使得系统的时序裕量越来越小,这给系统的信号完整性和电源完整性设计提出了较高的要求,许多设计由于信号完整性和电源完整性的问题,而导致ddr系统传输数据出现错误的码流,因此在系统级进行ddr pisi仿真,从而通过仿真分析给出准确的验证结果具有较大的实践意义,对于节省设计生产成本至关重要;

4.目前对ddr系统进行仿真时,主要有spice模型仿真和ibis模型仿真两种主流方法,spice模型仿真精度较高,但仿真时间较长,而ibis模型仿真时间短,但精度太差;基于上述问题,故此,本专利申请提出了一种车用芯片ddr仿真方法。

技术实现要素:

5.有鉴于此,本发明旨在提出一种车用芯片ddr仿真方法,以解决目前主流仿真方法难以满足仿真要求,导致验证结果不准确的问题。

6.为达到上述目的,本发明的技术方案是这样实现的:

7.一种车用芯片ddr仿真方法,包括如下步骤:

8.s1、利用软件工具提取控制器ibis plus模型;

9.s2、从ddr芯片中的die参数模型中依据需求提取相应的die参数;

10.s3、利用软件工具提取封装pkg、电路板pcb的s参数模型;

11.s4、通过从内存器官网或内存其供应商查找内存器模型,并对提取的ibis模型和s参数模型进行模拟仿真。

12.进一步的,步骤s1中,控制器ibis plus模型是指基于ibis格式的spice模型,对ibis模型进行抖动建模、c_comp动态建模和精准超频处理操作,使电源噪声对i/o端口的抖动特性表征出来。

13.进一步的,步骤s1具体包括如下步骤:

14.s11、准备i/o端口的晶体管级电路模型、配置方法和工艺文件;

15.s12、利用hspice软件建立spice仿真环境仿真验证单个i/o端口电路的功能;

16.s13、利用cadence软件的t2b工具建立t2b环境,生成ibis plus模型;

17.s14、对生成的ibis plus模型进行验证;若符合要求,则证明所提取的ibis plus模型成功;若不符合要求,则进行修改,并跳转至步骤s12。

18.进一步的,步骤s2中,提取的die参数为rlc参数,即电阻r、电感l和电容c数据信息。

19.进一步的,步骤s3具体包括如下步骤:

20.s31、利用cadence软件的powersi工具导入封装pkg、电路板pcb的布局文件,并将其合并;

21.s32、检查步骤s31合并后的布局文件堆叠信息;

22.s33、在powersi工具中选择网络,生成i/o端口;

23.s34、设置仿真频率,生成s参数模型。

24.进一步的,步骤s4中的内存器模型是指内存i/o端口的行为层面模型,该模型包含记忆i/o端口的输入电阻r、电容c和电感l寄生信息。

25.相对于现有技术,本发明所述的一种车用芯片ddr仿真方法具有以下有益效果:

26.本发明所述的一种车用芯片ddr仿真方法通过验证可发现能够对对芯片ddr系统级pisi进行较为准确的仿真分析,在尽量不影响仿真精度的前提下,大大缩短了仿真时间;此外,仿真可靠性强,通过仿真可以及时改进、优化电路设计,通过合理的建模仿真,可以给设计者以直观、准确的设计结果,便于及早发现问题、解决问题,从而缩短设计时间,大大降低设计成产成本。

附图说明

27.构成本发明的一部分的附图用来提供对本发明的进一步理解,本发明的示意性实施例及其说明用于解释本发明,并不构成对本发明的不当限定。在附图中:

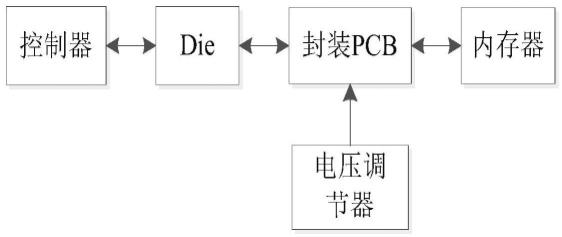

28.图1为本发明实施例所述的车用芯片ddr架构拓扑图;

29.图2为本发明实施例所述的控制器ibis plus模型提取流程图;

30.图3为本发明实施例所述的封装pkg、电路板pcb的s参数模型提取流程图;

31.图4为本发明实施例所述的采用仿真方法验证的功率波形图。

具体实施方式

32.需要说明的是,在不冲突的情况下,本发明中的实施例及实施例中的特征可以相互组合。

33.在本发明的描述中,需要理解的是,术语“中心”、“纵向”、“横向”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”、“内”、“外”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。此外,术语“第一”、“第二”等仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”等的特征可以明示或者隐含地包括一个或者更多个该特征。在本发明的描述中,除非另有说明,“多个”的含义是两个或两个以上。

34.在本发明的描述中,需要说明的是,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通。对于本领域的普通技术人员而言,可以通过具体情况理解上述术语在本发明中的具体含义。

35.下面将参考附图并结合实施例来详细说明本发明。

36.请参阅图1所示,车用芯片ddr仿真架构包括控制器ibis plus模型、die参数模型、封装pkg和电路板pcb的s参数模型、内存器和电压调节器vrm;在该架构中,利用以下仿真方法,大大节省了仿真时间,提高了仿真精度。

37.一种车用芯片ddr仿真方法,包括如下步骤:

38.s1、利用软件工具提取控制器ibis plus模型;

39.s2、从ddr芯片中的die参数模型中依据需求提取相应的die参数;

40.s3、利用软件工具提取封装pkg、电路板pcb的s参数模型;

41.s4、通过从内存器官网或内存其供应商查找内存器模型,并对提取的ibis模型和s参数模型进行模拟仿真。

42.步骤s1中,控制器ibis plus模型是指基于ibis格式的spice模型,对ibis模型进行抖动建模、c_comp动态建模和精准超频处理操作,使电源噪声对i/o端口的抖动特性表征出来,从而使得ddr的仿真精度更高;此外,控制器ibis plus模型能够准确模拟功率对信号的影响,其模拟精度接近spice模拟,远高于普通ibis模型;

43.本技术方案中采用的抖动建模、c_comp动态建模和精准超频处理技术均为本领域技术人员熟知的常规技术手段,本专利申请故不再作进一步赘述。

44.利用cadence软件的t2b工具提取ibis plus模型,t2b工具用于生成ibis模型或ibis plus模型,在使用t2b工具生成ibis plus模型之前,需要先利用meta-software公司的hspice软件建立spice仿真环境仿真验证单个i/o端口电路的功能,该程序需要用hspcie软件依据自己需求进行简单模型的搭建,并设置好电压、电容负载、输入波形等参数进行仿真,之后利用cadence软件的t2b工具建立t2b环境,生成ibis plus模型;如图2所示,具体方法为:

45.步骤s1具体包括如下步骤:

46.s11、准备i/o端口的晶体管级电路模型、配置方法和工艺文件;

47.s12、利用hspice软件建立spice仿真环境仿真验证单个i/o端口电路的功能;

48.s13、利用cadence软件的t2b工具建立t2b环境,生成ibis plus模型;

49.s14、对生成的ibis plus模型进行验证;若符合要求,则证明所提取的ibis plus模型成功;若不符合要求,则进行修改,并跳转至步骤s12。

50.上述方法生成的ibis plus模型包括ibis文件和ckt文件。ckt文件是一个加密的spice网表,具有io特性。ibs文件可以调用ckt文件,用户可以通过调用ibis文件进行模拟。

51.步骤s2中,提取的die参数为rlc参数,即电阻r、电感l和电容c数据信息,die参数模型包含信号和电源路径中的寄生参数,使得仿真拓扑更加接近实际,保证了仿真结果的准确性。

52.powersi工具提取的s参数模型为bnp文件,包含信道反射、串扰等信息;但在仿真

中,由于文件中包含了大量的通道信息,可能会出现不收敛的现象,为了提高仿真的收敛性,需利用cadence软件的sigrity工具将提取的s参数模型转换为bbs模型,转换后的模型可调用s参数模型,同时,也可提高仿真的收敛性;

53.如图3所示,步骤s3具体包括如下步骤:

54.s31、利用cadence软件的powersi工具导入封装pkg、电路板pcb的布局文件,并将其合并;

55.s32、检查步骤s31合并后的布局文件堆叠信息;

56.s33、在powersi工具中选择网络,生成i/o端口;

57.s34、设置仿真频率,生成s参数模型。

58.封装pkg、电路板pcb的s参数:为了进行ddr的系统级pisi仿真,需要对封装pkg、电路板pcb进行精确模拟,并尽可能提高仿真的收敛性,仿真中采用了s参数模型,s参数模型包含了信号的反射、串扰和损耗信息;因此,它可以准确地描述传输信道的频域特性;在提取s参数模型时,我们将封装pkg、电路板pcb合并提取其s参数模型,这样可以使得提取的模型更加接近真实情况。

59.步骤s4中的内存器模型是指内存i/o端口的行为层面模型,该模型包含记忆i/o端口的输入电阻r、电容c和电感l寄生信息,通过它可以得到接收器的上升下降转换时间、信号在i/o端口的延迟、过压以及欠压等电气特性。

60.电压调节器模型(vrm):vrm是一个电压调节模块,是分布式电源系统中的重要组成部分,其可根据不同负载需要独立调节输出电压,从而可以实现低电压、大电流、高功率密度及高稳定度输出;在本发明设计系统中,其主要作用是在仿真中为ddr的i/o端口供电,用vrm可以提供较为理想的dc电压,这样的电压可以尽量避免电源噪声对信号的影响,在分析影响信号质量因素的时候,使用该电源可以排除电源引入的噪声的作用。

61.在该仿真模拟方法中,ddr通道包含32位dq信号和dqs信号,数据速率为1066mbps,激励为脉冲频率的prbs7模式,dbi功能使能。

62.图4功率波形图显示了电源的电压噪声波形,从波形可以看出,标准电压为1.1v,电压波动范围为1.02v-1.165v。

63.在本发明设计的仿真方法中,首先要进行对控制器ibis plus模型和s参数模型的提取,利用t2b提取控制器ibis plus模型,利用powersi工具提取s参数模型,其次,在利用提取的模型进行较为精确的仿真,最后,查看仿真结果,从仿真结果中判断信号质量,进而决定下一步的工作;为进行验证,分别用标准ibis模型、ibis plus模型、spice模型,对i/o端口电路作一系列的仿真,为验证i/o端口抖动的表征效果,在电源上叠加一个正弦源,作为电源噪声,频率为200mhz,输入方波的频率为1.2ghz,观测i/o端口的抖动大小,发现采用ibis plus模型和spice模型仿真得到的抖动大小,室种很相近,因此,可认为ibis plus在表征电源噪声引起的抖动方面,精度与spice非常接近,远远优于传统ibis模型;此外,抖动特征仅在ibis plus和spice中有,传统ibis模型仿真时间50分钟,ibis plus模型仿真时间3.5小时,spice模型仿真时间1.8天,收敛性spice模型较差;综上,利用ibis plus模型仿真架构能够获得较好的精度,同时大大缩短仿真时间,并给ddr接口的ssn和抖动分析提供了一种新的高效可靠方法。

64.以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精

神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1