用于生成深度信息的电子装置和生成深度信息的方法与流程

用于生成深度信息的电子装置和生成深度信息的方法

1.相关申请的交叉引用

2.本技术基于并要求于2021年4月26日在韩国知识产权局提交的韩国专利申请no.10-2021-0053756的优先权,其公开内容通过引用整体合并于此。

技术领域

3.本发明构思涉及一种用于生成深度信息的处理电路,更具体地讲,涉及一种包括用于使用照度数据生成深度信息的处理电路的电子装置和生成深度信息的方法。

背景技术:

4.由于互补金属氧化物半导体(cmos)图像传感器广泛地安装在便携式电子装置上,因此在各种成像环境中需要清晰的图像。为了在低照度环境中捕捉清晰的图像,关于对象的深度信息需要是精确的。

5.尽管飞行时间(tof)传感器通常用于获取深度信息,但是存在需要大空间并且成本和功耗增加的缺点。而且,普通的基于rgb的cmos图像传感器易受低照度的影响。

技术实现要素:

6.本发明构思的各方面提供了一种即使在低照度下也能够获取准确的深度信息的处理电路、一种包括该处理电路的电子装置、以及一种生成深度信息的方法。

7.根据本发明构思的一方面,一种电子装置被配置为生成深度信息,并且包括:存储器,其存储一个或多个指令和图像数据;以及至少一个处理电路,其被配置为通过执行一个或多个指令生成关于图像数据的深度信息,其中,至少一个处理电路还被配置为获取图像数据的照度数据,通过使用照度数据和被配置为提取视差特征的第一人工神经网络来生成照度数据的绝对深度数据,并且基于绝对深度数据来生成深度信息。

8.根据本发明构思的另一方面,一种电子装置包括:图像传感器,其被配置为通过使用多个光电转换元件感测对象,并且生成具有视差的图像数据,其中,多个光电转换元件中的至少两个共享一个微透镜;存储器,其存储一个或多个指令和图像数据;以及至少一个处理电路,其被配置为通过执行一个或多个指令生成关于图像数据的深度信息,其中,至少一个处理电路被配置为:通过使用被配置为估计图像数据的绝对深度的第一人工神经网络来生成图像数据的绝对深度数据,通过使用被配置为基于与图像数据对应的场景的形状来估计相对深度的第二人工神经网络生成绝对深度数据的相对深度数据,以及通过使用第三人工神经网络将绝对深度数据与相对深度数据融合来生成深度信息。

9.根据本发明构思的另一方面,一种由处理电路执行的生成关于图像数据的深度信息的方法包括:从存储器获取来自图像数据的符合yuv格式的照度数据;通过使用第一人工神经网络将视差特征学习应用于照度数据来生成绝对深度数据;通过使用第二人工神经网络将场景学习应用于绝对深度数据来生成相对深度数据;以及通过使用第三人工神经网络将绝对深度数据与相对深度数据融合来生成深度信息。

附图说明

10.从以下结合附图的详细描述中,本发明构思的实施例将被更清楚地理解,在附图中:

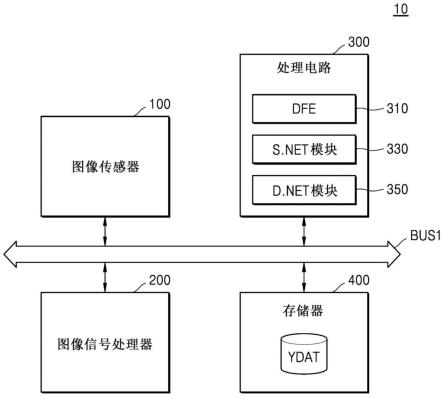

11.图1是示出根据本发明构思的示例实施例的包括处理电路的电子装置的框图;

12.图2是示出根据本发明构思的示例实施例的生成深度信息的方法的流程图;

13.图3是具体示出图像信号处理器的框图;

14.图4a和图4b是示出图像数据的rgb格式和yuv格式之间的转换关系的示图;

15.图5a至图5d是示出符合yuv格式的图像数据的数据结构的示图;

16.图6a至图6c是示出根据本发明构思的示例实施例的处理电路的框图;

17.图7a至图7c是示出人工神经网络的结构和操作的示图;

18.图8是示出根据本发明构思的示例实施例的视差特征提取器的结构的框图;

19.图9是示出根据本发明构思的示例实施例的场景网络模块的结构的框图;

20.图10是示出根据本发明构思的示例实施例的视差网络模块的结构的框图;

21.图11是示出根据本发明构思的示例实施例的后处理层的结构的框图;

22.图12a至图12c是示出根据本发明构思的示例实施例的图像数据的深度估计结果的示图;

23.图13a至图13d是示出根据本发明构思的示例实施例的像素的结构的示图;

24.图14是示出根据本发明构思的示例实施例的电子系统的框图;

25.以及

26.图15是示出图14的片上系统的示例实施例的框图。

具体实施方式

27.在下文中,将参照附图详细描述本发明构思的实施例。

28.图1是示出根据本发明构思的示例实施例的包括处理电路的电子装置10的框图。

29.参照图1,电子装置10可通过硬件和软件的交互来处理数据,并且可向用户提供处理结果。电子装置10可提供执行软件的物理基础,并且可通过使用硬件的资源来导出用户想要的结果。在示例实施例中,电子装置10可通过操作系统(os)执行应用软件,并且根据执行的操作结果可存储在存储器400中。在这种情况下,电子装置10可被称为计算系统。

30.电子装置10可包括图像传感器100、图像信号处理器(isp)200、处理电路300和存储器400,并且可通过第一总线bus1与每个组件通信。

31.图像传感器100可安装在具有图像或光学感测功能的电子装置上。例如,图像传感器100可安装在电子装置上或电子装置中,电子装置诸如相机、智能电话、可穿戴装置、物联网(iot)装置、平板个人计算机(pc)、个人数字助理(pda)、便携式多媒体播放器(pmp)、导航装置等。此外,图像传感器100可安装在作为车辆、家具、制造设备、门或门铃、或各种测量设备中的一部分提供的电子装置上或电子装置中。

32.图像传感器100可将通过光学透镜入射的对象的光信号转换为电信号,并可基于电信号生成图像数据,并将图像数据输出到外部(例如,图像传感器100的外部)。图像传感器100可包括例如包括多个二维地布置的像素的像素阵列和读出电路,并且像素阵列可将接收到的光信号转换成电信号。

33.例如,像素阵列可实现为诸如电荷耦合器件(ccd)或互补金属氧化物半导体(cmos)的光电转换元件、或者其它各种光电转换元件中的一种。光电转换元件可生成根据入射光的强度而变化的光电荷。例如,光电转换元件可包括光电二极管、光电晶体管、端口门或钉扎光电二极管。例如,作为p-n结二极管的光电二极管pd可生成与入射光量成比例的电荷,即,作为负电荷的电子和作为正电荷的空穴。

34.微透镜和滤色器可层叠在多个像素中的每一个的上部上。在示例实施例中,多个像素中的每一个可通过使用至少两个光电转换元件来感测对象。例如,多个像素中的每一个可包括相对于微透镜的光轴布置在左方向(或向上方向)上的至少一个第一光电转换元件和相对于微透镜的光轴布置在右方向(或向下方向)上的至少一个第二光电转换元件。多个像素中的每一个可输出由第一光电转换元件生成的第一图像信号或由第二光电转换元件生成的第二图像信号。图像数据中可包括视差,视差是由一对光电转换元件感测的同一对象的第一图像信号和第二图像信号之间的相位差。如本文所使用的,包括共享一个微透镜的两个光电转换元件的像素将被称为双像素。将参照图13a至图13d详细描述双像素的结构。

35.读出电路可基于从像素阵列提供的电信号,输出已经对其执行了诸如坏像素的去除的预处理的数据作为图像数据。图像传感器100可实现为包括像素阵列和读出电路的半导体芯片或封装件。

36.isp 200可对从图像传感器100提供的图像数据执行图像处理。例如,isp 200可对图像数据执行用于改变数据格式的图像处理(例如,将拜尔模式的图像数据改变为yuv格式或rgb格式),或者用于改善图像质量的图像处理(诸如噪声去除、亮度调整或锐度调整)。将参照图3详细描述isp 200的结构。

37.根据示例实施例,isp 200可将以拜尔格式感测的图像数据转换为rgb格式或yuv格式。根据本发明构思的示例实施例,isp 200可生成照度数据ydat和色度数据udat和vdat作为处理图像数据的结果。照度数据ydat和色度数据udat和vdat可存储在存储器400中。

38.处理电路300可处理电子装置10的整体操作,具体地,可处理构成电子装置10的其它组件(例如,图像传感器100、isp 200和存储器400)的请求,并且可控制其它组件。在示例实施例中,处理电路300可执行特定任务、指令或操作。在示例实施例中,可从存储器400加载指令。例如,计算机程序代码可用于实现处理电路300的一些功能。

39.在示例实施例中,处理电路300可实现为通用处理器、专用处理器、应用处理器(ap)等。在示例实施例中,处理电路300可实现为包括专用逻辑电路(例如,现场可编程门阵列(fpga)、专用集成电路(asic)等)的运算处理器(例如,中央处理单元(cpu)、图形处理单元(gpu)、神经处理单元(npu)、ap等),但不限于此。

40.处理电路300还可包括加速器,加速器为用于高速数据运算(例如人工智能(ai)数据运算)的专用电路,并且加速器可包括gpu、npu和/或数字信号处理器(dsp)。根据示例实施例,加速器可实现为物理地独立于处理电路300的其它组件的单独芯片。根据示例实施例,处理电路300可通过使用一个或多个人工神经网络来处理数据。此外,处理电路300可通过经由一个或多个人工神经网络学习数据来增强一个或多个人工神经网络。

41.根据本发明构思的与ai相关的功能可通过至少一个处理电路300和存储器400来操作。处理电路300可以是通用处理器(诸如cpu、ap或dsp)、图形专用处理器(诸如gpu或视

觉处理单元(vpu))或ai专用处理器(诸如npu)。处理电路300可根据存储在存储器400中的预定义的操作规则或ai模型来控制输入数据的处理。当处理电路300是ai专用处理器时,ai专用处理器可被设计为具有专用于处理特定ai模型的硬件结构。通过学习创建预定义的操作规则或ai模型。这里,表述“通过学习创建”意味着通过学习算法使用多个学习数据片段来训练基础ai模型,使得创建被设置为执行期望特征(或目的)的预定义的操作规则或ai模型。这种学习可在执行根据本发明构思的ai的装置中执行,或者可通过单独的服务器和/或系统执行。学习算法的示例可以是监督学习、无监督学习、半监督学习或强化学习,但不限于此。

42.人工神经网络可包括深度神经网络(dnn),例如,卷积神经网络(cnn)、循环神经网络(rnn)、受限玻尔兹曼机(rbm)、深度置信网络(dbn)、双向循环深度神经网络(brdnn)或深度q网络,但不限于此。

43.人工神经网络可由多个神经网络层组成。多个神经网络层中的每一个具有多个权重值,并且通过前一层的运算结果与多个权重值之间的运算来执行神经网络运算。多个神经网络层的多个权重值可由ai模型的学习结果来优化。例如,可更新多个权重值,使得在学习处理期间从ai模型获取的损失值或成本值被减小或最小化。将参照图7a至图7c详细描述人工神经网络。

44.根据本发明构思的示例实施例,处理电路300可包括视差特征提取器(dfe)310、场景网络(s.net)模块330和视差网络(d.net)模块350。

45.一对图像数据可被输入到dfe 310,并且作为结果,可生成包括特征的一条输出数据。在示例实施例中,dfe 310可通过使用人工神经网络从输入图像提取诸如边界、线、颜色、边缘(对象的边界)、密度(包括密集状态和稀疏状态)和深度的特征。如本文所使用的,具有密集(例如,高)密度的图像将被称为纹理图像,而具有稀疏(例如,低)密度的图像将被称为无纹理图像。纹理图像可对应于高频,并且无纹理图像可对应于低频。

46.dfe 310可通过使用人工神经网络预先学习图像的密度。例如,dfe 310可通过使用人工神经网络预先学习高密度图像(即,纹理图像),并且可根据学习结果来改进对输入数据的边缘检测的性能。

47.在示例实施例中,dfe 310可估计具有视差的输入数据对的绝对深度。例如,dfe 310可生成绝对深度数据作为提取输入数据对的特征的结果。

48.根据本发明构思的示例实施例,照度数据ydat可被输入到dfe310,使得可估计照度数据ydat的绝对深度。

49.一条数据可被输入到s.net模块330,并且作为结果,可生成包括特征的一条输出数据。s.net模块330可通过使用被配置为学习场景的整体特征的人工神经网络来处理输入图像。场景网络s.net是学习场景的整体特征的人工神经网络,可以以金字塔结构来实现场景网络s.net。根据示例实施例,s.net模块330可在顺序地降低与图像数据对应的场景的分辨率的同时对该场景执行编码,并可在顺序地提高分辨率的同时执行解码,直到返回到初始分辨率。例如,场景网络s.net可具有五到六个编码级和解码级。作为在顺序地降低分辨率的同时执行编码的结果,场景网络s.net可学习表示场景的所有分辨率的特征。例如,s.net模块330使用的人工神经网络可以是pydnet,但是本发明构思不限于特定模型或特定实施例。

50.根据本发明构思的示例实施例,s.net模块330可通过使用场景网络s.net来估计输入图像的相对深度。例如,s.net模块330可被提供有从dfe 310输出的绝对深度数据,并且相对深度数据可作为由场景网络s.net对绝对深度数据的处理的结果被生成。通过估计低密度图像(即,无纹理图像)的相对深度,s.net模块330即使对于具有相对小的视差的图像数据也可获取相对准确的深度。

51.一条数据可被输入到d.net模块350,并且作为结果,包括特征的一条输出数据可被生成。d.net模块350可通过使用人工神经网络将相对深度数据与绝对深度数据融合。视差网络d.net是通过将相对深度数据与绝对深度数据融合来生成最终深度数据的人工神经网络,视差网络d.net可包括激活层和多个卷积层,激活层包括至少一个修正线性单元(relu)函数。例如,视差网络d.net可由五个级组成,每个级具有一个卷积层和一个激活层。

52.根据本发明构思的示例实施例,d.net模块350可通过使用视差网络d.net将相对深度数据与绝对深度数据融合。例如,d.net模块350可被提供有从dfe 310输出的绝对深度数据和从s.net模块330输出的相对深度数据,并且最终深度数据可作为视差网络d.net的处理结果被生成。最终深度数据可通过后处理层(未示出)的处理被转换成深度信息。

53.如本文所使用的,dfe 310、s.net模块330和d.net模块350可实现为硬件、固件和/或软件的组合。例如,dfe 310、s.net模块330和d.net模块350均可实现为处理电路(诸如包括逻辑电路的硬件),或者可实现为硬件和软件的组合(诸如运行执行人工神经网络的处理操作的软件的处理器)。

54.根据本发明构思的示例实施例,与rgb格式的图像数据相比,照度数据ydat即使在经过人工神经网络处理之后,对于低照度环境也可以是鲁棒的。根据本发明构思的示例实施例,与使用rgb格式的图像数据的情况相比,处理电路300可使用照度数据ydat作为输入,并且可增强作为在处理电路300中使用的至少一个人工神经网络的处理结果的深度估计结果。

55.存储器400可存储由图像传感器100、isp 200和/或处理电路300生成或处理的数据,并且可将存储的数据提供给isp 200和/或处理电路300。存储器400可存储用于电子装置10的os、应用和处理操作的指令。

56.根据示例实施例,存储器400可以是与处理电路300实时交换数据的工作存储器。例如,存储器400可包括作为易失性存储器的动态随机存取存储器(dram)、静态随机存取存储器(sram)、移动dram、双数据速率同步动态随机存取存储器(ddr sdram)、低功率ddr(lpddr)sdram、图形ddr(gddr)sdram、rambus动态随机存取存储器(rdram)等。然而,这仅仅是示例实施例,并且本发明构思不排除存储器400可包括非易失性存储器。

57.例如,存储器400可以是以非易失性方式存储由图像传感器100、isp 200和/或处理电路300生成或处理的数据的存储装置。在示例实施例中,存储器400可包括作为非易失性存储器的电可擦除可编程只读存储器(eeprom)、闪速存储器、相变随机存取存储器(pram)、电阻随机存取存储器(rram)、纳米浮栅存储器(nfgm)、聚合物随机存取存储器(poram)、磁随机存取存储器(mram)、铁电随机存取存储器(fram)等。

58.根据本发明构思的示例实施例,存储器400可存储照度数据ydat。照度数据ydat由isp 200生成,作为符合yuv格式的图像数据的一部分。照度数据ydat和色度数据udat和vdat可分离地存储在存储器400内的逻辑地或物理地分离的空间中。根据示例实施例,处理

电路300可仅使用yuv格式的图像数据中的照度数据ydat。

59.第一总线bus1可在图像传感器100、isp 200、处理电路300和存储器400之间中继数据通信。在示例实施例中,第一总线bus 1可通过使用诸如地址总线、控制总线或数据总线的总线类型来中继图像传感器100、isp 200、处理电路300和存储器400之间的控制信号、数据和地址的发送和接收。

60.如图1所示的包括图像传感器100、isp 200、处理电路300、存储器400和第一总线bus1的电子装置10可实现为片上系统(soc)。soc是包括用于驱动具有单个芯片(或单个封装件的芯片部件的组或堆叠)的电子装置10所需的硬件模块的半导体芯片。在示例实施例中,可通过将执行多个硬件模块中的每一个的功能所需的应用与内部软件组合来安装soc。应用(或程序)可以是执行特定目的的应用软件。根据示例实施例,可通过使用至少一个功能来执行应用。可通过执行源代码来构建应用。通过使用soc,与分别生产各种功能元件相比,可减小每个元件安装在基板上的空间,使得产品小型化成为可能,并且可降低制造成本。

61.根据本发明构思的示例实施例的处理电路300可通过仅利用yuv数据中的照度数据ydat训练人工神经网络来降低存储器使用和功耗。

62.此外,因为根据本发明构思的示例实施例的处理电路300不需要将已经转换为yuv格式的数据转换回rgb格式,所以可提高数据处理速度。

63.此外,根据本发明构思的示例实施例的处理电路300可通过使用照度数据ydat来改善即使在低照度环境中的深度估计的精度。

64.此外,因为根据本发明构思的示例实施例的处理电路300即使对于具有小视差的图像数据也可考虑相对深度来估计深度,所以可改善深度估计的精度。

65.图2是示出根据本发明构思的示例实施例的生成深度信息的方法的流程图。生成深度信息的方法可由处理电路300(图1)或包括处理电路300的电子装置10(图1)执行。将一起参照图1与图2。

66.在操作s110中,可获取符合yuv格式的照度数据ydat(图1)。例如,处理电路300可获取存储在存储器400(图1)中的照度数据ydat。照度数据ydat可被理解为以yuv格式表示的图像数据中的照度通道中包括的数据。

67.在操作s120中,可通过使用第一人工神经网络将双像素特征学习应用于照度数据ydat来生成绝对深度数据。例如,通过将获取的照度数据ydat输入dfe 310,处理电路300可估计作为对由双像素感测的图像数据进行处理的结果的绝对深度,从而生成绝对深度数据。由双像素感测的图像数据可具有视差。双像素是指共享一个微透镜的两个光电转换元件,并且与指的是彼此不同的相机模块的双相机相比,双像素可具有小的视差。因此,由于双像素而导致的特征可不同于由于双相机而导致的特征。

68.在操作s130,可通过使用第二人工神经网络将场景学习应用于绝对深度数据来生成相对深度数据。例如,从dfe 310输出的绝对深度数据可被提供至s.net模块330,并且s.net模块330可根据由与第二人工神经网络对应的场景网络s.net进行的处理来估计相对深度,从而生成相对深度数据。

69.在操作s140,可通过使用第三人工神经网络生成绝对深度数据和相对深度数据的最终深度数据。例如,从s.net模块330输出的相对深度数据可被提供至d.net模块350,并且

d.net模块350可根据由与第三人工神经网络对应的视差网络d.net进行的处理来生成最终深度数据。

70.在操作s150中,可生成深度信息。可生成作为由包括卷积层、批次归一化(batch normal ization)层和激活层的后处理层对最终深度数据进行处理的结果的深度信息。

71.图3是具体示出isp 200的框图。

72.参照图3,isp 200可包括dphy 210、isp接口(isp i/f)230、图像前端引擎(ife)250和图像处理引擎(ipe)270。

73.作为图像传感器100和显示器之间的接口的物理层的dphy 210是由移动工业处理器接口(mipi)联盟建立的标准化接口。dphy 210可将图像数据idat发送到isp 200。图像数据idat可从图像传感器100被提供给isp 200。在这种情况下,isp 200可被称为相机子系统,并且具体地,可符合由mipi联盟定义的相机串行接口-2(mipi-csi-2)。

74.isp i/f 230可路由来自多个相机串行接口(csi)解码器的数据流。isp i/f 230可将通过dphy 210提供的原始数据rdat路由至ife 250。

75.ife 250可包括被配置为接收原始数据rdat并输出预yuv数据pyuv的硬件、固件和软件。根据示例实施例,ife 250可执行图像处理操作,诸如收集自动曝光(ae)噪声、自动聚焦(af)噪声和自动白平衡(awb)噪声的统计信息。此外,ife 250可执行各种图像处理操作,诸如缺陷像素校正、偏移校正、透镜失真校正、颜色增益校正、绿色不平衡校正等。

76.ipe 270可包括cpu、微处理器或微控制器单元(mcu)。ipe 270可执行针对输入数据的图像后处理。后处理可指基于感测的图像数据用于减少误差和失真的一系列后续处理任务。由ipe 270执行的后处理可指针对图像伪影的图像增强算法的应用。

77.在示例实施例中,由ipe 270处理的数据可存储在存储器400中。例如,照度数据ydat和色度数据片段udat和vdat可存储在存储器400中,其中照度数据ydat和色度数据片段udat和vdat中的每一个都具有相对于预yuv数据pyuv改变的数据格式。此外,根据图像处理生成的图像处理后的帧(在下文中,被称为转换后的图像数据)和/或结果数据(统计数据、直方图等)可存储在存储器400中。

78.图4a和图ab是示出图像数据的rgb格式和yuv格式之间的转换关系的示图。将一起参照图1与图4a和图4b。

79.参照图4a,颜色像素cp可包括红色通道、绿色通道和蓝色通道rgb 3ch。isp 200可通过颜色空间转换将红色通道、绿色通道和蓝色通道rgb 3ch转换为y通道、u通道和v通道yuv 3ch。在此,照度数据ydat是与表示照度信号的通道对应的数据。u通道是表示照度信号和蓝色分量之间的差的通道,并且也被称为蓝色色度cb通道。v通道是表示照度信号和红色分量之间的差的通道,并且也被称为红色色度cr通道。电子装置10可将照度数据ydat输入到人工神经网络,照度数据ydat是转换后的y通道、u通道和v通道yuv 3ch当中的y通道的数据。

80.参照图4b,描述了rgb颜色空间和yuv颜色空间之间的转换关系。

81.在rgb颜色空间中,红色r、蓝色b和绿色g构成维度,并且其原点是黑色bk。当以8位表示数据时,红色可表示为(255,0,0),蓝色可表示为(0,0,255),绿色可表示为(0,255,0)。在这种情况下,黄色可表示为(255,255,0),品红色可表示为(255,0,255),青色可表示为(0,255,255)。

82.rgb颜色空间可通过以下等式被转换成yuv颜色空间。

83.[等式1]

[0084]

y=(0.257

×

r)+(0.504

×

g)+(0.098

×

b)+16

[0085]

[等式2]

[0086]

u=-(0.148

×

r)-(0.291

×

g)+(0.439

×

b)+128

[0087]

[等式3]

[0088]

v=(0.439

×

r)-(0.368

×

g)-(0.071

×

b)+128

[0089]

当通过等式1至等式3将rgb颜色空间转换为yuv颜色空间时,rgb颜色空间中的红色、蓝色、绿色、黄色、品红色、青色和白色的位置关系改变。

[0090]

在yuv颜色空间中,照度y、蓝色色度cb(即,u通道)和红色色度cr(即,v通道)构成维度。当数据以8位表示时,rgb颜色空间的红、蓝、绿、黄、品红、青、白和黑可表示为八面体的边,但可不标准化为特定的位置。例如,白色是照度y为255、蓝色色度cb和红色色度cr均为128的颜色。

[0091]

图5a到图5d是示出符合yuv格式的图像数据idat的数据结构的示图。yuv格式的图像数据idat可存储为具有针对每个像素分离的其照度分量luma及其色度分量chroma,以显示彩色图像。yuv格式也称为ycbcr格式。在图5a至图5d中,为了便于说明,将以ycbcr格式为例描述数据结构。

[0092]

参照图5a,示出了具有4:4:4的ycbcr采样比的数据结构。ycbcr4:4:4是指cr和cb与y的比率等于4:4:4。当在垂直方向上从照度分量luma读取数据结构时,当在一行中为照度分量luma提供四个数据空间的同时,在色度分量chroma中,为蓝色色度cb提供四个数据空间,并且为红色色度cr提供四个数据空间。

[0093]

参照图5b,示出了具有4:2:2的ycbcr采样比的数据结构。当在垂直方向上从照度分量luma读取数据结构时,当在一行中为照度分量luma提供四个数据空间的同时,在色度分量chroma中,为蓝色色度cb提供两个数据空间,并且为红色色度cr提供两个数据空间。因此,ycbcr 4:2:2是指cr和cb与y的比率为2:2:4。

[0094]

参照图5c,示出了具有4:1:1的ycbcr采样比的数据结构。当在垂直方向上从照度分量luma读取数据结构时,当在一行中为照度分量luma提供四个数据空间的同时,在色度分量chroma中,为蓝色色度cb提供一个数据空间,并且为红色色度cr提供一个数据空间。因此,ycbcr 4:1:1是指cr和cb与y的比率为1:1:4。

[0095]

参见图5d,示出了具有4:2:0的ycbcr采样比的数据结构。当在垂直方向上从照度分量luma读取数据结构时,当在一行中为照度分量luma提供四个数据空间的同时,在色度分量chroma中,为蓝色色度cb提供两个数据空间,或者为红色色度cr提供两个数据空间。因此,ycbcr 4:2:0可指cr(或cb)和cb(或cr)与y的比率为2:0:4。

[0096]

根据本发明构思的示例实施例,isp 230(图3)可针对图像数据idat生成符合ycbcr 4:2:0的格式的yuv数据。ycbcr 4:2:0可对于便携式电子装置中的数据处理、存储及/或显示是高效的。然而,图像数据idat不限于此,并且可具有如上所述的各种ycbcr数据结构中的一种。

[0097]

图6a至图6c是示出根据本发明构思的示例实施例的处理电路300a和300b以及第一处理电路301c和第二处理电路302c的框图。

[0098]

参照图6a,处理电路300a可通过处理照度数据ydata来生成深度信息ideptha。根据示例实施例,处理电路300a可包括dfe 310a、d.net模块350a和后处理层370a。

[0099]

可通过将照度数据ydata输入到dfe 310a来估计照度数据ydata的绝对深度,并且作为结果,可生成绝对深度数据ada。d.net模块350a支持的视差网络d.net可包括激活层和多个卷积层,激活层包括至少一个relu函数,并且d.net模块350a支持的视差网络d.net可通过处理绝对深度数据ada生成最终深度数据fda。后处理层370a可将最终深度数据fda处理成深度信息ideptha。

[0100]

根据本发明构思的示例实施例,通过仅使用照度数据ydata,处理电路300a可生成对低照度环境比符合rgb格式的图像数据更鲁棒的深度信息。

[0101]

此外,根据本发明构思的示例实施例,通过仅利用yuv数据(例如,图3的照度数据ydat以及色度数据片段udat和vdat)中的照度数据ydata训练人工神经网络,处理电路300a可降低存储器使用和功耗。此外,因为根据本发明构思的示例实施例的处理电路300a不需要将已经转换为yuv格式的数据转换回rgb格式,所以可提高数据处理速度。

[0102]

参照图6b,处理电路300b可通过处理照度数据ydatb来生成深度信息idepthb。根据示例实施例,处理电路300b可包括dfe 310b、s.net模块330b、d.net模块350b和后处理层370b。

[0103]

可通过将照度数据ydatb输入到dfe 310b来估计照度数据ydatb的绝对深度,并且作为结果,可生成绝对深度数据adb。s.net模块330b可通过使用场景网络s.net来估计绝对深度数据adb的相对深度。可输出绝对深度数据adb的相对深度估计结果作为相对深度数据cdb。d.net模块350b支持的视差网络d.net可通过将绝对深度数据adb与相对深度数据cdb融合来生成最终深度数据fdb。后处理层370b可将最终深度数据fdb处理成深度信息idepthb。

[0104]

因为根据本发明构思的示例实施例的处理电路300b即使对于具有小视差的数据(例如,照度数据ydatb)也可考虑相对深度来估计深度,所以可提高深度估计的精度。

[0105]

参照图6c,第一处理电路301c可通过处理照度数据ydatc来生成深度信息idepthc。根据示例实施例,第一处理电路301c可包括dfe 310c、d.net模块350c和后处理层370c,并且第二处理电路302c可包括s.net模块330c。

[0106]

可通过将照度数据ydatc输入到dfe 310c来估计照度数据ydatc的绝对深度,并且作为结果,可生成绝对深度数据adc。可将绝对深度数据adc提供至s.net模块330c和d.net模块350c。

[0107]

第二处理电路302c的s.net模块330c可通过使用场景网络s.net来估计绝对深度数据adc的相对深度。可将绝对深度数据adc的相对深度估计结果作为相对深度数据cdc输出到第一处理电路301c。d.net模块350c支持的视差网络d.net可通过将绝对深度数据adc与从第二处理电路302c接收的相对深度数据cdc融合来生成最终深度数据fdc。后处理层370c可将最终深度数据fdc处理成深度信息idepthc。

[0108]

因为人工神经网络的一部分在另一处理电路(例如,第二处理电路302c)中被处理,所以根据本发明构思的示例实施例的第一处理电路301c可促进数据的分布式处理,并且可实现具有大数据量或需要长数据处理时间的任务的分布式和/或并行处理。

[0109]

图7a至图7c是示出人工神经网络nn1、nn2和nn3的结构和操作的示图。

[0110]

参照图7a,人工神经网络nn1可以是cnn,但不限于此。尽管为了便于解释,图7a示出人工神经网络nn1包括两个隐藏层,但人工神经网络nn1不限于此,并可包括各种数量的隐藏层。此外,尽管图7a示出人工神经网络nn1包括用于接收输入数据的单独输入层,但在一些实施例中,输入数据可直接输入到隐藏层。

[0111]

在人工神经网络nn1中,除了输出层之外的层的节点可通过用于发送输出信号的链路连接到下一层的节点。通过这些链路,通过将包括在前一层中的节点的节点值乘以分配给每个链路的权重而获取的值可被输入到包括在当前层中的节点。前一层的节点值可对应于轴突值,并且权重可对应于突触权重。权重可被称为人工神经网络nn1的参数。

[0112]

可应用激活函数来将特征映射的值转换成关于特征是否存在的非线性信息。例如,激活函数可包括s形函数、双曲正切(tanh)函数、relu函数等,并且非线性可通过激活函数在人工神经网络nn1中实现。

[0113]

包括在人工神经网络nn1中的任何一个节点的输出可由以下等式4表示。

[0114]

[等式4]

[0115][0116]

等式4可表示第i个节点的相对于层中的m个输入值的输出值yi。xj可表示前一层的第j个节点的输出值,w

j,i

可表示施加到前一层的第j个节点和当前层的第i个节点之间的连接部分的权重。f()可表示激活函数。如等式4所示,在激活函数中,可使用将输入值xj乘以权重w

j,i

的累积结果。换句话说,在每个节点处,可执行将输入值xj乘以权重w

j,i

并累加其结果的运算,例如乘法-累加(mac)运算。除了这种用途之外,还可存在需要mac运算的各种应用,并且可使用能够在模拟电路区域中处理mac运算的处理装置。

[0117]

参照图7b,人工神经网络nn2可包括多个层,即,第1层l1至第n层ln。第一层l1至第n层ln中的每一个可以是线性层或非线性层。在实施例中,至少一个线性层和至少一个非线性层可彼此组合并且被称为一个层。例如,线性层可包括卷积层和全连接层,并且非线性层可包括池化层和激活层。

[0118]

例如,第一层l1可以是卷积层,第二层l2可以是池化层,并且作为输出层的第n层ln可以是全连接层。人工神经网络nn2还可包括激活层或执行另一类型运算的层。

[0119]

第一层l1至第n层ln中的每一个可接收输入数据(例如,图像帧)或由前一层生成的特征映射作为输入特征映射,并且可通过对输入特征映射进行运算来生成输出特征映射或识别信号rec。在这种情况下,特征映射是指其中表达了输入数据的各种特征的数据。第1特征映射至第n特征映射fm1、fm2、fm3、...和fmn可具有例如二维矩阵形式或三维矩阵(或张量)形式。第1特征映射至第n特征映射fm1、fm2、fm3、...和fmn可具有宽度w(或列)、高度h(或行)和深度d,其可分别对应于坐标上的x轴、y轴和z轴。在这种情况下,深度d可被称为通道的数量。

[0120]

第一层l1可通过将第一特征映射fm1与权重映射wm卷积来生成第二特征映射fm2。权重映射wm可对第一特征映射fm1进行滤波,并且可被称为滤波器或内核。权重映射wm的深度(即,通道的数量)等于第一特征映射fm1的深度(即,通道的数量),并且权重映射wm和第

一特征映射fm1的相同通道可彼此卷积。可通过使用第一特征映射fm1作为滑动窗口的遍历方法来移位权重映射wm。移位量可被称为“步幅长度”或“步幅”。在每次移位期间,包括在权重映射wm中的每个权重值可与包括在权重映射wm中的每个权重值与第一特征映射fm1重叠的区域中的所有单元数据片段相乘并相加。第一特征映射fm1的在包括在权重映射wm中的每个权重值与第一特征映射fm1重叠的区域中的数据片段可被称为提取数据。当第一特征映射fm1与权重映射wm卷积时,可生成第二特征映射fm2的一个通道。尽管在图7b中示出了一个权重映射wm,但多个权重映射可基本上与第一特征映射fm1卷积,以生成第二特征映射fm2的多个通道。例如,第二特征映射fm2的通道的数量可对应于权重映射的数量。

[0121]

第二层l2可通过经由池化改变第二特征映射fm2的空间大小来生成第三特征映射fm3。池化可被称为采样或下采样。可以以池化窗口pw的大小为单位在第二特征映射fm2上移位二维池化窗口pw,并且可选择第二特征映射fm2与池化窗口pw重叠的区域中的单元数据片段的最大值(或平均值)。因此,可根据第二特征映射fm2生成具有改变的空间大小的第三特征映射fm3。第三特征映射fm3的通道的数量等于第二特征映射fm2的通道的数量。

[0122]

第n层ln可通过将第n特征映射fmn的特征组合来将输入数据的类别cl分类。此外,第n层ln可生成与类别cl对应的识别信号rec。在实施例中,输入数据可对应于包括在视频流中的帧数据,并且第n层ln可基于从前一层提供的第n特征映射fmn提取与包括在由帧数据表达的图像中的对象对应的类别cl,从而识别对象,并生成与识别的对象对应的识别信号rec。

[0123]

参照图7c,输入特征映射可包括d个通道,并且每个通道的输入特征映射可具有h行乘w列的大小(其中,d、h和w是自然数)。每个内核可具有r行乘s列的大小,并且内核可包括与输入特征映射的通道数量(或深度)相对应的数量的通道(其中,r和s是自然数)。输出特征映射可通过输入特征映射和内核之间的三维卷积运算来生成,并且根据卷积运算可包括y个通道。

[0124]

图8是示出根据本发明构思的示例实施例的dfe 310的结构的框图。

[0125]

参照图8,dfe 310可包括多个级,并且一个级可由一对卷积层conv和激活层actv构成。激活层actv是非线性层,s形函数、双曲正切函数和relu函数中的至少一个被应用于该非线性层以将特征的存在转换成非线性信息。

[0126]

根据本发明构思的示例实施例,dfe 310可从存储器400接收照度数据ydat,并可将照度数据ydat输入到第一级的卷积层conv以细化和处理数据。dfe 310可生成绝对深度数据ad作为结果。可将绝对深度数据ad提供给s.net模块330或d.net模块350。

[0127]

图9是示出根据本发明构思的示例实施例的s.net模块330的结构的框图。

[0128]

参照图9,在s.net模块330中使用的场景网络s.net可包括编码层单元lua和解码层单元lub。场景网络s.net可接收绝对深度数据ad,并且可由编码层单元lua、解码层单元lub计算绝对深度数据ad的特征值。

[0129]

场景网络s.net可包括多个编码器(编码层单元)和多个解码器(解码层单元),并且多个编码器和多个解码器可以以对称金字塔结构来实现。例如,多个编码器可串联连接以逐渐降低编码数据的分辨率,并且多个解码器可串联连接以逐渐增加解码数据的分辨率。

[0130]

编码层单元lua可接收从前一编码层单元输出的特征映射,并可执行分配给每个

编码层单元(例如lua1)的运算。例如,第一编码层单元lua1可接收特征映射fma0,并通过包括在第一编码层单元lua1中的各种层执行运算。例如,编码层单元lua可包括卷积层、采样层和激活层。卷积层可执行卷积运算。采样层可执行下采样、上采样、平均池化或最大池化运算。激活层可通过relu函数或s形函数执行运算。第一编码层单元lua1可基于运算的结果输出特征映射fma1。

[0131]

由第一编码层单元lua1输出的特征映射fma1可具有比输入特征映射fma0小的宽度和高度,并且可具有大的深度。例如,第一编码层单元lua1可控制特征映射fma1的宽度、高度和深度。例如,可控制深度以便不过度大。第一编码层单元lua1可具有用于设置特征映射fma1的深度的参数。同时,第一编码层单元lua1可包括下采样层ds。下采样层ds可从包括在输入特征映射fma0中的特征值中选择预定特征值,并将其输出为特征映射fma1的特征值。例如,下采样层ds可控制特征映射fma1的宽度和高度。第二编码层单元lua2和第三编码层单元lua3可与第一编码层单元lua1类似地处理运算。例如,第二编码层单元lua2和第三编码层单元lua3可从前一编码层单元接收特征映射,通过包括在当前层单元中的多个层来处理运算,并将包括运算的结果的特征映射输出到下一编码层单元。

[0132]

编码层单元lua可将运算的结果输出至下一编码层单元lua或同一级的解码层单元lub。每个编码层单元lua可固定地连接到下一编码层单元lua,并可经由多个跳过连接(例如,第一跳过连接sk1至第三跳过连接sk3)连接到同一级的解码层单元lub。尽管在图9中仅示出了第一跳过连接至第三跳过连接,但是本发明构思不限于此。例如,表述“同一级”可指从输入层il开始的顺序等于从输出层ol开始的顺序的情况。同一级的层单元可以是例如第一编码层单元lua1和第一解码层单元lub1。

[0133]

根据示例实施例,可由处理电路300或电子装置10选择第一跳过连接sk1至第三跳过连接sk3中的至少一些。例如,处理电路300可接收关于跳过级的信息。当设置人工神经网络模型的跳过级时,可激活与预设的跳过级对应的第一跳过连接sk1至第三跳过连接sk3。例如,当人工神经网络模型的跳过级为2时,可激活第二跳过连接sk2。编码层单元lua可经由激活的跳过连接将特征映射输出到解码层单元lub。未激活的跳过连接(例如,sk1和sk3)可不传播特征映射。

[0134]

根据本发明构思的示例实施例,同一级的层单元(例如,lua1和lub1)可处理基本相同大小的特征映射。例如,由第一编码层单元lua1接收的特征映射fma0的大小和由第一解码层单元lub1输出的特征映射fmb0的大小可基本相同。例如,特征映射的大小可包括宽度、高度和深度中的至少一个。此外,由第一编码层单元lua1输出的特征映射fma1的大小和由第一解码层单元lub1接收的特征映射fmb1的大小可基本相同。

[0135]

根据本发明构思的示例实施例,同一级的编码层单元lua和解码层单元lub可具有基本相同的采样大小。例如,第一编码层单元lua1的下采样大小和第一解码层单元lub1的上采样大小可基本上相同。

[0136]

解码层单元lub可从前一解码层单元lub接收特征映射,或者从同一级的编码层单元lua接收特征映射。解码层单元lub可通过使用接收到的特征映射来处理运算。例如,解码层单元lub可包括卷积层、采样层和激活层。

[0137]

由第一编码层单元lua1输出的特征映射fma1可具有比输入特征映射fma0小的宽度和高度,并且可具有大的深度。例如,第一编码层单元lua1可控制特征映射fma1的宽度、

高度和深度。例如,可控制深度以便不过度大。第一编码层单元lua1可具有用于设置特征映射fma1的深度的参数。

[0138]

上采样层us可调整输入特征映射的大小。例如,上采样层us可调整特征映射的宽度和高度。上采样层us可通过使用输入特征映射的每个特征值和与每个特征值相邻的特征值来执行上采样操作。例如,上采样层us可以是通过使用最近邻方法将相同的特征值写入输出特征映射的层。作为另一示例,上采样层us可以是转置卷积层,并且可通过使用预定的权重映射来对图像进行上采样。

[0139]

通过上采样已经返回到先前分辨率的数据可经由卷积层conv、批次归一化层bn和激活层actv被转换成相对深度数据cd。

[0140]

图10是示出根据本发明构思的示例实施例的d.net模块350的结构的框图。

[0141]

参照图10,d.net模块350可包括多个级,并且一个级可由一对卷积层conv和激活层actv构成。

[0142]

根据本发明构思的示例实施例,d.net模块350可从dfe 310接收绝对深度数据ad,并且/或者可从s.net模块330接收相对深度数据cd。

[0143]

绝对深度数据ad或与绝对深度数据ad融合的相对深度数据cd可被输入到第一级的卷积层conv。d.net模块350可生成最终深度数据fd作为结果。最终深度数据fd可被发送到后处理层370。

[0144]

图11是示出根据本发明构思的示例实施例的后处理层370的结构的框图。

[0145]

根据示例实施例,后处理层370可包括卷积层conv、批次归一化层bn和激活层actv。后处理层370可例如通过使用卷积层conv、批次归一化层bn和激活层actv执行已知类型的卷积、批次归一化和激活功能,将最终深度数据fd转换成深度信息idepth。

[0146]

图12a至图12c是示出根据本发明构思的示例实施例的图像数据的深度估计结果的示图。

[0147]

参照图12a,第一图像img1可包括对象(兔子)和背景。第一图像img1可对应于图像数据idat。作为第一图像img1的背景,山丘可被理解为其中图像的密度稀疏并且边界或边缘中的突然改变的发生小的无纹理区域。

[0148]

参照图12b,第二图像img2包括对象(兔子)和背景,并且表示与深度信息ideptha对应的深度图。深度图可以是包含从图像传感器或观察点到对象的表面的距离和与该距离相关的信息的图像,或者是图像的通道,并且从用户的视点(或图像传感器)到屏幕上包含的对象的表面的距离可被识别为深度信息ideptha。

[0149]

第二图像img2可以以阴影显示深度信息ideptha。较亮(或更接近白色)的部分可被定义为具有较小深度值的部分,较暗(或更接近黑色)的部分可被定义为具有较大深度值的部分。

[0150]

深度信息ideptha由图6a的dfe 310a、d.net模块350a和后处理层370a生成。根据本发明构思的示例实施例,处理电路300a可通过仅将对低照度鲁棒的照度数据ydata应用于估计绝对深度的人工神经网络来实现对象(兔子)和背景之间的区分。

[0151]

参照图12c,第三图像img3包括对象(兔子)和背景,并且表示与深度信息idepthb相对应的深度图。

[0152]

深度信息idepthb由图6b的dfe 310b、s.net模块330b、d.net模块350b和后处理层

370b生成。根据本发明构思的示例实施例,处理电路300b可额外地通过使用s.net模块330b将相对深度数据与绝对深度数据融合,并且因此,即使对于具有相对小的视差的数据,也可实现对象(兔子)和背景之间的清楚区分。例如,第三图像img3的无纹理区域是在第二图像img2中还未被观察到的区域,并且可证明深度图已得到改善。

[0153]

图13a至图13d是示出根据本发明构思的示例实施例的像素的结构的示图。

[0154]

参照图13a,像素phda可包括微透镜、光电转换元件和滤色器。例如,多个像素px1和px2中的每一个可包括作为光电转换元件的实施例的光电二极管pd1和pd2,和滤色器cf1和cf2,并且可在滤色器cf1和cf2上设置微透镜ml1和ml2。根据示例实施例,微透镜ml1和ml2的竖直截面形状可以是具有圆形或椭圆的一部分的曲率的弧。

[0155]

根据图13a所示的实施例,一个滤色器cf1或cf2以及一个微透镜ml1或ml2可分别设置在一个光电二极管pd1或pd2上。例如,入射到微透镜ml1的中心的光可穿过滤色器cf1,使得仅特定波长带(例如,对应于绿色的约500纳米(nm)至约600nm)的光可透射,并且特定波长带的透射光可在光电二极管pd1上成像。类似地,入射到微透镜ml2的中心的光可穿过滤色器cf2,使得仅特定波长的光可透射,并且特定波长的透射光可在光电二极管pd2上成像。如图13a所示,当入射在一个微透镜ml1或ml2上的光在一个光电二极管pd1或pd2上成像时,光电二极管可被称为单个光电二极管(单个pd)。图像传感器100(图1)可通过使用像素phda根据光电二极管pd1与pd2之间的相位差计算视差,进而确定到对象的距离。

[0156]

参照图13b,双像素phdb可包括微透镜、光电转换元件和滤色器。例如,像素pxx可包括两个滤色器cfa和cfb以及分别对应于滤色器cfa和cfb的两个光电二极管pda和pdb。类似地,像素pxy可包括两个滤色器cfc和cfd及分别对应于滤色器cfc和cfd的两个光电二极管pdc和pdd。

[0157]

根据图13b所示的实施例,两个滤色器cfa和cfb以及两个光电二极管pda和pdb可分别设置在一个微透镜mlx下方。例如,作为入射到微透镜mlx的中心的光的一部分的第一光通量lfx可穿过滤色器cfa以在光电二极管pda上成像。作为入射到微透镜mlx的中心的光的其余部分的第二光通量lfy可穿过滤色器cfb以在光电二极管pdb上成像。在像素pxy中也可发生与像素pxx的现象类似的现象。如图13b所示,当入射到一个微透镜mlx或mly的光在两个光电二极管pda和pdb(或pdc和pdd)上成像时,光电二极管可被称为双光电二极管(双pd)或双像素。

[0158]

图13c是图13b的双像素phdb的平面图。参照图13c,像素pxx可包括微透镜mlx和两个子像素,例如,第一子像素spxa与第二子像素spxb。第一子像素spxa和第二子像素spxb可在行方向(例如,x轴方向(第一方向))上并排布置。例如,第一子像素spxa可布置在像素pxx的左侧,而第二子像素spxb可布置在像素pxx的右侧。第一子像素spxa和第二子像素spxb可分别包括第一光电二极管pda和第二光电二极管pdb。

[0159]

根据示例实施例,可由第一光电二极管pda和第二光电二极管pdb生成感测信号。例如,分别地,可由第一子像素spxa输出第一图像信号,可由第二子像素spxb输出第二图像信号,并且可基于第一图像信号和第二图像信号计算根据相位差运算的视差。

[0160]

图13d示出了根据图13c的线a-a'的竖直截面图。

[0161]

参照图13d,像素pxx可包括在z轴方向(例如,第三方向)上层叠的第一层l1和第二层l2。第一层l1可被称为光电转换层,并且可包括形成在基板sub上的滤色器cf、微透镜

mlx、以及形成在基板sub中的两个光电转换元件(例如,第一光电二极管pda和第二光电二极管pdb)。第二层l2可被称为布线层,并且多个布线ws可形成在第二层l2中。

[0162]

基板sub可以是硅晶片、绝缘体上硅(soi)基板或半导体外延层。基板sub可包括彼此相对的第一表面sf和第二表面sb。例如,第一表面sf可以是基板sub的前表面,而第二表面sb可以是基板sub的后表面。光可入射到第二表面sb。

[0163]

从基板sub的第二表面sb朝向第一表面sf延伸的多个像素分离层(例如,第一像素分离层sep1和第二像素分离层sep2(例如,深沟槽隔离(dti)或p型离子注入区域))可形成在基板sub上,其中形成有像素pxx的像素区域apx可被多个像素分离层sep1和sep2中的多个相对长的第一像素分离层sep1分离,并且像素区域apx可被相对短的第二像素分离层sep2划分成其中形成有第一子像素spxa和第二子像素spxb的第一区域a1和第二区域a2。在示例实施例中,第一区域a1和第二区域a2中的每一个可掺杂有第一导电类型(例如,p型)的杂质。第一光电二极管pda和第二光电二极管pdb可分别形成在第一区域a1和第二区域a2中。例如,掺杂有第二导电类型(例如,n型)的杂质的阱区可形成为第一光电二极管pda和第二光电二极管pdb。

[0164]

如图所示,第一光电二极管pda和第二光电二极管pdb可相对于微透镜mlx的光轴mlx在第一方向(例如,x方向)或第二方向(例如,y方向)上并排布置。

[0165]

浮动扩散节点fd可形成在第一光电二极管pda与第二光电二极管pdb之间。在实施例中,晶体管可形成在第一光电二极管pda和第二光电二极管pdb与第一表面sf之间,并且信号可通过布线层l2的多个布线ws发送到晶体管并由晶体管接收。

[0166]

图14是示出根据本发明构思的示例实施例的电子系统1的框图。

[0167]

参照图14,图14的soc 1000可以是图1的电子装置10的应用。因此,图14的soc 1000可设计为支持图1的电子装置10。图14中所示的soc 1000可对应于图1中所示的电子装置10。soc 1000可控制至少一个组件的操作。

[0168]

电子系统1可实现为pc、数据服务器或便携式电子装置。便携式电子装置可实现为例如膝上型计算机、移动电话、智能电话、平板pc、pda、企业数字助理(eda)、数字静态相机、数字摄像机、pmp、个人导航装置或便携式导航装置(pnd)、手持式游戏控制台或电子书。

[0169]

电子系统1可包括soc 1000、相机模块1100、显示器1200、电源1300、输入/输出(i/o)端口1400、存储器1500、存储部1600、外部存储器1700和网络装置1800。

[0170]

相机模块1100是指能够将光学图像转换为电子图像的模块。因此,从相机模块1100输出的电子图像可存储在存储部1600、存储器1500或外部存储器1700中。此外,可通过显示器1200显示从相机模块1100输出的电子图像。相机模块1100可包括图1的图像传感器100或图像传感器100和isp 200。

[0171]

显示器1200可显示从存储部1600、存储器1500、i/o端口1400、外部存储器1700或网络装置1800输出的数据。电源1300可向至少一个组件提供操作电压。i/o端口1400是指能够将数据发送到电子系统1或将从电子系统1输出的数据发送到外部装置的端口。例如,i/o端口1400可以是用于连接到诸如计算机鼠标的指示装置的端口、用于连接到打印机的端口、或用于连接到usb驱动器的端口。

[0172]

存储器1500可实现为易失性存储器或非易失性存储器。根据实施例,能够控制针对存储器1500的数据访问操作(例如,读取操作、写入操作(或编程操作)、或擦除操作)的存

储器控制器可集成或嵌入在soc 1000中。根据另一实施例,存储器控制器可实施在soc 1000与存储器1500之间。

[0173]

存储部1600可实现为硬盘驱动器或固态驱动器(ssd)。

[0174]

外部存储器1700可实现为安全数字(sd)卡或多媒体卡(mmc)。根据实施例,外部存储器1700可以是用户识别模块(sim)卡或通用用户识别模块(usim)卡。

[0175]

网络装置1800是指用于将电子系统1连接到有线网络或无线网络的装置。

[0176]

图15是示出了图14的soc 1000的示例实施例的框图。

[0177]

参照图15,soc 1000可包括主处理器1010、随机存取存储器/只读存储器(ram/rom)1020、调制解调器1030、isp 1040、(包括npu 1051、gpu 1053和dsp 1055的)加速器模块1050、非易失性存储器接口(nvm i/f)1060、相机接口(i/f)1070、存储器接口(i/f)1080和显示器接口(i/f)1090。soc 1000的组件(即,主处理器1010、rom/ram 1020、调制解调器1030、isp 1040、非易失性存储器接口1060、相机接口1070、存储器接口1080和显示器接口1090)可通过第二总线bus2发送和接收数据。

[0178]

主处理器1010可控制soc 1000的整体操作。主处理器1010可实现为例如cpu、微处理器、arm处理器、x86处理器、mips处理器等。在一些实施例中,主处理器1010可实现为具有两个或更多个独立处理器(或核)的一个计算组件,即多核处理器。主处理器1010可处理或执行存储在rom/ram 1020中的命令代码(例如,指令)和/或数据。

[0179]

ram/rom 1020可临时地存储程序、数据和/或指令。根据实施例,ram/rom 1020可实现为dram或sram。ram/rom 1020可通过接口1060、1070、1080和1090输入和输出,或者可临时地存储由isp 1040进行过图像处理的数据。

[0180]

非易失性存储器接口1060可对接(interface)从非易失性存储器(nvm)装置1160输入的数据或输出到非易失性存储器的数据。非易失性存储装置1160可实现为例如存储卡(mmc、嵌入式mmc(emmc)、sd卡、微sd卡等)。

[0181]

相机接口1070可对接从位于soc 1000外部的相机1170输入的图像数据(例如,原始图像数据)。相机1170可生成通过使用多个光电转换元件拍摄的图像的数据。通过相机接口1070接收的图像数据可被提供给isp 1040或通过存储器接口1080存储在存储器1180中。

[0182]

存储器接口1080可对接从存储器1180输入的数据或向存储器1180输出的数据。根据实施例,存储器1180可实现为诸如dram或sram的易失性存储器,或者实现为诸如rram、pram或nand闪存的非易失性存储器。

[0183]

显示接口1090可对接输出到显示装置1190的数据(例如,图像数据)。显示装置1190可通过诸如液晶显示器(lcd)、有源矩阵有机发光二极管(amoled)等的显示器输出根据图像数据的图像信号。

[0184]

isp 1040可通过对由相机1170提供的图像数据执行图像处理来生成转换后的图像数据,并可将转换后的图像数据存储在存储器1180中,或者可按比例缩放转换后的图像数据并将按比例缩放的图像提供给显示装置1190。此外,soc 1000还可包括安全装置1100,安全装置1100包括安全方法、协议以及加密和解密密钥。

[0185]

尽管已经参照本发明构思的实施例具体示出和描述了本发明构思,但将理解,在不脱离所附权利要求的精神和范围的情况下,可在形式和细节上对其进行各种改变。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1